Adunarea si scaderea fara rotunjiri in virgula flotanta

Preconizam o prezentare graduala a

problematicii operatiilor de adunare si scadere in virgula

flotanta, neabordand, pentru inceput, aspecte legate de despachetarea

operanzilor/impachetarea rezultatului dintr-un/intr-un format standard, dar, in

special, de rotunjire. Astfel vom accepta o structura de tipul celei

reprezentate in fig. 5.3, la care consideram ca operanzii sosesc in

forma despachetata (cu hidden bit explicit), adica dimensiunea

magistralei este de (![]() ) biti, anume e

pentru exponent, m pentru

mantisa si cate unul pentru semn si hidden bit.

) biti, anume e

pentru exponent, m pentru

mantisa si cate unul pentru semn si hidden bit.

Fata de cele

cunoscute anterior relativ la o configuratie cum este cea a

unitatii de significand din fig.5.3, mai admitem ca nu doar

registrul A are capacitatea de deplasare la dreapta (el putand fi deplasat

si la stanga), ci si registrul M. Cele doua registre A si M

au cate (![]() ) biti pentru a putea stoca numerele significand cu

semne asociate lor, iar A mai are asociat un flag, A-COUT, care este setat pe

1, in mod implicit, atunci cand se obtine transport (cout) din

rangul msb al adder/subtracter-ului).

) biti pentru a putea stoca numerele significand cu

semne asociate lor, iar A mai are asociat un flag, A-COUT, care este setat pe

1, in mod implicit, atunci cand se obtine transport (cout) din

rangul msb al adder/subtracter-ului).

In ceea ce priveste unitatea de exponent, compararea continutului celor doua registre de exponent, E1 si E2, fiecare de e biti , se realizeaza prin operatia de scadere, a carei rezultat este incarcat in registrul E, si el tot de e biti. Acest registru are capacitatea de incrementare si decrementare a continutului sau, ceea ce se petrece atat in operatia de aliniere a numerelor significand, cat si la cea de normalizare a rezultatului, evident, doar pana la aparitia situatiilor de overflow sau underflow. Mai mentionam ca in E se incarca, dupa ce a fost traversata operatia de aliniere, valoarea exponentului mai mare dintre continuturile lui E1 si E2, tatonarea acestui fapt se presupune a fi facuta in mod cablat.

Cu aceste precizari,

in termenii limbajului de descriere cunoscut, prezentam in fig.5.10 secventa

de cod corespunzatoare procedurii de adunare/scadere la care nu s-au

facut nici un fel de referiri la procesul de rotunjire, toti

bitii care, prin deplasari, parasesc registrele fiind

considerati trunchiati, pierduti. Ar fi de mentionat

ca in descriere, la incarcarea registrelor cu operanzii intrare (enunturile

INPUT), nu au fost detaliati bitii magistralei INBUS care contribuie

la parte de exponent, respectiv de mantisa, fiind specificati doar

operanzii (![]() si

si ![]() respectiv

respectiv ![]() si

si ![]() ). De asemenea, operatiile de deplasare, la stanga

si la dreapta, precum si cele de tatonare a unui rezultat normalizat

nu au fost prezentate in detaliu. Recurgand in aceeasi nota, si la

alte simplificari, o observatie aparte se impune relativ la

exceptii care au fost rezumate doar la unele dintre situatiile

posibile de overflow si underflow, precum si la cea de rezultat zero.

Astfel a fost prevazut un singur flag, ERROR, care este setat pe 1 atunci

cand este necesara o deplasare la dreapta a significand-ului rezultat din

A si exponentul are deja valoarea sa maxima reprezentabila,

). De asemenea, operatiile de deplasare, la stanga

si la dreapta, precum si cele de tatonare a unui rezultat normalizat

nu au fost prezentate in detaliu. Recurgand in aceeasi nota, si la

alte simplificari, o observatie aparte se impune relativ la

exceptii care au fost rezumate doar la unele dintre situatiile

posibile de overflow si underflow, precum si la cea de rezultat zero.

Astfel a fost prevazut un singur flag, ERROR, care este setat pe 1 atunci

cand este necesara o deplasare la dreapta a significand-ului rezultat din

A si exponentul are deja valoarea sa maxima reprezentabila, ![]()

Referindu-ne

la procedura din fig. 5.10, in urma incarcarii operanzilor si

inainte de compararea rezultatelor, este recomandabila testarea de zero a

ambilor operanzi significand, situatie in care rezultatul poate fi

anticipat fara a mai parcurge intreaga procedura. In rest, operatiile elementare

se inlantuie conform cu cele descrise de (5.1), in sensul ca, in

urma compararii - prin scadere - a exponentilor, se aliniaza

mantisele, operatie legat de care ar fi posibila o interventie

in procedura pentru a stopa deplasarile in vederea alinierii

dupa (![]() ) pasi si dupa │E│pasi,

intrucat putem avea │E│>(

) pasi si dupa │E│pasi,

intrucat putem avea │E│>(![]() ) si atunci numarul de pasi diferenta

(│E│- m - 1) sunt inutili, significand-ul deplasat, oricum, devenind

zero. Urmarind in continuare procedura, dupa alinierea numerelor

significand, se executa operatia propriu-zisa, care este

succedata de normalizarea rezultatului in vederea impachetarii sale,

cu corespunzatoare tatonari de cazuri exceptii. Acestei

descrieri a procedurii de adunare/scadere ii corespunde aproape intocmai

schema bloc a unui calculator celebru in epoca sistemnelor de capacitate medie

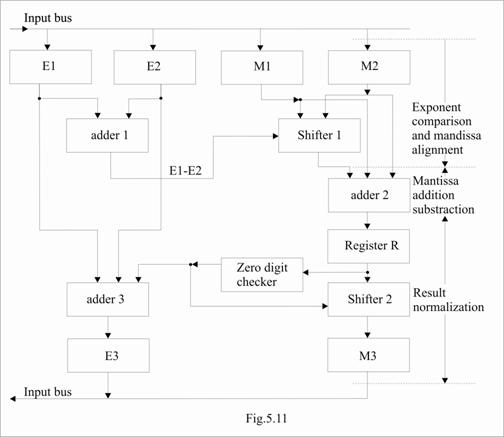

si mare, de tip mainframe, anume IBM/S360, model 91. Aceasta

masina include doua unitati separate de virgula

mobila, una destinata operatiilor de adunare si

scadere (add unit), iar cealalta destinata operatiilor de

inmultire si impartire (multiply/divide unit) [Haye98]. Ne

vom referi doar la add unit care permite adunarea/scadere de numere pe 32,

respectiv 64 de biti. Motivul inserarii schemei bloc

corespunzatoare (acestei unitati fig. 5.11 [Haye98]) in aceasta lucrare este, pe

langa faptul ca poate sa constituie o sinteza a ceea ce

este prezentat mai in amanunt in fig. 5.10, pune in relief unele mecanisme

hardware de accelerare a procesului de adunare.

) si atunci numarul de pasi diferenta

(│E│- m - 1) sunt inutili, significand-ul deplasat, oricum, devenind

zero. Urmarind in continuare procedura, dupa alinierea numerelor

significand, se executa operatia propriu-zisa, care este

succedata de normalizarea rezultatului in vederea impachetarii sale,

cu corespunzatoare tatonari de cazuri exceptii. Acestei

descrieri a procedurii de adunare/scadere ii corespunde aproape intocmai

schema bloc a unui calculator celebru in epoca sistemnelor de capacitate medie

si mare, de tip mainframe, anume IBM/S360, model 91. Aceasta

masina include doua unitati separate de virgula

mobila, una destinata operatiilor de adunare si

scadere (add unit), iar cealalta destinata operatiilor de

inmultire si impartire (multiply/divide unit) [Haye98]. Ne

vom referi doar la add unit care permite adunarea/scadere de numere pe 32,

respectiv 64 de biti. Motivul inserarii schemei bloc

corespunzatoare (acestei unitati fig. 5.11 [Haye98]) in aceasta lucrare este, pe

langa faptul ca poate sa constituie o sinteza a ceea ce

este prezentat mai in amanunt in fig. 5.10, pune in relief unele mecanisme

hardware de accelerare a procesului de adunare.

Astfel, cei doi exponenti sunt stocati in registrele ![]() si

si![]() si diferenta dintre continuturile lor,

evaluata prin adder 1, determina care dintre mantise (inca nu era

cunoscuta notiunea de significand), stocate in registrele

si diferenta dintre continuturile lor,

evaluata prin adder 1, determina care dintre mantise (inca nu era

cunoscuta notiunea de significand), stocate in registrele ![]() si

si ![]() , trebuie deplasata la dreapta in vederea alinierii.

Trebuie mentionat ca, intrucat baza sistemului de numeratie a

intregii serii de fabricatie careia ii apartine si calculatorul

in discutie este

, trebuie deplasata la dreapta in vederea alinierii.

Trebuie mentionat ca, intrucat baza sistemului de numeratie a

intregii serii de fabricatie careia ii apartine si calculatorul

in discutie este ![]() , atunci daca

, atunci daca ![]() , intrucat k este un numar hexazecimal, numarul

pozitiilor binare de deplasat la dreapta este 4k. Intregul proces de

aliniere a mantiselor este accelerat printr-o schema combinationala

de deplasare, notata Shifter 1, care permite efectuarea acestei

operatii simultan pentru cele 4k pozitii binare. In continuare,

mantisa deplasata este adunata/scazuta la/din mantisa

nedeplasata prin adder 2, reprezentand un sumator/scazator pe 56

biti (64 biti din care se scade bitul de semn si 7 biti

pentru campul de exponent) implementat cu mai multe niveluri de

carry-lookahead. Suma/diferenta preliminara este memorata

temporar in registrul R, a carui continut este investigat de schema

combinationala, notata zero digit checker, a carei menire

consta in determinarea numarului de cifre hex egale cu zero, asa

numite leading zeros, care trebuie eliminate prin procesul de normalizare.

Valoarea determinata prin acest al doilea element de structura destinat

accelerarii adunarii, constituit de zero digit checker,

determina pe de o parte, numarul de pozitii hexazecimale cu care

trebuie deplasata la stanga mantisa suma/diferenta

preliminara din R, operatie care este de asemenea accelerata

printr-o schema combinationala, notata Shifter 2 in fig.

5.11. Acest al treilea element de structura de accelerare asigura

deplasarea simultana a mantisei preliminara cu numarul de

leading zerouri determinate de zero digit checker. Pe de alta parte,

aceasta din urma valoare intervine, prin adder 3, fiind scazuta

din valoarea gasita mai mare la compararea exponentilor,

definitivand procesul de normalizare al rezultatului, al carui exponent

si mantisa finale vor fi preluate din registrele E3 si M3. In

mod evident, cele trei scheme de accelerare, precum si baza

, intrucat k este un numar hexazecimal, numarul

pozitiilor binare de deplasat la dreapta este 4k. Intregul proces de

aliniere a mantiselor este accelerat printr-o schema combinationala

de deplasare, notata Shifter 1, care permite efectuarea acestei

operatii simultan pentru cele 4k pozitii binare. In continuare,

mantisa deplasata este adunata/scazuta la/din mantisa

nedeplasata prin adder 2, reprezentand un sumator/scazator pe 56

biti (64 biti din care se scade bitul de semn si 7 biti

pentru campul de exponent) implementat cu mai multe niveluri de

carry-lookahead. Suma/diferenta preliminara este memorata

temporar in registrul R, a carui continut este investigat de schema

combinationala, notata zero digit checker, a carei menire

consta in determinarea numarului de cifre hex egale cu zero, asa

numite leading zeros, care trebuie eliminate prin procesul de normalizare.

Valoarea determinata prin acest al doilea element de structura destinat

accelerarii adunarii, constituit de zero digit checker,

determina pe de o parte, numarul de pozitii hexazecimale cu care

trebuie deplasata la stanga mantisa suma/diferenta

preliminara din R, operatie care este de asemenea accelerata

printr-o schema combinationala, notata Shifter 2 in fig.

5.11. Acest al treilea element de structura de accelerare asigura

deplasarea simultana a mantisei preliminara cu numarul de

leading zerouri determinate de zero digit checker. Pe de alta parte,

aceasta din urma valoare intervine, prin adder 3, fiind scazuta

din valoarea gasita mai mare la compararea exponentilor,

definitivand procesul de normalizare al rezultatului, al carui exponent

si mantisa finale vor fi preluate din registrele E3 si M3. In

mod evident, cele trei scheme de accelerare, precum si baza ![]() , determina unele deosebiri intre schema din fig. 5.11

si descrierea din fig. 5.10.

, determina unele deosebiri intre schema din fig. 5.11

si descrierea din fig. 5.10.

|

Politica de confidentialitate |

| Copyright ©

2024 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |