Sumatoare paralele pe principiul omiterii propagarii seriale a transportului

Solutiile de proiectare a sumatoarelor pe principiile clasice RCA si CLA reprezinta extremele atat in termeni de performanta, cat si de cost. Intre acestea pot fi adoptate unele solutii hibride care combina cele 2 concepte, dar si cea care se bazeaza pe omiterea propagarii seriale a transportului cunoscuta sub denumirea carry-skip adder (prescurtarea CSA, potrivita pentru acest sumator,a fost atribuita sumatorului bazat pe principiul salvarii transportului denumit carry slave adder, asa incat vom folosi pentru sumatorul in discutie prescurtarea CSkA) [HePa03]. La cosntructia CSkA se pleaca de la analiza ecuatiilor booleene pentru functiile G si P, care in cazul segmentului cel mai putin semnificativ de 4 biti, au cunoscutele expresii G0,3 = g3 + p3g2 + p3p2g1 + p3p2p1g0, respectiv P0,3 = p3p2p1.

Dintre cele doua ecuatii, calculul lui P0,3 este mult mai facil decat al lui G0,3 necesitand doar o poarta AND cu patu intrari, ceea ce se exploateaza la constitutia unui CSkA si anume cand semnalul de propagare corespunzator unui bloc de ranguri, cum este cel asociat, spre exemplu, lui P0,3, devine activ, transportul nu se mai propaga serial, din rang, ca la un sumator RCA, ci se creeaza o cale de propagare bypass a blocului care evita, omite (skip) transmisia lui carry prin rangurile blocului.

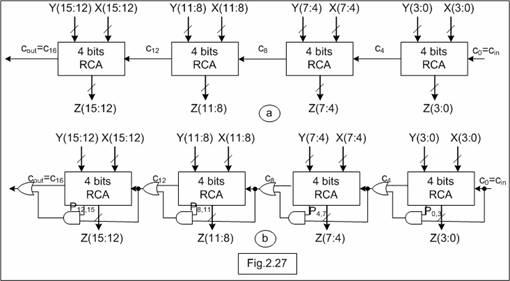

Astfel, in figura 2.2.7a se prezinta, schematic, un sumator RCA pe 16 biti, iar in figura 2.2.7b este data versiunea acestuia transformata intr-un sumator CSkA. Omiterea unui bloc se realizeaza prin portile AND care permite trecerea transporturilor c0, c4, c8 si c12, atunci cand functiile P0,3, P4,7, P8,11, P12,15 au valoarea logica 1, fiecare dintre acestea fiind obtinute prin produsul logic . patru variabile de propagare p, la randul lor obtenabile prin cate o poarta OR din variabile de intrare x si y.

Se impune precizarea ca principiul bypass-arii devine doar atunci practic daca se dispune de o tehnologie care sa permita implementarea fara dificultati, la inceputul fiecarei operatii, a semnalelor de carry-in pentru fiecare bloc al sumatorului. Preincarcarea (precharging) in tehnologia CMOS asigura indeplinirea acestui deziderat, permitand evitarea generarii la fiecare bloc, a unor semnale carry-out neautentice. Plecand din starea initiala cu toate carry-in-urile de bloc pe 0, transporturile se vor propaga serial, in mod simultan, in paralel, prin fiecare bloc. Astfel, daca intr-un anumit bloc se genereaza un transport atunci carry-out-ul respectivului bloc este obtinut in mod corect chiar daca carry-in-ul la acel bloc nu a atins inca valoarea corecta. Intr-un fel, carry-out-urile blocurilor pot fi asimilate functiilor G specifice conceptului CLA multilevel. Odata ce este generat carry-out-ul unui anumit bloc, asa cum rezulta din figura 2.2.7b el este aplicat nu numai blocului urmator mai semnificativ, ci ... portii AND menita a inlesni bypass-area, trecand prin aceasta cand ii permite functia P asociata respectivului bloc. In acest mod la CSkA-ul din figura 2.27b, intarzierea corespunzatoare propagarii

de carry cea mai defavorabila (worst-case carry propagation delay) se obtine in cazul cand carry este generat in rangul 0, cel mai putin semnificativ, trecand, in mod serial prin rangurile 1 la 3 si apoi prin poarta OR asociata primului bloc, bypass-and urmatoarele doua blocuri prin perechi de porti AND-OR si fiind propagat, tot serial, prin rangurile de la 12 la 15, ceea ce cumuleaza 20 de niveluri de poarta pana in momentul obtinerii corecte a bitului suma z15 . Se obtine, prin urmare, o imbunatatire de performanta consistenta in raport cu cele 2x16 = 32 niveluri logice ale RCA-ului de aceeasi dimensiune(fig 2 27.a).

Trecand la generalizarea exemplului din figura 2.27, intarzierea de propagare cea mai defavorabila, corespunzatoare unui CSkA de n ranguri impartit in blocuri de cate b ranguri se obtine pentru generarea transportului in rangul lsb si propagarea acestuia pana la obtinerea corecta a bitului suma msb, insumand cele 2b niveluri logice din blocul cel mai putin semnificativ cu nivelul corespunzator portii OR asociata acestui bloc, la care se cumuleaza 2(n/b-2) niveluri logice corespunzatoare blocurilor situate intre cele extreme si bypass-ate prin perechi de porti AND-OR si (2(b-1)+1) niveluri logice pentru propagarea seriala prin blocul msb pana la rangul msb, inclusiv poarta EXCLUSIVE-OR finala corespunzatoare obtinerii bitului suma msb. Notand cu L latenta unui CSkA cu blocuri de lungime fixa b, exprimata in termeni de niveluri logice, in ipoteza admiterii acelorasi intarzieri pe porti, indiferent de tipul acestora, obtinem pentru acest parametru de performanta:

L = 2b + 1 + 2(n/b-2) + 2(b-1) + 1 = 2(n/b+2b-2) (2.12)

Plecand de la (2.12), sa determinam dimensiunea optima , bopt , pentru blocurile structurii CSkA sens in care anulam derivata latentei L in raport cu b, obtinand

![]() (2.13)

(2.13)

Introducand (2.13) in (2.12), rezulta intarzierea defavorabila corespunzatoare segmentarii CSkA in blocuri de lungime fixa optima, si anume:

![]() (2.14)

(2.14)

Exemplificand, sa consideram constructia unui CSkA cu n = 32 ranguri, pentru care rezulta, in conformitate cu (2.13), bopt = 4 si in conformitate cu (2.14), Lopt = 28 niveluri logice, ceea ce reprezinta o performanta de aproape 2,3 ori mai buna decat cea corespunzatoare RCA-ului de aceeasi dimensiune.

Pe de alta parte, este evidenta observatia conform careia un transport generat sau absorbit de catre unul dintre blocurile interioare, situat intre cele doua blocuri extreme, va trebui propagat prin mai putine niveluri logice, ceea ce conduce la ideea ca acestor blocuri li se pot aloca mai multe ranguri cu propagare seriala adica implicit la faptul ca blocurile sa fie de lungime variabila. In ceea ce priveste numarul de blocuri variabile, precum si dimensiunile acestora, pot fi realizate analize care insa accepta ipoteze simplificatorii dintre care multe nu sunt confirmate de practica inginereasca. Unul dintre factorii care influenteaza in mod decisiv optimizarea unui proiect de CSkA este cel tehnologic, care din nefericire, este facut cunoscut, in mod uzual, doar dupa ce devine perimat [ErLa b4][ParL00]. Fara un suport formal riguros, exista experimente reusite de partitionare a rangurilor in blocuri de dimensiune variabila, context in care amintim ca CSkA de 20 de biti impartit in 5 blocuri de 2,5,6,5 si 2 ranguri [HePa03]. Latenta defavorabila, in termeni de niveluri logice, pentru acest CSkA implica propagarea semnalelor prin 2x6 = 12 porti ale blocului median (intervalul de timp in care un potential carry generat in rangul LSB al acestui punct este considerat egal cu cel necesar propagarii unui potential carry din rangul LSB al anteriorului bloc, de 5 ranguri, care trebuie sa traverseze, de asemenea, portile OR si AND), la care se adauga poarta OR de la iesirea blocului median, perechea de porti AND-OR asociata blocului de 5 ranguri mai semnificativ, precum si cele 3 porti (AND-OR si EXCLUSIVE-OR) din ulteriorul segment, cel cu 2 ranguri. Rezulta un total de 18 niveluri logice, substantial mai putine decat cele 40 revendicate de un RCA de acelasi dimensiune, dar mai putine si decat solutia CSkA partitionat de 5 blocuri de aceeasi dimensiune, de 4 ranguri, pentru care, aplicand (2.12), se obtine L = 2 niveluri logice.

In final, mai remarcam posibilitatea de a configura CSkA cu mai multe niveluri (multilevel) in care se permite bypass-area de carry a mai multor blocuri [ParL00]. In acest sens, semnalele de skip de la iesirile portilor AND sunt aplicate unei porti AND de pe un nivel superior, numarul de intrari corespunzator acesteia corespunzand numarului de blocuri bypass-at, si de asemenea, poarta OR de la iesirea grupului de blocuri bypass-at are o intrare suplimentara. Rezulta in acest mod o structura etajata cu 2 niveluri, dar problema configurarii optimale a sumatoarelor CSkA ramane deschisa.

|

Politica de confidentialitate |

| Copyright ©

2024 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |