Modulul de captura/comparare/PWM (CCP)

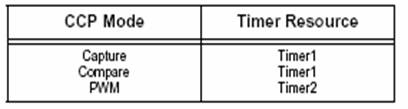

Fiecare modul CCP (Captura/Comparare/PWM) contine un registru de 16 biti, care poate functiona ca registru de captura pe 16 biti, ca registru de comparare pe 16 biti sau ca registru PWM master/slave pentru ciclul util. Tabelul X.3.9-1 prezinta sursele pentru timer ale modurilor modulului CCP.

Tabelul X.3.9-1 - Modurile CCP - sursele pentru timer

Functionarea lui CCP1 este identica cu cea a lui CCP2, cu exceptia trigger-ului special. De aceea, functionarea unui modul CCP este descrisa in continuare cu privire la CCP1.

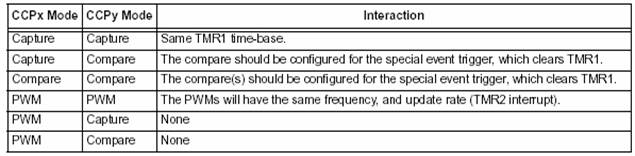

Tabelul X.3.9-2 prezinta interactiunile modulelor CPP.

Tabelul X.3.9-2 - Interactiunea a doua module CPP

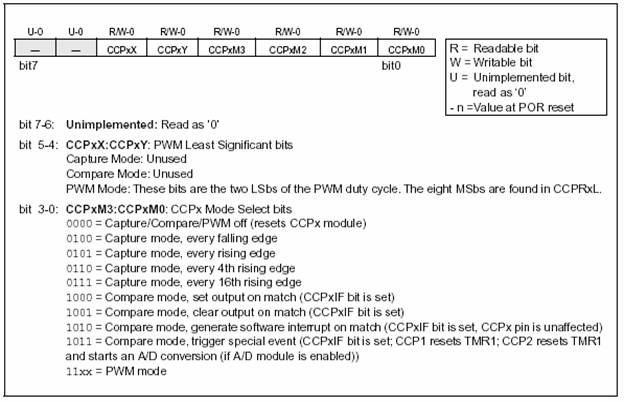

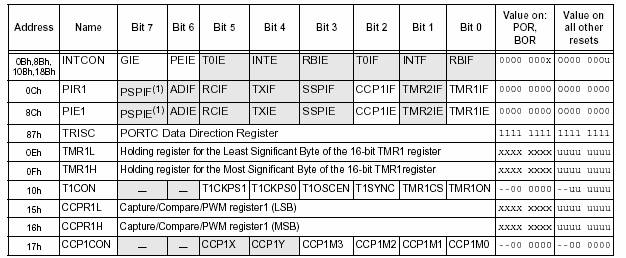

Registrul CCPR1 (Captura/Comparare/PWM) este alcatuit din doua registre de 8 biti : CCPR1L (octetul inferior) si CCPR1H (octetul superior). Registrul CCP1CON controleaza functionarea lui CCP1. Toate pot fi citite si scrise.

Registrul CCPR2 (Captura/Comparare/PWM) este alcatuit din doua registre de 8 biti : CCPR2L (octetul inferior) si CCPR2H (octetul superior). Registrul CCP2CON controleaza functionarea lui CCP2. Toate pot fi citite si scrise.

Figura X.3.9-1 - Registrul CCP1CON (adresa 17H) / registrul CCP2CON (adresa 1DH)

1 Modul Captura

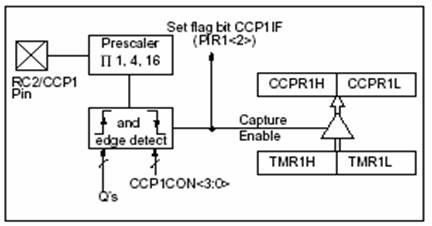

In modul Captura, CCPR1H:CCPR1L captureaza valuarea pe 16 biti a registrului TMR1 cand se produce un eveniment la pinul RC2/CCP1. Un eveniment este definit ca :

fiecare front cazator

fiecare front crescator

fiecare al patrulea front crescator

fiecare al saisprezecelea front crescator

Un eveniment este selectat prin bitii de control CCP1M3:CCP1M0 (CCP1CON<3:0>). Cand este facuta o captura, bitul de flag de intrerupere CCP1IF (PIR1<2>) este setat. El trebuie resetat prin program. Daca o alta captura are loc inainte de citirea valorii din registrul CCPR1, vechea valoare capturata se va pierde.

1.1 Configuratia pinului CCP

In modul Captura, pinul RC2/CCP1 trebuie configurat ca intrare prin setarea bitului TRISC<2>.

Nota : Daca pinul RC2/CCP1 este configurat ca iesire, o scriere in port poate determina o conditie de captura.

Figura X.3.9-2 - Diagrama bloc de functionare a modului Captura

1.2 Selectia modului pentru Timer1

Timer1 trebuie sa lucreze in modul timer sau in modul numarator sincronizat pentru ca modulul CCP sa poata folosi facilitatea de captura. In modul numarator asincron, operatia de captura poate sa nu functioneze.

1.3 Intreruperea software

Cand este schimbat modul Captura, poate fi generata o intrerupere falsa de captura. Utilizatorul trebuie sa pastreze resetat bitul CCP1IE (PIE1<2>) pentru a evita intreruperi false si trebuie sa reseteze bitul de flag CCP1IF imediat dupa fiecare asemenea schimbare in modul de operare.

1.4 Prescaler-ul CCP

Exista patru setari pentru prescaler, date de bitii CCP1M3:CCP1M0. De fiecare data cand modulul CCP este oprit sau nu este in modul Captura, numaratorul prescaler-ului este resetat. Asta insemna ca orice reset va reseta numaratorul prescaler-ului.

Comutand de la un prescaler de captura la altul se poate genera o intrerupere. De asemenea, numaratorul prescaler-ului nu va fi resetat, de aceea prima captura poate fi dintr-un prescaler nenul. Exemplul X.3.9-1 prezinta metoda recomandata pentru comutarea intre prescaler-ele de captura. Acest exemplu reseteaza si numaratorul prescaler-ului si nu va genera intreruperea "falsa".

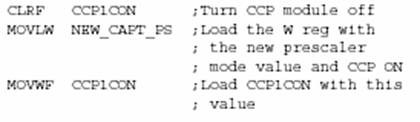

Exemplul X.3.9-1 - Comutarea intre prescaler-ele de captura

2 Modul Comparare

In modul Comparare, valoarea registrului de 16 biti CCPR1 este comparata continuu cu valoarea perechii de registre TMR1. Cand se produce o potrivire, pinul RC2/CCP1 este :

pus pe '1'

pus pe '0'

ramane neschimbat

Actiunea asupra pinului este bazata pe valoarea bitilor de control CCP1M3:CCP1M0 (CCP1CON<3:0>). In acelasi timp este setat bitul de flag CCP1IF.

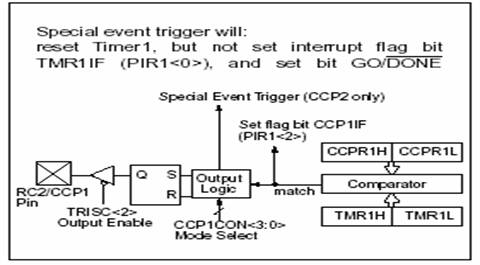

Figura X.3.9-3 - Diagrama bloc de functionare a modului Comparare

2.1 Configurarea pinului CCP

Utilizatorul trebuie sa configureze pinul RC2/CCP1 ca iesire prin resetarea bitului TRISC<2>.

Nota : Resetarea registrului CCP1CON va forta latch-ul de pe iesirea de comparare a pinului RC2/CCP1 pe nivelul predefinit de '0'. Acesta nu este latch-ul de date.

2.2 Selectarea modului pentru Timer1

Timer1 trebuie sa lucreze in modul timer sau numarator sincronizat daca modulul CCP foloseste facilitatea de comparare. In modul numarator asincron, operatia de comparare poate sa nu mearga.

2.3 Modul intrerupere software

Cand este aleasa intreruperea generata software, pinul CCP1 nu este afectat. Este generata doar o intrerupere CCP (daca este validata).

2.4 Trigger-ul special de eveniment

In acest mod, este generat un trigger hardware intern, care poate fi folosit pentru a initia o actiune.

Iesirea speciala de trigger de eveniment a lui CCP1 reseteaza perechea de registre TMR1. Aceasta permite ca registrul CCPR1 sa fie efectiv un registru pe 16 biti de perioada programabila pentru Timer1.

Iesirea speciala de trigger a lui CCP2 reseteaza perechea de registre TMR1 si starteaza o conversie A/D (daca modulul A/D este validat).

Nota : Trigger-ul special de evenimente al modulului CCP2 nu va seta bitul de flag de intrerupere TMR1IF (PIR1<0>).

Tabelul X.3.9-3 - Registrele asociate cu captura, compararea si cu Timer1

Legenda : x=necunoscut; u=nemodificat; -=neimplementat, citit ca '0'. Celulele hasurate nu sunt folosite de Captura si de Timer1.

Nota : Bitii PSPIE si PSPIF sunt rezervati la dispozitivele cu 28 de pini, pastrati intotdeauna acesti biti resetati.

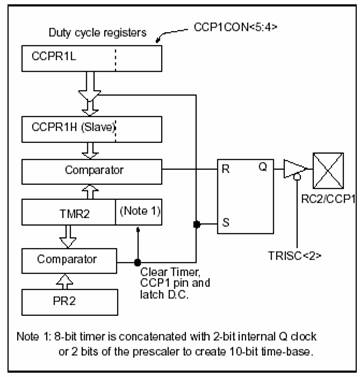

3 Modul PWM

In modul PWM - Modulatie prin latimea pulsului (Pulse Width Modulation), pinul CCP1 produce o iesire PWM cu o rezolutie de pana la 10 biti. De vreme ce pinul CCP1 este multiplexat cu latch-ul de date al portului PORTC, bitul TRISC<2> trebuie resetat pentru a configura pinul ca iesire.

Nota : Resetarea registrului CCP1CON va forta latch-ul de iesire PWM al pinului CCP1 pe nivelul predefinit de '0'. Acesta nu este latch-ul I/O de date al portului PORTC.

Figura X.3.9-4 prezinta o diagrama bloc simplificata a modulului CCP in modul PWM.

Figura X.3.9-4 - Diagrama bloc simplificata a modului PWM

O procedura pas cu pas pentru configurarea modulului CCP pentru functionare PWM este prezentata in sectiunea 3.3.

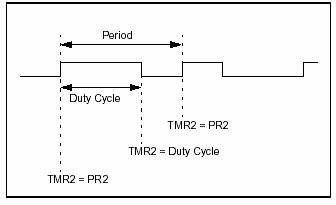

O iesire PWM (Figura X.3.9-5) are o baza de timp (perioada) si un timp in care iesirea sta in '1' (ciclul util). Frecventa pentru PWM este inversul perioadei (1/perioada).

Figura X.3.9-5 - Iesirea PWM

3.1 Perioada PWM

Perioada PWM este specificata prin scrierea in registrul PR2. Ea poate fi calculata cu formula urmatoare :

Perioada PWM = [(PR2 1]*4*TOSC*(valoarea prescaler-ului pentru TMR2)

Frecventa PWM este definita ca 1 perioada PWM].

Cand TMR2 este egal cu PR2, se produc urmatoarele trei evenimente in urmatorul ciclu de incrementare :

TMR2 este resetat

Pinul CCP1 este setat (exceptie : daca ciclul util PWM =0%, pinul CCP1 nu va fi setat)

Ciclul util PWM este memorat din CCPR1L in CCPR1H.

Nota : Postscaler-ul pentru Timer2 nu este folosit la determinarea frecventei PWM. Acesta poate fi folosit pentru a avea o rata automata de modificare la o frecventa diferita de cea a iesirii PWM.

3.2 Ciclul util PWM

Ciclul util PWM este specificat prin scrierea in registrul CCPR1L si a bitilor CCP1CON<5:4>. Este disponibila o rezolutie de pana la 10 biti : CCPR1L contine cei mai semnificativi 8 biti si CCP1CON<5:4> contine cei mai putin semnificativi 2 biti. Aceasta valoare pe 10 biti este reprezentata de CCPR1L:CCP1CON<5:4>. Ecuatia urmatoare este folosita pentru a calcula ciclul util PWM in timp :

Ciclul util PWM = (CCPR1L:CCP1CON<5:4>)*TOSC*(valoarea prescaler-ului pentru TMR2)

CCPR1L si CCP1CON<5:4> pot fi scrise oricand, dar valoarea ciclului util nu este memorarata in CCPR1H decat dupa a potrivire intre PR2 si TMR2 (de exemplu : cand perioada este completa). In modul PWM registrul CCPR1H poate fi doar citit.

Registrul CCPR1H si un latch intern pe 2 biti sunt folositi pentru a buffera dublu ciclul util PWM. Aceasta buffer-are dubla este esentiala pentru o functionare PWM fara paraziti.

Cand CCPR1H si latch-ul pe 2 biti se potrivesc cu TMR2 concatenat cu un clock Q pe 2 biti sau cu 2 biti ai prescaler-ului pentru TMR2, pinul CCP1 este resetat.

Rezolutia maxima PWM (numarul de biti) pentru o frecventa PWM data este :

log(FOSC / FPWM) / log(2) biti.

Nota : Daca valoarea ciclului util PWM este mai mare decat perioada PWM, pinul CCP1 nu va fi resetat.

3.2 Configurarea pentru functionare in modul PWM

Pasii urmatori trebuie urmati la configurarea modulului CCP pentru functionarea in modul PWM:

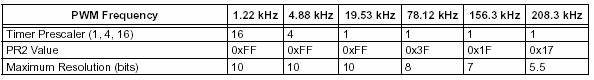

Tabelul X.3.9-4 - Exemplu de frecvente PWM si de rezolutii la 20 MHz

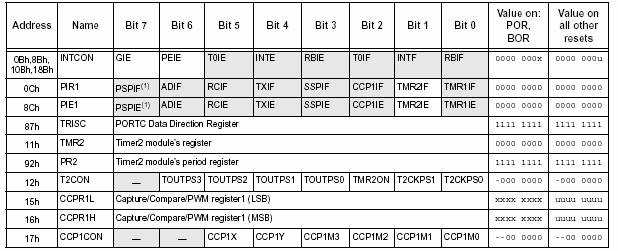

Tabelul X.3.9-5 - Registrele asociate cu PWM si Timer2

Legenda : x=necunoscut; u=nemodificat; -=neimplementat, citit ca '0'. Celulele hasurate nu sunt folosite de PWM si de Timer2.

Nota : Bitii PSPIE si PSPIF sunt rezervati la dispozitivele cu 28 de pini, pastrati intotdeauna acesti biti resetati.

|

Politica de confidentialitate |

| Copyright ©

2024 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| STRUCTURA BENZII DE FRECVENTA ALOCATA SERVICIULUI GSM |

| Reflectorul parabolic |

| SISTEME DE ANTENA |

| Antena dipol |

| DECT |

| CODAREA SEMNALULUI VOCAL |

| Fisa de masuratori prin tehnologie GPS |

| Antene active |

| Termeni si conditii |

| Contact |

| Creeaza si tu |