52. Comunicarea UC - controler DMA - periferic

Perifericul cere transfer de tip DMA activand intrarea DREQ (DMA Request) a controlerului DMA;

Controlerul DMA activeaza iesirea sa HRQ spre intrarea HOLD a procesorului anuntandu-l ca are nevoie de magistrale;

Procesorul incheie ciclul masina inceput, isi trece magistralele si semnalele de comanda in a 3 - a stare, respectiv in starea inactiva, si activeaza iesirea HLDA anuntand controlerul DMA ca a cedat magistralele; cererea de pe intrarea HOLD trebuie sa ramina activa pe toata durata transferului DMA;

Controlerul DMA activeaza iesirea sa DACK comunicand perifericului ca cererea sa DREQ a fost acceptata si va incepe transferul;

Controlerul DMA executa transferurile:

i. Memorie - port: pune adresa primului octet (cuvant) pe magistrala de adrese, actveaza semnalul de comanda MEMR si apoi IOW,

ii. Port - memorie: activeaza semnalul de comanda IOR, pune adresa primului octet (cuvant) pe magistrala de adrese si apoi MEMW;

Dupa incheierea transferurilor controlerul DMA dezactiveaza iesirea HRQ anuntand procesorul ca nu mai are nevoie de magistrale.

53. Circuitul 82C37A: rol, caracteristici

Dispune de 4 canale independente,

Poate fi cascadat pentru a obtine oricate canale,

Control individual (activare/ dezactivare si polaritate) asupra fiecarei cereri DREQ si fiecarui raspuns DACK,

Permite transfer memorie - memorie,

Rata de transfer ridicata:

i. Pana la 4 MO/ sec. cu tact de 8 MHz si

ii. Pana la 6.25 MO/ sec. cu tact de 12.5 MHz,

Asigura incrementarea sau decrementarea adresei,

Se foloseste cu un registru extern pentru jumatatea mai semnificativa a adresei,

Poate lucra in mai multe moduri,

Compatibil TTL/ CMOS.

54. Descrieti 2 tipuri de cicluri active ce pot fi executate de circuitul 82C37A

Demand transfer mode:

Se tranfera date continuu pana cand:

i. TC este setat sau

ii. /EOP este activat sau

iii. Cererea DREQ devine inactiva.

Mod util atunci cand un periferic doreste sa-si goleasca tamponul de date, indiferent de capacitatea acestuia.

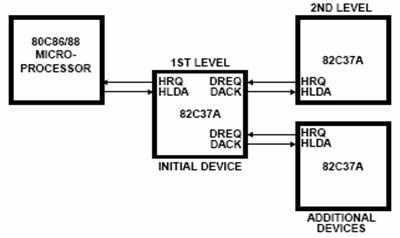

Cascade mode:

q Permite extinderea numarului de canale prin legarea in cascada a mai multor circuite 82C37A;

q Figura urmatoare arata o cascadare pe 2 nivele:

q Pot fi atasate noi nivele la intrarile DREQ libere ale circuitelor de pe nivelul 2;

q Programarea incepe cu circuitul cel mai aproape de procesor

55. Enumerati citeva tipuri de informatii trimise circuitului 82C37A prin programare

In prealabil canalul a fost programat prin intermediul registrelor Command, Mode, Address si Word; de ex. pentru un transfer DMA - port:

Adresa de inceput este incarcata in Base si Current Address Registers, ale canalului implicat,

Lungimea blocului este incarcata in Word Count register corespunzator,

Mode Register corespunzator este programat pentru un transfer memorie - port,

Optiuni sunt selectate prin Command Register si Mode Register,

Bitul de mascare a canalului este pus la 0 pentru a valida o cerere DREQ; aceasta poate fi un semnal sau o comanda software.

56. Intreruperile: ce inseamna, la ce folosesc si de cate tipuri sunt?

Permit abandonarea momentana de catre microprocesor a executiei unui program si inceperea executiei unui alt program situat oriunde in spatiul de memorie.

Se folosesc la:

Comunicarea UC - periferie,

In sisteme multiprocesor.

2 tipuri:

Externe si

Interne.

57. Intreruperile interne

Se gasesc la microprocesoarele peste 8 biti si la toate microcontrolerele;

Se numesc si exceptii la unele microprocesoare;

O parte din ele se numesc si "traps" la unele microprocesoare;

Provocate de cauze interne procesorului;

La microcontrolere pot fi mascate, la microprocesoare nu;

2 tipuri de cauze (la microprocesoare):

Evenimente interne speciale sau

Instructiuni dedicate (se mai numesc si intreruperi software).

Intreruperi interne provocate de evenimente speciale:

Pot fi generate inainte de executia unei instructiuni: de ex.: o violare de privilegiu sau cod ilegal etc.;

Pot fi generate dupa executia unei instructiuni: de ex.: o divizare la 0, obtinerea unui rezultat in afara unui domeniu, pas cu pas etc.

n Intreruperi interne datorate instructiunilor:

q Exista instructiuni ale caror executie este echivalenta cu generarea unei cereri de intrerupere; de ex.:

n INT nn la familia Intel,

n TRAP #n la microprocesoarele Motorola.

q Pot fi folosite pentru emularea a noi instructiuni.

n Pe langa o eventuala prioritizare externa, exista si o prioritizare implicita a surselor de interupere; de ex. la 8086:

q Eroare la divizare, INT nn - prioritate maxima,

q INTO,

q NMI,

q INTR,

q Pas cu pas - prioritate minima.

58. Cum sunt tratate cererile de intrerupere?

Tratarea cererilor de intrerupere:

Programul principal este oprit;

Procesorul salveaza, in stiva, continutul PC si, in unele cazuri, si alte informatii - aceste informatii vor fi folosite la revenirea din rutina de tratare a cererii de intrerupere;

Procesorul incarca in PC adresa de inceput a ISR ("Interrupt Service Routine");

Adresa de inceput este:

i. Fixa,

ii. Obtinuta dintr - o tabela - vectorul de intrerupere este folosit ca deplasament pentru a ajunge la intrarea ce contine adresa de inceput.

Se executa ISR; trebuie evitata decalarea stivei;

La sfarsitul ISR se reactiveaza sistemul de intreruperi (daca s - a tratat o cerere externa mascabila);

Revenirea in programul principal se face cu o instructiune dedicata (de ex. IRET la familia Intel) care aduce din stiva continutul PC-ului.

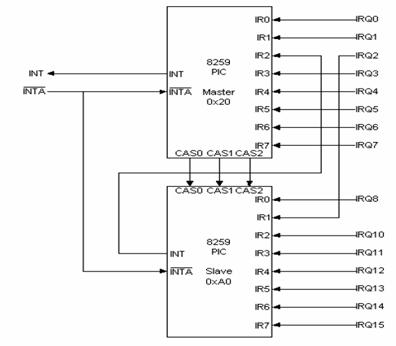

59. Circuitul 8259A: rol, caracteristici si schema interna

Poate gestiona si prioritiza 8 cereri de intrerupere

Poate fi legat in cascada cu alte 8 circuite similare asigurand astfel gestionarea si prioritizarea a 64 cereri de intrerupere;

Posibilitate de mascare individuala a cererilor;

Mai multe moduri de gestionare a intreruperilor:

Fully nested,

Rotating priority,

Special mask si

Poll.

Necesita 2 - 4 cuvinte de initializare (ICW1 - 4) si 4 cuvinte de operare (OCW1 - 4);

Genereaza vectorul de intrerupere asociat cererii luata in considerare de procesor.

60. Schema sistemului de intreruperi a PC - ului

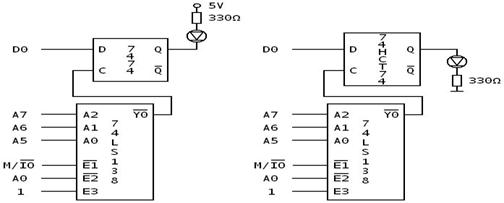

52. Prezentati 2 solutii complete pentru comanda unui LED prin program

n In solutia a s-a folosit un bistabil in tehnologie TTL, ca urmare comanda va fi in 0 (IOL = 16 mA, IOH = 0,8 mA);

n Secventa ca LED - ul sa lumineze este:

MOV AL,00H

OUT 00H,AL

n Secventa ca LED - ul sa nu lumineze este:

MOV AL,01H

OUT 00H,AL

n In varianta b bistabilul este in tehnologie HCT, ca urmare comanda se poate face fie in 0 fie in 1;

n Secventa ca LED - ul sa lumineze (comanda in 1):

MOV AL,01H

OUT 00H,AL

n Secventa ca LED - ul sa nu lumineze (comanda in 1):

MOV AL,00H

OUT 00H,AL

n Dimensionarea rezistentei (s-a considerat LED - ul rosu):

R = (5 - 1,6 - 0,2) V / 10 mA = 320 Ω, valoarea uzuala fiind 330 Ω

53. Descrieti solutiile pentru comanda prin program a unui modul de afisare cu segmente cu mai multe ranguri

n Comanda unui modul de afisare cu segmente cu mai multe ranguri:

q Solutia nemultiplexata,

q Solutia multiplexata.

n Solutia nemultiplexata:

q Cere un registru pentru fiecare rang,

q Registrele vor fi comandate ca porturi de iesire si vor memora configuratiile care se vor afisa,

q Comanda in 0 sau 1 in functie de tehnologia registrelor si de tipul de circuit afisaj (cu anod sau catod comun),

q Componenta software simpla,

q Avantaje: software simplu, usor de extins,

Dezavantaje: numar mare de circuite, numar mare de rezistente, consum mare.

n Solutia multiplexata:

q Se bazeaza pe inertia ochiului uman: imaginile care se succed cu o rata mai mare de 25 ori/ sec. dau impresia de miscare continua;

q Exista un singur registru pentru memorarea configuratiei care se va afisa, indiferent de numarul de ranguri;

q Este necesara comanda alimentarii circuitelor afisaj;

q Va exista cate un bistabil pentru fiecare rang care va comanda un tranzistor plasat pe alimentare sau pe masa in functie de tipul circuitului afisaj (cu anod sau cu catod comun);

q Componenta software va trebui sa asigure afisarea cu o rata mai mare ca 25 ori/ sec., succesiv si ciclic;

q Componenta software va trebui sa asigure concordanta intre continutul registrului si afisajul care este alimentat;

q Avantaje: minim de hardware, numar minim de rezistente, consum minim;

q Dezavantaje: software complex, utilizarea intreruperilor.

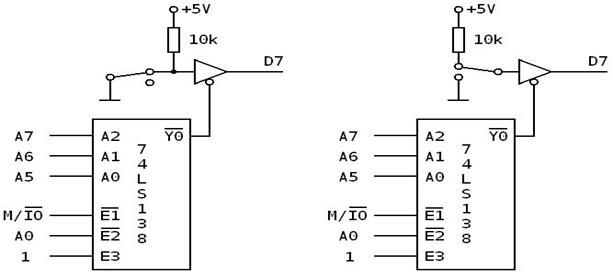

54. Prezentati solutiile complete pentru comanda prin program a unui comutator

n Solutii pentru conectarea unui comutator

a b

n Secventa pentru solutia a:

IN AL,00H

AND AL,80H

JZ SUS ; ramura corespunzatoare pozitiei din figura

; ramura corespunzatoare pozitiei contrare

n Secventa pentru solutia b:

IN AL,00H

AND AL,80H

JNZ SUS ; ramura corespunzatoare pozitiei din figura

; ramura corespunzatoare pozitiei contrare

512 Kocteti memorie fixa in zona superioara a spatiului de adrese;

256 Kocteti memorie SRAM incepind cu adresa 80000H a spatiului de adrese.

Se vor folosi circuite AM27C2048 si A616316.

|

Politica de confidentialitate |

| |

Copyright ©

2024 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |