Memoria de date de tip EEPROM

Memoria de date de tip EEPROM poate fi atit inscrisa cit si citita pe tot parcursul unei functionari normale, pentru tot domeniul admisibil al tensiunii VDD.

Acest tip de memorie nu este mapat nici in spatiun memoriei program nici in spatiul memoriei de date de tip SRAM.

Toti membrii familiei PIC16F8x au cu cite 64 de octeti de memorie de date de tip EEPROM.

Adresarea acestei memorii de tip special se realizeaza:

in domeniul de adrese de 0x00 - 0x3F;

se foloseste un mod indirect de adresare;

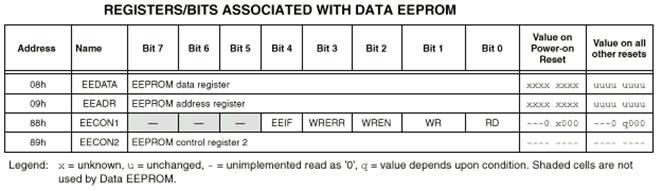

Gestionarea memoriei de date de tip EEPROM se face cu ajutorul a 4 registri cu functii speciale:

EECON1 = registru de comanda si control;

EECON2 = registru meimplementat fizic, folosit doar pe parcursul secventei de inscriere;

EEDATA = destinat pentru data pe 8 biti care urmeaza sa fie citita sau inscrisa;

EEADR = destinat pentru a pastra adresa locatiei ce se doreste a fi accesata;

Observatie: Memoria de date de tip EEPROM poate fi atit citita cit si inscrisa. In momentul inscrierii unui octet mai intii locatia respectiva este stearsa in mod automat si apoi este inscrisa.

Observatie: Ciclurile stergere / inscriere sunt scurte, durata lor fiind controlata de un timer incorporat. Timpul de inscriere variaza in functie de temperatura, de tensiunea de alimentare si, evident, de la chip la chip.

Observatie: In cazul in care este setata protectia de cod, CPU-ul poate continua sa citeasca sau sa inscrie memoria de date EEPROM. Dispozitivul de programare poate avea acces la aceasta zona de memorie.

1. Registrul de adrese EEADR

EEADR este un registru pe 8 biti cu ajutorul caruia se pot accesa pina la 256 de octeti. Familia PIC16F8x nu are implementati fizic decit primii 64 de octeti, pentru care sunt necesari pentru adresare doar cei mai putini semnificativi 6 biti ai registrului EEADR. Cei mai semnificativi 2 biti ai registrului EEADR intra si ei la codarea adreselor, ceea ce inseamna ca acestia trebuie sa fie totdeauna "0" pentru a fi siguri ca adresarea se face in spatiul primilor 64 octeti.

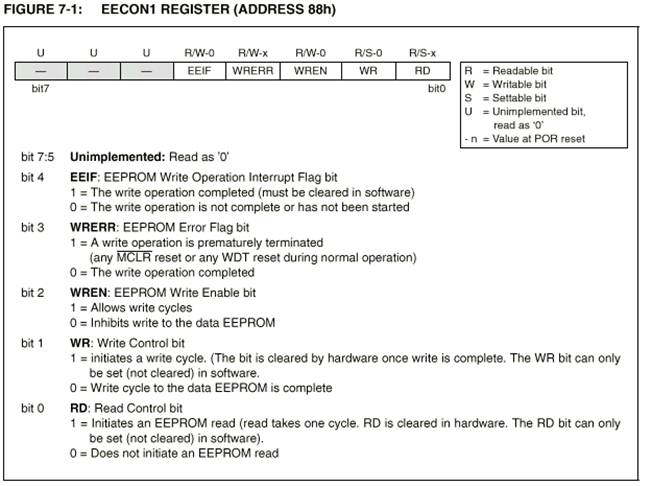

2. Registrii EECON1 si EECON2

EECON1 este un registru de control care are implementati fizic doar cei mai putin semnificativi 5 biti. Restul de 3 biti nu exista si sunt cititi ca "0".

Bitii RD si WR initializeaza operatii de citire, respectiv de inscriere. Acesti biti nu pot fi stersi ci numai setati prin program. Ei sunt resetati de catre hardware in mod automat la sfirsitul operatiilor de citire, respectiv de inscriere.

Observatie: Incapacitatea bitilor RD si WR de a fi resetati prin soft se traduce ca fiind o masura de protectie impotriva terminarii accidentale sau premature a operatiilor de citire sau de inscriere, in special.

Observatie: Bitul WREN, cind este setat, face posibila efectuarea unei operatii de inscriere. La Power-up

acest bit este resetat tocmai ca o protectie impotriva inscrierilor accidentale.

Observatie: Bitul WREER este setat cind o operatie de scriere este intrerupta datorite unui semnal de reset aplicat pe pinul MCLR sau datorita aparitiei unui reset comandat de WDT care a detectat o situatie de time-out pe parcursul unei functionari normale. In aceste situatii, dupa reset, programatorul trebuie sa verifice starea bitului WREER si daca acesta este setat, se reia ciclul de inscriere in EEPROM, tinind cont ca registrii EEDATA si EEADR ramin neschimbati.

Observatie: Flagul de intrerupere EEIF este setat numai cind ciclul de inscriere curent este terminat. Acest bit poate fi sters numai prin soft.

Registrul EECON2 nu este un registru implementat fizic. Citirea acestui registru are ca rezultat obtinerea valorii 0x00. Acest registru este folosit exclusiv numai pe parcursul secventelor de inscriere a memoriei de date de tip EEPROM.

3. Citirea din memoria de date de tip EEPROM

Pentru citirea unui singur octet de date din memoria de date de tip EEPROM, programatorul trebuie sa parcurga urmatorii pasi:

incarca adresa dorita in registrul EEADR;

seteaza bitul RD din registrul EECON1 => este initializat procesul de citire a octetului;.

data este disponibila in registrul EEDATA in ciclul imediat urmator; de unde, pe parcursul

a inca a unui ciclu, data citita din EEPROM poate fi preluata.

Observatie: Registrul EEDATA isi pastreaza nemodificat continutul pina la urmatoarea secventa de citire sau pina la urmatoarea secventa de inscriere.

Exemplu: Citirea unei date din mem. de date de tip EEPROM:

BCF STATUS, RP0 ; selectare Bank0

MOVLW Address_ ; incarca in W adresa locatiei care se doreste a fi citita

MOVWF EEADR ; incarca in EEADR adresa dorita

BSF STATUS, RP0 ; selectare Bank1

BSF EECON1, RD ; RD = "1" => initializ. operatia de citire

BCF STATUS, RP0 ; selectare Bank0

MOVF EEDATA, W ; citirea datei din EEADR si incarcarea sa in W

4. Inscrierea in memoria de date de tip EEPROM

Pentru inscrierea unui singur octet de date in memoria de date de tip EEPROM, programatorul trebuie sa parcurga urmatorii pasi:

incarca adresa dorita in registrul EEADR;

incarca data ce se doreste a fi salvata, in registrul EEDATA;

inactiveaza sistemul de intreruperi prin setarea bitului GIE din registrul INTCON;

se seteaza bitul WREN din registrul EECON1 pentru validarea inscrierilor;

secventa de initializare a operatiei de inscriere:

se incarca constanta 0x55 in EECON2;

se incarca constanta 0xAA in EECON2;

se seteaza bitul WR din registrul EECON1

Observatie: Trebuie respectata intocmai secventa specifica de initializare pentru operatiilor de inscriere in mem. de date de tip EEPROM ( se incarca 0x55 in EECON2, se incarca 0xAA in EECON2, se seteaza bitul WR ), altfel nu se realizeaza inscrierea.

Observatie: Este foarte recomandat ca sistemul de intreruperi sa fie inactivat pe parcursul secventei de initializare a unei operatii de inscriere in mem. de date de tip EEPROM.

Observatie: Secventa de initializare a operatiei de inscriere in mem. de date de tip EEPROM se repeta intocmai pentru fiecare octet in parte ce se doreste a fi inscris.

Observatie: Acest mecanism previne inscrierile accidentale in mem. de date de tip EEPROM. Programatorul trebuie sa mentina tot timpul bitul WREN in "0", in afara cazurilor in care se doreste salvarea in EEPROM.

Observatie: ATENTIE!!! Bitul WREN nu este resetat automat de catre hardwarw. Astfel , sarcina de a fi resetat cade in totalitate in sarcina programatorului.

Observatie: Dupa ce secventa de inscriere a fost initializata, stergerea bitului WREN nu afecteaza cu nimic ciclul de inscriere.

Observatie: Daca bitul WREN nu este setat atunci numai prin setarea bitului WR nu se va initializa nici un ciclu de inscriere.

Observatie: La sfirsitul unui ciclu complet de inscriere, bitul WR este resetat automat de catre hardware iar flagul de intreruperi EEIF este setat automat de catre hardware.

Observatie: Flagul de intrerupere EEIF ( EE Write Complete Interrupt Flag ) poate fi activat pentru a se genera o cerere de intrerupere la sfirsitul fiecarui ciclu complet de inscriere. Acest flag poate fi resetat numai prin program.

Observatie: Programatorul poate sa nu activeze aceasta intrerupere si sa implementeze o bucla de pooling pentru a determina starea flagului EEIF in vederea salvarii in EEPROM a datelor dorite.

Exemplu:

BCF STATUS, RP0 ; selectare Bank0

MOVLW Address_ ; incarca in W adresa dorita

MOVWF EEADR ; incarca in EEADR adresa dorita

MOVLW Data_ ; incarca in W data dorita

MOVWF EEDATA ; incarca in EEDATA data dorita

BSF STATUS, RP0 ; selectare Bank1

BCF INTCON, GIE ; invalidare sistem intreruperi

BSF EECON1, WREN ; validare operatiilor de inscriere

MOVLW 0x55 ; incarca in W constanta 0x55

MOVWF EECON2 ; incarca in EECON2 constanta 0x55

MOVLW 0xAA ; incarca in W constanta 0xAA

MOVWF EECON2 ; incarca in EECON2 constanta 0xAA

BSF EECON1, WR ; WR = "1" => initializ. operatia de inscriere

BSF INTCON, GIE ; revalidare sistem intreruperi

5. Verificarea datelor inscrise in mem. de date de tip EEPROM

In functie de aplicatie, de multe ori este necesara verificarea datelor salvate in memoria de date de tip EEPROM.

Exemplu: Verificarea datelor inscrise in mem. de date de tip EEPROM:

============================

secventa de inscriere prezentata mai sus

============================

; registrul EEDATA inca mai pastreaza valorea ce a fost inscrisa si care trebuie verificata

============================

; incarca in W data care tocmai a fost inscrisa

BCF STATUS, RP0 ; selectare Bank0

MOVF EEDATA, W

============================

; registrul EEADR inca mai pastreaza adresa la care s-a efectuat inscrierea si de unde

; trebuie efectuata o citire in vederea verificarii

============================

; efectuarea citirii pentru verificare

BSF STATUS, RP0 ; selectare Bank1

BSF EECON1, RD ; RD = "1" => init. citirea de verif.

; rezultatul citirii de verificare este deja in registrul EEDATA

============================

BCF STATUS, RP0 ; selectare Bank0

SUBWF EEDATA, W ; scade continutul lui W din EEDATA si pastreaza

; rwezultatul in W

============================

BTFSS STATUS, Z ; testeaza rezultatul scaderii

daca Z = 1, => rezultatul operatiei de scadere este zero, adica valoarea inscrisa este egala cu

; valoarea rezultata din citirea pentru verificare => se sare peste instructiunea GOTO si se

; continua in mod firesc programul

daca Z != 0 => rezultatul operatiei de scadere NU este zero, adica valoarea inscrisa

; NU este egala cu valoarea rezultata din citirea pentru verificare => se executa instr. GOTO

GOTO ` WRITER_ERROR ; salt spre rutina de tratare a erorilor de inscriere

============================

; continuarea programului

6. Protectia impotriva inscrierilor accidentale in mem. de date de tip EEPROM

Exista conditii extreme care ar favoriza inscriei accidentale. Exista conditii in care dispozitivul nu trebuie sa execute inscrieri ( in mem. de date de tip EEPROM ).

Din aceste motive s-au implementat diferite mecanisme interne care au rolul de a impiedica realizarea unor inscriei false. Acestea sunt:

la power-up bitul WREN este sters;

Power-Up Timer care asigura o temporizare de 72 ms la punerea sub tensiune;

necesitatea parcurgerii secventei de initializare a unei operatii de inscriere;

In acest fel se face practic imposibila intrunirea aleatoare a tuturor conditiilor de inscriere, adica aceste mecanisme fac imposibila aparitia unor inscrieri false chiar in conditiile cele mai defavorabile de functionare ( brown-out, power glitch, software malfunction, ..etc. )

Accesul la mem. de date de tip EEPROM in conditiile setarii protectiei asupra codului

Chiar daca este setata protectia impotrina citirii din exterior a codului, CPU-ul este capabile in continuare sa citeasca sau sa inscrie date din / in memoria de date de tip EEPROM.

Pentru variantele de dispozitive prevazute cu ROM exista 2 biti pentru protectia codului.

Unul pentru protectia ROM-ului iar altul pentru protectia EEPROM-ului

|

Politica de confidentialitate |

| Copyright ©

2024 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |