Timer-ul si registrul TMR0

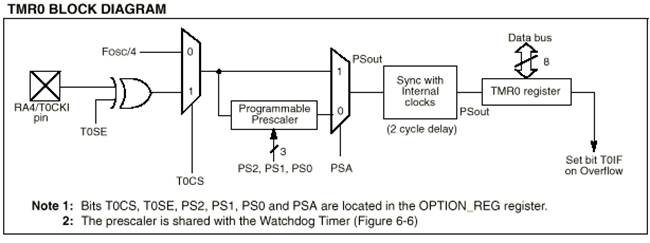

Blocul Timer0 are urmatoarele facilitati:

doua moduri de functionare: timer sau counter pe 8 biti;

registrul TMR0 poate fi atit citit cit si inscris;

prescaler pe 8 biti selectabil si programabil soft;

ofera posibilitatea de selectare a sursei de clk ( interna sau externa );

ofera posibilitatea de generare a unei cereri de intrerupere la depasire ( la trecerea de la

valoarea 0xFF la 0x00 );

ofera posibilitatea de selectare a frontului activ pentru sursa de clk externa ( fie pe

front ridicator fie pe front cazator );

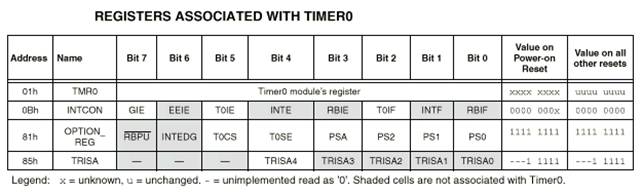

Observetie: Registrele asociate cu configurarea si functionarea modulului Timer0 sunt in numar de 4 si sunt prezentate mai jos sub forma unui tabel.

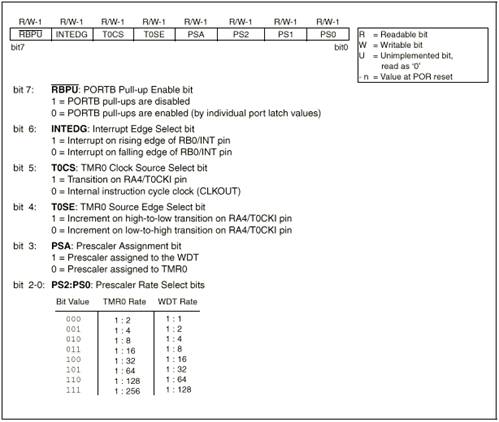

Observetie: Registrul OPTION_REG contine toti bitii de configurare pentru Timer0. De aceea il vom prezenta din nou pe scurt.

Observatie: Cele doua moduri de functionare ( timer sau counter ) sunt stabilite cu ajutorul bit-ului T0CS:

T0CS = "1" => este selectata sursa externe de clk, deci Timer0 functioneaza ca numarator de

evenimente ( counter );

T0CS = "0" => este selectata sursa externe de clk, deci Timer0 functioneaza ca temporizator

( timer);

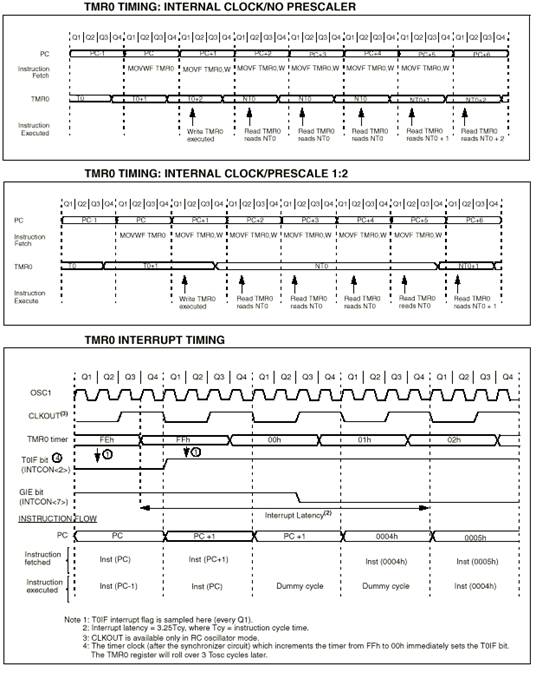

Observatie: In modul de operare timer, Timer0 este incrementat la fiecare ciclu instructiune, fara sa fie folosit si prescaler-ul.

Observatie: Daca registrul TMR0 este inscris, atunci incrementarea este inhibata pe parcursul urmatoarelor doua cicluri. Programatorul poate compensa acesta intirziere a incremantarii prin incarcarea in registrul TMR0 a unei valoari ajustate corespunzator.

Observatie: In modul de operare counter, Timer0 este incrementat ori pe frontul ridicator ori pe frontul cazator ( in functie de valoarea bitului T0SE ) al semnalului aplicat pe pinul RA4 / T0CKI, in acest caz putind fi folosit si prescaler-ul, al carui factor de divizare poate fi stabilit prin soft.

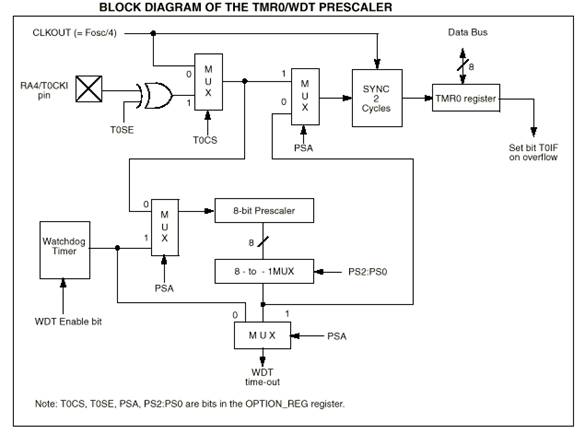

Observatie: Prescaler-ul poate fi utilizat, la un moment dat, fie de catre Timer0, fie de catre Watchdog Timer. Aceasta se stabileste cu ajutorul bitului PSA din cadrul registrului OPTION_REG ( vezi mai sus ).

Observatie: Prescaler-ul nu poate fi nici citit, nici inscris.

Observatie: Cind prescaler-ul este selectat sa deserveasca pe Timer0, atunci factorul sau de divizare poate fi programat ( 1:2, 1:4,., 1:256 ) cu ajutorul bitilor PS2, PS1, PS0 din cadrul registrului OPTION_REG

( vezi mai sus ).

1. Generarea cererilor de intreruperi de catre Timer0

Timer0 genereaza o cerere de intrerupere cind se realizeaza o depasire, adica cind se sesizeaza o trecere de la valoarea 0xFF la 0x00.

Observatie: In momentul detectiei depasirii este setat flag-ul de intreruperi T0IF din INTCON..

Observatie: Aceasta intrerupere poate fi validata ( TOIE = "1" ) sau invalidata ( TOIE = "0" ) ( mascata ) cu ajutorul bitului T0IE din INTCON.

Observatie: Flagul T0IF trebuie resetat prin soft la sfirsitul rutinei de deservire dar inainte de validarea acestei linii de cerere de intreruperi.

Observatie: Acest tip de intrerupere nu poate apare si deci nu poate activa microcontrolerul daca acesta este in modul SLEEP. Aceasta deoarece in acest mod functionarea lui Timer0 este suspendata.

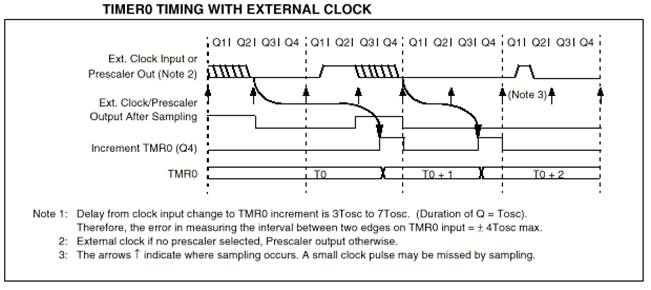

2. Utilizarea lui Timer0 cu sursa de clk externa

In cazul folosirii unui semnal extern pentru Timer0, acesta trebuie sa satisfaca anumite necesitati.

Acestea se datoreaza modului intern de sincronizare. De asemenea aici se intilneste o intirziere la incrementarea registrului TMR0 dupa sincronizare.

2.1. Sincronizarea sursei de clk externe

Cind nu este folosit prescaler-ul, semnalul de clk extern (T0CKl ) este direct aplicat spre TMR0. Sincronizarea semnalului de clk extern cu "internal phase clock" este realizata prin esantionarea sa pe parcursul ciclilor Q2 si Q4.

De aceea este necesar ca semnalul aplicat pe pinul RA4 / T0CKI sa aiba urmatoarele caracteristici:

sa fie in "1" cel putin 2*TOSC plus o mica intirziere RC;

cs fie in "0" cel putin 2*TOSC plus o mica intirziere RC;

Cind este folosit prescaler-ul ( care este un numarator asincron ), semnalul aplicat pe pinul RA4 / T0CKI este divizat. Astfel, pe iesirea prescaler-ului se obtine un semnal simetric ( cu factorul de umplere ½ ). In aceste conditii, pentru determinarea caracteristicilor necesare semnalului de clk extern ( T0CKl ), trebuie luat in calcul si prescaler-ul. De aceea este necesar ca semnalul T0CKl sa aiba o perioada de cel putin 4*TOSC plus o mica intirziere RC. Astfe; in acest caz, singura conditie ce trebuie satisfacuta de semnalul T0CKl este ca acesta sa nu aiba perioada mai mica de 10ns ( valoarea minima admisibila ).

2.2. Intirzierea la incrementarea registrului TMR0

Din cauza ca iesirea prescaler-ului este sincronizata cu clk-urile interne ( Q1, Q2, Q3, Q4 ), totdeauna va exista o mica intirziere intre momentul aparitiei frontului activ al semnalului T0CKl si momentul cind registrul TMR0 este incrementat. Acest lucru poate fi observat in diagrama cu formele de unda de mai sus.

3. Prescaler-ul

Exista un bloc de numarare asincron pe 8 biti ce indeplineste functia de divizor de frecventa si poate indeplini doua roluri distincte:

prescaler pentru modulul Timer0;

postscaler pentru Watchdog Timer;

Observatie: Acest bloc de numarare pe 8 biti poate indeplini, la un moment dat, numai unul dintre aceste roluri.

Observatie: Acest bloc de numarare poate fi complet configurat prin soft cu ajutorul urmatorilor biti continuti de registrul OPTION_REG:

PSA ( Prescaler Assigment bit ): - PSA = 1 => configurat ca postscaler pentru WDT;

- PSA = 0 => configurat ca prescaler pentru Timer0

PS2, PS1, PS0 ( Prescaler Rate Select bits ):

Observatie: Daca blocul de numarare / divizare este configurat sa functioneze ca prescaler pentru modulul Timer0, atunci toate instructiunile care executa o operatie de inscriere asupra modulului Timer0

( de exemplu: CLRF 1, MOVWF 1, BSF 1, x,.., etc. ) vor reseta prescaler-ul.

Observatie: Daca blocul de numarare / divizare este configurat sa functioneze ca postscaler pentru WDT, atunci instructiunea CLRWDT va reseta prescaler-ul impreuna cu WDT.

Observatie: Fie ca este configurat ca prescaler sau ca postscaler, blocul de numarare nu poate fi nici citit nici inscris.

3.1. Comutarea intre configuratia de prescaler si postscaler

Cum am vazut, configuratia de prescaler sau de postscaler se stabileste prin soft. Aceasta facilitate ofera posibilitarea ca modificarea configuratiei sa se poata face "din zbor".

Observatie: Pentru a se evita un RESET accidental al dispozitivului pe durata schimbarii configuratiei de prescaler in cea postscaler, trebuie executata o anumita secventa de cod, secvanta ce este prezentate mai jos. Aceasta secventa trebuie executata chiar daca WDT este inactivat.

Exemplu: Schimbarea configuratiei: prescaler ( Timer0 ) == postscaler ( WDT ):

BCF STATUS, RP0 ; selectie Bank0

CLRF TMR0 ; sterge registrul TMR0 si prescaler-ul

BSF STATUS, RP0 ; selectie Bank1

CLRWDT ; sterge registrul WDT

MOVLW b'xxxx1xxx' ; incarca in W const. de config. destin. pentru OPTION_REG

MOVWF OPTION_REG ; seteaza PSA = "1" => setare config. de postscaler

BCF STATUS, RP0 ; selectie Bank0

Exemplu: Schimbarea configuratiei: postscaler ( WDT ) == prescaler ( Timer0 ):

CLRWDT ; sterge registrul WD si postscaler-ul

BSF STATUS, RP0 ; selectie Bank1

MOVLW b'xxxx0xxx' ; incarca in W const. de config. destin. pentru OPTION_REG

MOVWF OPTION_REG ; seteaza PSA = "0" => setare config. de prescaler si

; selectie sursa de clk

BCF STATUS, RP0 ; selectie Bank0

|

Politica de confidentialitate |

| Copyright ©

2026 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |