PIC16F84A apartine domeniului de mijloc a microcontrolerelor PICmicro. Diagrama bloc a acestui dispozitiv este prezentata in Fig.1 .

Fig. 1

Memoria de program contine 1024 (1Kb) cuvinte ce corespund la 1024 instructiuni, fiecare instructiune are o lungime de 14 biti exact cit lungimea cuvintului memoriei de program. Memoria de date de tip RAM static contine 68 de octeti si memoria de date de tip EEPROM contine 64 octeti.

Exista deasmenea 13 pini de intrare/iesire care pot fi configurati de catre utilizator. Unii pini sunt multiplexati cu alte functii ale dispozitivului. Aceste functii sunt:

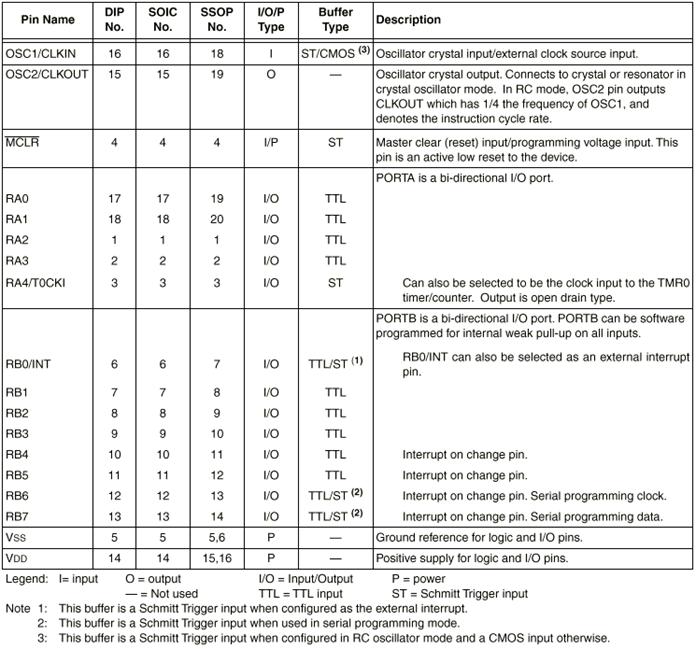

In Tabelul 1 sunt prezentate in detaliu functiile pinilor.

Tabelul 1

PIC 16F84A are doua blocuri de memorie: Memoria de Program, Memoria de Date. Fiecare bloc de memorie are cite un bus propriu astfel incit accesul la oricare bloc poate apare simultan cu accesul la celalalt bloc in timpul aceluiasi ciclu al masinii.

In blocul memoriei de date este continuta si memoria de tip EEPROM. Aceasta memorie nu poate fi accesata direct ca si memoria de tip static RAM ci indirect. Un pointer indirect de adresa specifica adresa memoriei de date EEPROM pentru scriere/citire. Cei 64 octeti de memorie EEPROM au domeniul de adrese 00h-3Fh. Detalii suplimentare despre memoria EEPROM pot fi gasite in Sectiunea 5.0.

PIC16FXX are un Program Counter pe 13 biti capabil sa adreseze pina la 8K x 14 spatiu memorie de program. Pentru PIC 16F84A sunt implementati fizic primii 1K X 14 (0000h-03FFh). Accesul locatiilor peste adesele fizice implementate se face tot in spatiul implementat fizic, ca si cum aceleasi locatii fizice se gasesc la mai multe adrese de memorie. De exemplu la adresele 20h, 420h, 820h, C20h, 1020h, 1420h, 1820h si 1C20h se va gasi aceeasi instructiune. Adresa accesata dupa Reset este 0000h iar adresa vectorului de intrerupere este 0004h.

Fig. 2

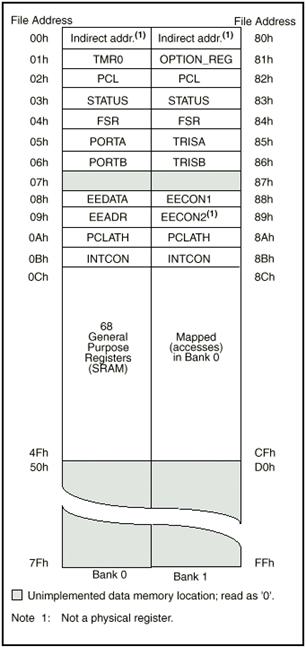

Memoria de date este impartita in doua zone. Prima este zona SFR (Special Function Registers - Registri cu Functii Speciale) iar a doua este zona GPR (General Purpose Registers - Registri cu Scop General). SFR controleaza operatiile dispozitivului.

Portiuni din Memoria de Date sunt impartite in bacuri (valabil pentru SFR cit si pentru GPR). Zona GPR este impartita in bancuri pentru a permite mai mult decit 116 octeti de RAM cu scop general. Bancurile zonei SFR sunt pentru registrii care controleaza functiile perifericelor. Pentru a selecta un anumit banc este nevoie de niste biti de selectie. Acesti biti de control se gasesc in Registrul de STARE (Status Register). In figura de mai jos este prezentata organizarea Memoriei de Date.

Fig. 3

Intreaga Memorie de Date poate fi accesata direct (folosind adresarea absoluta a fiecarui registru) sau indirect (prin registrul FSR - File Select Register). Adresarea indirecta foloseste valoarea curenta a bitului RP0 pentru a accesa in interiorul bancului de Memorie de Date.

Memoria de date este impartita in doua bancuri: SFR si GPR. Bancul 0 este selectat prin stergerea bitului RP0 (STATUS<5>). Setarea bitului RP0 va duce la selectia bancului 1. Fiecare banc se intinde pina la adresa 7Fh (128 octeti). Primele 12 locatii a fiecarui banc sunt rezervate pentru SFR. Zona ramasa este GPR implementata ca si RAM static.

SFR sunt folositi de catre CPU si Functiile Perifericelor pentru a controla operatiile dispozitivului. Acesti registri sunt RAM static. SFR pot fi clasificati in doua seturi: nucleu, periferic. In continuare sunt descrisi registii care tin de nucleul microcontrolerului urmind ca in continuare sa fie prezentati cei asociati functiilor periferice.

Tabelul 1: Sumar al

registrilor SFR

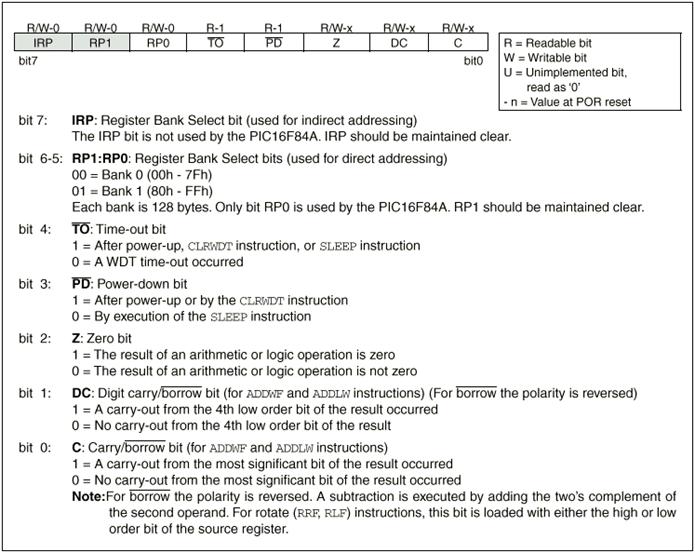

Registrul de Stare contine date despre starea aritmetica a ALU, starea RESET si bitul de selectie a bancului de memorie de date. El poate fi destinatia unei instructiuni, caz in care daca instructiunea afecteaza bitii Z, DC sau C scrierea lor este dezactivata. Acesti biti sunt stersi sau setati conform cu dispozitivul logic. Mai mult, bitii /TO si /PD nu pot fi scrisi. Rezultatul unei instructiuni cu destinatie Registrul de Stare poate fi diferit fata de ce ne-am astepta.

De exemplu, CLRF STATUS va sterge cei mai semnificativi trei biti dar va seta bitul Z. Dupa aceasta registrul de Stare va fi 000u u1uu (unde u=neschimbat). Pentru a modifica Registrul de Stare pot fi folosite doar instructiunile BCF, BSF, SWAPF si MOVWF deoarece acesti biti nu afecteaza nici un bit de stare.

Fig. 5 : Registrul de Stare (Adresa 03h, 83h)

Nota 1: Bitii IRP si RP1 (STATUS<7:6>) nu sunt folositi de PIC16F84A. Nu este recomandata folosirea acestor biti ca biti cu scop general pentru a nu afecta compatibilitatea cu produsele viitoare.

Nota 2: Bitii C si DC reflecta si aparitia imprumutului in cazul operatiei de scadere. Pentru exemplificare vezi instructiunile SUBLW si SUBWF.

Acest registru poate fi scris sau citit si contine diferiti biti de control pentru configurarea divizorului TMR0/WDT, a intreruperii externe INT, TMR0 si tipul de iesire a portului PORTB.

Fig. 6 : Registrul

Optiune (Adresa 81h)

Nota : Cind divizorul este asociat cu WDT (Watchdog Timer - PSA='1'), TMR0 are asociata divizarea 1:1.

Registrul INTCON poate fi citit sau scris si contine diferiti biti de validare a tuturor surselor de intrerupere.

Fig. 7 Registrul

INTCON (Adresa 0Bh, 8Bh)

Registrul Program Counter (PC) specifica adresa instructiunii de extras pentru a fi executata. PC este pe 13 biti. Octetul inferior al PC (PC<7:0>) este denumit PCL. Acest registru poate fi citit sau scris. Partea superioara a PC (PC<12:8>) este denumita PCH. Acest registru nu poate fi citit sau scris direct. Orice schimbare asupra lui PCH se face prin registrul PCLATH.

Stiva permite o combinatie de pina la 8 apeluri de program si intreruperi. Ea contine adresa de intoarcere din ramificatiile aparute in executia programului.

Dispozitivele ca PIC16F84A au o stiva hardware cu 8 nivele (un nivel = 13 biti). Stiva nu este parte a vreunei zone de memorie iar pointerul stivei nu poate fi citit sau scris. Registrul PC este salvat in stiva la o instructiune CALL sau la aparitia unei intreruperi. La executia unei instructiuni RETURN, RETLW sau RETFIE registrul PC este incarcat cu cuvintul din virful stivei. Registrul PCLATH nu este modificat cind dispozitivul lucreaza cu stiva.

Dupa ce s-a salvat de 8 ori in stiva, a noua salvare va rescrie valoarea salvata prima data. Inca o adaugare in stiva va rescrie a doua salvare in stiva, si asa mai departe. Deducem ca stiva este circulara.

Registrul INDF nu este un registru fizic. Adresind INDF de fapt se adreseaza registrul a carui adresa este continuta in registrul FSR (FSR este un pointer). Acest mecanism reprezinta adresarea indirecta.

Exemplul 1 : ADRESAREA INDIRECTA

Citirea indirecta a registrului INDF insusi (FSR=0) va intoarce valoarea 00h. Scrierea indirecta a registrului INDF este o non-operatie (desi registrul STATUS ar putea fi afectat).

In exemplul urmator este prezentat un program simplu de stergere a locatiilor 20h-2Fh folosind adresarea indirecta.

Exemplul 2 : Cum sa stergi RAM-ul folosind adresarea indirecta

O adresa efectiva pe 9 biti este obtinuta prin concatenarea registrului FSR (8 biti) cu bitul IRP (STATUS<7>) asa cum este aratat in figura de mai jos. Oricum, bitul IRP nu este folosit de PIC 16F84A.

Fig. 8 : Adresarea directa/indirecta

Unii pini ai acestor porturi de intrare sunt multiplexati cu functiii alternative. In general daca un periferic este valid pinul corespunzator nu ar putea fi folosit ca pin de intrare/iesire de uz general.

PORTA este un port bidirectional pe 5 biti. TRISA este registrul corespunzator pentru directia datelor. Setind un bit TRISA (=1) vom initializa pinul corespunzator din PORTA ca intrare, iar driver-ul corespunzator in modul inalta-impedanta. Stergind un bit TRISA (=0) vom initializa pinul corespunzator din PORTA ca iesire, punind continutul latch-ului de iesire la pinul selectat.

Nota: La Reset-ul de dupa alimentare toti pinii de intrare/iesire sunt conigurati ca iesire.

La citirea registrului PORTA se citeste de fapt starea pinilor, in timp ce scrierea lor va scrie in latcch-ul de iesire. Toate operatiile de scriere sunt operatii citeste-modifica-scrie. Deci o scriere la un port implica faptul ca pinul este citit, valoarea lui este modificata , apoi se face scrierea in latch-ul de date.

Fig. 1 Diagrama bloc a pinilor RA3:RA0

Pinul RA4 este multiplexat cu intrarea de clock a modulului Timer0 devenind pinul RA4/T0CKI. Acest pin este o intrare Trigger-Schmitt si iesire open-drain. Toti ceilalti pini RA au nivele de intrare TTL si driver de iesire CMOS.

Fig. 1 Diagrama bloc a pinului RA4

Exemplul 3 : Initializarea portului PORTA

Tabelul 3 : Functiile portului PORTA

Tabelul 3 : Registri asociati portului PORTA

PORTB este un port bidirectional pe 8 biti. TRISB este registrul corespunzator pentru directia datelor. Setind un bit TRISB (=1) vom initializa pinul corespunzator din PORTB ca intrare, iar driver-ul corespunzator in modul inalta-impedanta. Stergind un bit TRISB (=0) vom initializa pinul corespunzator din PORTB ca iesire, punind continutul latch-ului de iesire la pinul selectat.

Exemplul 4 : Initializarea portului PORTB

Fiecare pin al portului PORTB are o mica rezistenta interna conectata la VDD. Exista niste biti de control care pot activa sau dezactiva aceste rezistente interne, Activarea se poate face prin stergerea bitului /RBPU (OPTION<7>). Daca portul PORTB este configurat ca iesire aceste rezistente sunt dezactivate automat. La Reset-ul de dupa alimentare rezistentele sunt dezactivate.

Patru din pinii portului PORTB, RB7:RB4, au facilitatea de a produce o intrerupere la schimbarea starii lor. Numai bitii configurati ca intrari pot produce intrerupere (oricare din pinii RB7:RB4 configurati ca iesiri sunt exclusi de la compararea pentru detectarea schimbarii starii). Pinii configurati ca intrari (dintre RB7:RB4) sunt comparati cu veche valoare a lor din latch memorata la ultima citire a portului PORTB. Orice modificare a starii pinilor RB7:RB4 poate duce la activarea bitului RBIF - RB Interrupt Flag (INTCON<0>).

Aceasta intrerupere poate activa dispozitivul din starea SLEEP. Utilizatorul

poarte sterge intreruperea in rutina de tratare a intreruperii in doua feluri:

a) Orice citire/scriere a portului PORTB.

b) Stergerea bitului flag RBIF

O schimbare a starii PORTB va duce la setarea in continuare a flag-ului RBIF. Citirea portului PORTB va sirsi conditia de intrerupere permitind stergerea bitului RBIF.

Facilitateade intrerupere la schimbare a portului PORTB este recomandata pentru activarea circuitului la o operatie de apasare a unei taste si operatii in care portul PORTB este folosit doar pentru aceasta acilitate. ? ? ?????

Fig. 3 Diagrama bloc a pinilor RB7:RB4

Fig. 3 Diagrama bloc a pinilor RB3:RB0

Tabelul 4 : Functiile portului PORTB

Tabelul 4 : Registri asociati portului PORTB

Moduulul Timer0 are urmatoarele facilitati:

In figura de mai jos este prezentata o diagrama bloc simplificata a modulului Timer0.

Fig. 1 Diagrama bloc

a modulului Timer0

Timer0 poate functiona ca timer sau counter (numarator de evenimente). Modul de lucru Timer este selectat prin stergerea bitului T0CS (OPTION_REG<5>). In modul timer incrementarea se va face la fiecare ciclu instructiune (fara divizor). Daca registrul TMR0 este scris incrementarea este inhibata pentru urmatoarele doua cicluri instructiune. Utilizatorul va trebui sa tina seama de aceasta cind calculeaza valoarea care va trebui incarcata in registrul TMR0.

Modul counter este selectat prin setarea bitului T0CS (OPTION_REG<5>). In modul counter incrementarea se va face la iecare front crescator sau descrescator al pinului RA4/T0CKI. Tipul frontului de incrementare este determinat de bitul T0SE - Timer0 Source Edge Select (OPTION_REG<4>). Stergerea bitului T0SE va selecta tipul de front crescator. Mai jos sunt tratate restrictiiile asupra intrarii semnalului de clock extern.

Cind se foloseste intrarea de clock extern pentru Timer0, acesta trebuie sa indeplineasca anumite cerinte. Cerintele asigura clock-ul extern ca poate fi sincronizat cu faza clock-ului intern (Tosc). Deasemeni , exista o intirziere la incrementarea Timer0 dupa sincronizare. Informatii suplimentare referitoare la cerintele clock-ului extern se gasesc in PICmicro Mid-Range Reference Manual, (DS33023).

Un counter pe 8 biti este disponibil ca divizor pentru modulul Timer0 sau pentru Watchdog Timer.

Fig. 2 Diagrama bloc

a divizorului Timer0/WDT

Exista un singur divizor disponibil care este folosit ori de catre modulul

Timer0 ori de catre WDT. Asocierea divizorului cu modulul Timer0 inseamna ca nu

mai este disponibil nici un alt divizor pentru WDT si vice-versa.

Divizorul nu poate fi citit sau scris.

Bitii PSA si PS2:PS0 (OPTION_REG<3:0>) stabilesc cu ce modul este asociat

divizorul cit si raportul de divizare 1:2, 1:4, , 1:256.

Prin stergerea bitului PSA vom asocia divizorul modulului Timer0. In acest

caz valorile de divizare pot fi 1:2, 1:4, , 1:128.

Prin setarea bitului PSA vom asocia divizorul modulului Watchdog Timer (WDT).

In acest caz valorile de divizare pot fi 1:1, 1:2, , 1:128.

Cind divizorul este asociat modulului Timer0 toate instructiunile care scriu

registrul TMR0 (CLRF 1, MOVWF 1, BSF 1,x etc.) vor sterge divizorul. In

cazul cind divizorul este asociat cu WDT, instructiunea CLRWDT va sterge

divizorul inainte de a sterge WDT.

Nota: Scrierea registrului TMR) cind are divizorul asociat va sterge valoarea

divizorului dar nu va schimba asocierea acestuia.

Asocierea divizorului poate fi facuta doar prin software, deci poate fi

schimbata in timpul executiei unui program.

Nota: Pentru a preveni Reset-area neintentionata a dispozitivului trebuie

executata o anumita secventa de instructiuni (arata in PICmicro Mid-Range

Reference Manual,DS3023) cind se doreste schimbarea asocierii divizorului de la

Timer0 la WDT. Aceste instructiuni trebuiesc executate chiar daca WDT este

dezactivat.

Intreruperea TMR0 este generata la trecerea registrului TMR0 din starea cu valoarea FFh la starea cu valoarea 00h. Aceasta depasire seteaza bitul T0IF (INTCON<5>). Bitul T0IF trebuie sters prin software in rutina de tratare a intreruperii corespunzatoare inainte de revalidarea intreruperii. Intreruperea TMR0 nu poate activa procesorul din modul SLEEP din moment ce timer-ul este inchis in timpul modului SLEEP.

Tabelul 1: Registri

asociati cu Timer0

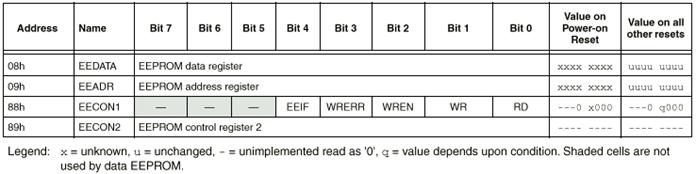

Memoria de date de tip EEPROM poate fi scrisa sau citita in timpul unei operatii normale (domeniul VDD complet). Acesta nu este mapata direct in spatiul de memorie. In schimb ea este adresata prin Registri cu Functii Speciale (SFR). Sunt folositi patru registri pentru a scie sau citi aceast tip de memorie.Acesti registri sunt:

Registrul EEDATA contine cei 8 biti de date ce trebuie scrisi/cititi iar registrul EEADR contine adresa locatiei de memorie EEPROM ce este accesata. Dispozitivul 16F84A are 64 octeti de date de tip EEPROM aflat in domeniul de adrese 00h-3Fh. Memoria de date EEPROM permite scrierea si citirea de octeti. Scrierea unui octet sterge automat locatia de memorie si scrie noua valoare (stergere inainte de scriere). Memoria de date EEPROM permite cicli stergere/scriere de viteza mare. Timpul de scriere este controlat de catre un timer intern. Timpul de scriere variaza cu tensiunea si temperatura precum si de la chip la chip. In specificatiile AC puteti gasi date exacte de spre ciclii de scriere/citire a memoriei de date EEPROM.

Cind dispozitivul are codul protejat CPU ar putea continua citire si scrierea memoriei EEPROM. Informatii suplimentare despre Data EEPROM se pot gasi in PICmicro Mid-Range Reference Manual, (DS33023).

Fig. 1 Registrul

EECON (Adresa 88h)

Pentru a citi o locatie din memoria de date de tip EEPROM utilizatorul trebuie sa scrie adresa in registrul EEADR si apoi sa seteze bitul de control RD (EECON<0>). Data va fi valida in cel mai apropiat ciclu urmator in registrul EEDATA; deci el poate fi citit in urmatoarea instructiune. Registrul EEDATA va contine aceasta valoare pina la o alta citire sau pina cind va fi scris de utilizator (intr-o operatie de scriere).

Exemplul 5-1 : Citire data din memoria EEPROM

Pentru a scrie o locatie din memoria de date de tip EEPROM utilizatorul trebuie mai intii sa scrie adresa in registrul EEADR si apoi data in registrul EEDATA. Apoi utilizatorul trebuie sa urmeze o secventa specifica de initalizare a scrierii fiecarui octet.

Exemplul 5-2 : Scriere data in memoria EEPROM

Scrierea nu va avea loc daca secventa de instructiuni de mai sus nu este urmata intocmai (scrie 55h in EECON2, scrie AAh in EECON2, apoi seteaza bitul WR) pentru fiecare octet in parte. Se recomanda ca intreruperile sa fie neaparat dezactivate in timpul executiei acestui segment de cod. In plus, bitul WREN din EECON1 trebuie setat pentru a valida scrierea. Acest mecanism previne scrierea accidentala in EEPROM datorat executiei unui cod necorespunzator. Utilizatorul trebuie sa mentina bitul WREN sterstot timpul, exceptind cazul cind se scrie in EEPROM. Bitul WREN nu este sters hardware.

Dupa ce a fost inceputa o secventa de scriere stergerea bitului WREN nu va afecta ciclul de scriere curent. Bitul WR va fi inhibat din starea setat mai putin in cazul cind bitul WREN este setat.

La sfirsitul ciclului de scriere bitul WR este sters prin hardware iar bitul EEIF (EE write complet Interrupt Flag) este setat. Utilizatorul poate valida sau nu aceasta intrerupere.????? Bitul EEIF trebuie sters prin software.

Depinzind de aplicatie, din practica se recomanda ca data ce este scrisa in EEPROM ar trebui sa fie apoi verificata daca a fost scrisa corect. Aceasta verificare trebuie folosita in aplicatii in care EEPROM-ul este constrins sa lucreze in apropierea situatiilor de limita. In general, eroarea de scriere a EEPROM-ului va fi atunci cind a fost scris un '0' dar citit ca '1' (datorat fluctuatiilor de bit????).

Exemplul 5-3 : Verificarea Scrierii

Tabelul 5-1 : Registri/Biti asociati cu memoria EEPROM

Ceea ce face ca un microcontroler sa difere de alte procesoare sunt tocmai circuitele sale speciale necesare la tratarea unor aplicatii de timp real. PIC 16F84A are aceste facilitati cu scopul de a maximiza siguranta sistemului, minimizind costurile prin eliminarea componentelor externe, furnizind moduri de lucru cu consum redus de putere cit si protectie asupra codului. Aceste facilitati sunt:

PIC16F84A are un Watchdog Timer care poate fi inchis numai prin bitii de configurare. El isi inchide propriul sau oscilator RC pentru marirea sigurantei. Exista doua timere care realizeaza intirzierile necesare la alimentare. Unul este Oscillator Start-up Timer (OST), cu rolul de a mentine circuitul in Reset pina cind oscilatorul cu cristal se stabilizeaza. Celalalt este Power-up Timer (PWRT) care furnizeaza o intirziere de exact 72ms doar la alimentare. Acest model tine dispozitivul in Reset cit timp sursa de alimentare se stabilizeaza. Cu aceste doua timere incluse in chip cele mai multe aplicatii nu au nevoie de circuite externe de Reset.

Modul SLEEP ofera um mod de lucru cu consum foarte redus de putere.

Utilizatorul poate activa circuitul din stara SLEEP prin Reset extern, Watchdog

Timer sau intrerupere. Mai multe optiuni pentru oscilator permit adaptarea cu

aplicatia. Optiunea de oscilator RC micsoreaza costul sistemului in timp ce

optiunea cristal LP micsoreaza consumul de putere. Un set de biti de

configurare sunt folositi pentru a selecta diferite optiuni.

Informatii suplimentare despre facilitatile speciale se gasesc in PICmicro

Mid-Range Reference Manual (DS33023).

Bitii de configurare pot fi programati (cititi ca '0') sau lasati neprogramati (cititi ca '1') pentru a selecta diferite configuratii ale dispozitivului. Acesti biti se gasesc im memoria de program la adresa 2007h. Adresa 2007h este peste spatiul memoriei de program accesibila utilizatorului si apartine zonei de memorie de test/configurare (2000-3FFFh). Acest spatiu poate fi accesat doar in timpul programarii.

Fig. 6-1 : Cuvintul de configurare - PIC16F84A

PIC16F84A poate opera in patru moduri de oscilator diferite. Utilizatorul poate programa doi biti de configurare (FOSC1 si FOSC0) pentru a selecta unul din urmatoarele patru moduri.

In modurile XT, LP sau HS un rezonator cu cristal sau ceramic este conectat

la pinii OSC1/CLKIN si OSC2/CLKOUT pentru a realiza oscilatia (Fig. 6-2).

Fig. 6-2 : Rezonator cristal/ceramic (configuratia HS, XT sau LP)

Modul de proiectare a oscilatorului microcontrolerului PIC16F84A impune

folosirea unui cristal conectat in paralel. Conectarea in serie a cristalului

poate duce la iesirea din parametrii tehnici dati de specificatiile de catalog.

Im modurile XT, LP sau HS dispozitivul poate avea o sursa de clock extern

conectat la pinul OSC1/CLKIN (Fig. 6-3).

Fig. 6-3 : Intrarea de clock externa

Tabelul 6-1 : Selectia

condensatorilor pentru rezonatorii ceramici

Tabelul 6-2 : Selectia condensatorilor pentru rezonatorii cu cristal

Pentru aplicatii nepretentioase la obtinerea

unei referinte de timp, optiunea RC ofera o alternativa mai ieftina. Frecventa

oscilatorului RC depinde de tensiunea sursei de alimentare de valoarea

rezistorului (Rext), valoarea condensatorului (Cext) si de temperatura de

lucru. In plus fata de acestea frecventa oscilatorului se va schimba de la o

valoare la alta datorita variatiilor normale a unor parametri de proces. Mai

mult, diferenta dintre valorile reale a condensatorilor afecteaza frecventa de

oscilatie, in special pentru valori mici ale Cext. Utilizatorul trebuie sa tina

seama de variatiile datorate tolerantelor componentelor R si C externe. In

figura 6-4 este prezentat modul de conectare a componentelor R/C externe pentru

PIC16F84A.

Fig. 6-4 : Modul de lucru cu oscilator RC

Microcontrolerul PIC16F84A poate avea mai multe tipuri de Reset:

In figura 6-5 este prezentata schema bloc simplificata a circuitului de reset integrat in chip-ul microcontrolerului. Calea de reset /MCLR are un filtru de zgomot pentru a filtre impulsurile mici. Specificatiile electrice precizeaza latimea necesara a impulsului pentru pinul /MCLR.

Unii registri nu sunt afectati de nici una din conditiile de reset; starea lor este necunoscuta la un POR reset si neschimbata in cazul celorlator tipuri de reset. Maoritatea celorlaltor registri sunt resetati la o stare de reset la POR, /MCLR sau WDT reset din timpul functionarii normale si la /MCLR in timpul functionarii in modul SLEEP. Ei nu sunt afectati de catre WDT reset in timpul functionarii in modul SLEEP, deoarece acest reset este vazut ca o reluare a modului de functionare normal.

In Tabelul 6-3 este prezentata o descriere a conditiilor de reset pentru registrii Program Counter (PC) si STATUS. Tabelul 6-4 furnizeaza o descriere completa a starilor reset pentru toti registrii. Bitii /TO si /PD sunt setati sau stersi diferit in situatii de reset diferite (Sectiunea 6.7). Acesti biti sunt folositi la determinarea naturii reset-ului prin software.

Fig.

6-5 : Diagrama bloc simplificata a circuitului de reset inclus in chip-ul

PIC16F84A

Tabelul 6-3 : Conditiile de reset pentru registrii PC si STATUS

Tabelul 6-4 : Conditiile de reset pentru toti registrii

Un impuls Power-on reset este generat in chip cind este detectat frontul crescator al semnalului VDD (in domeniul 1.2V-1.7V). Pentru a beneficia de avantajele POR leaga pinul /MCLR direct (sau printr-un rezistor) la VDD. Astfel vor fi eliminate componentele RC externe necesare in general la crearea Power-on Reset. Pentru o functionare normala este necesara realizarea unui timp minim de crestere pentru VDD. Vezi specificatiile electrice pentru detalii.

Cind dispozitivul incepe o functionare normala (iese dintr-o conditie de reset), parametrii de operare a dispozitivului (tensiune, frecventa, temperatura, ) trebuie indepliniti pentru a se asigura operatia. Daca aceste conditii nu sunt realizate dispozitivul ar putea fi tinut in reset pina cind conditiile de operare sunt indeplinite. Pentru informatii suplimentare vezi Nota de aplicatie AN607, 'Power-up Trrouble Shooting'. Circuitul POR nu produce reset intern cind tensiunea VDD scade.

Power-up Timer (PWRT) furnizeaza o pauza (TPWRT) de exact 72 ms fata de POR (Fig. 6-7, Fig. 6-8, Fig. 6-9 si Fig. 6-10). Power-up Timer opereaza cu un oscilator RC intern. Circuitul este tinut in reset atit timp cit PWRT este activ. Intirzierea datorata PWRT permite tensiunii VDD sa creasca la un nivel acceptabil (posibilele exceptii sunt prezentate in Fig. 6-10).

Bitul de configurare /PWRTE poate activa/dezactiva PWRT. Vezi Fig. 6-1 pentru operatiile bitului /PWRTE la fiecare dispozitiv particular. Timpul de intirziere TPWRT va varia de la circuit la circuit datorita VDD, temperaturii si variatiilor de proces. Vezi parametrii DC pentru datalii.

Oscillator Start-up Timer (OST) furnizeaza o intirziere de 1024 de cicli oscilator (de la intrarea OSC1) dupa sfirsitul intirzierii furnizate de PWRT (Fig. 6-7, Fig. 6-8, Fig. 6-9 si Fig. 6-10). Acesta ne asigura ca oscilatorul cu cristal sau rezonatorul au pornit si s-au stabilizat.

Pauza OST (TOST) este invocata numai pentru modurile XT, LP si HS si numai la Power-on Reset sau activarea din modul de lucru SLEEP. Cind VDD creste foarte incet este posibil ca pauzele TPWRT si TOST sa expire inainte ca VDD sa atinga valoarea sa finala. In acest caz (Fig. 6-10) este necesar un circuit extern care sa realizeze 'Power-on Reset' (Fig. 6-6).

Fig.

6-6 : Circuit extern pentru realizearea 'Power-on Reset'

Fig.

6-7 : Secventa de pauza la alimentare (/MCLR neconectat la VDD) cazul 1

Fig. 6-8 : Secventa de pauza la alimentare (/MCLR neconectat la VDD) cazul 2

Fig. 6-9 : Secventa de pauza la alimentare (/MCLR conectat la VDD) timp de

crestere rapid pentru VDD

Fig. 6-10 : Secventa de pauza la alimentare (/MCLR conectat la VDD) timp de

crestere lent pentru VDD

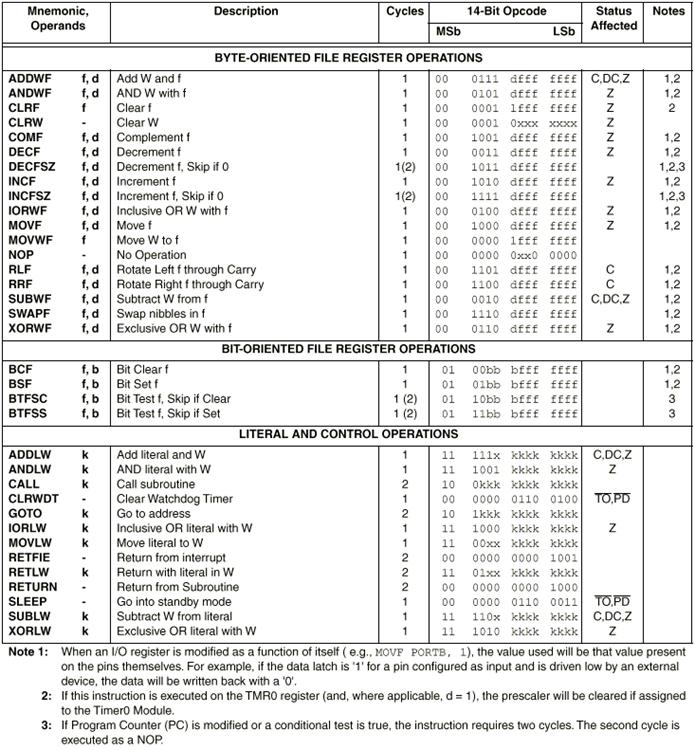

Fiecare instructiune al PIC16CXXX este un cuvint pe 16 biti impartit intr-un OPCODE care precizeaza tipul instructiunii si unul sau mai multi operanzi care in continuare precizeaza operatia instructiunii. Sumarul setului de instructiuni din tabelul 7-2 contine operatii orientate pe bit sau octet, operatii literale si de control. In tabelul 7-1 sunt aratate descrierile cimpurilor OPCODE.

Pentru instructiunile orientate pe octet, 'f' reprezinta 'file register' desemnat si 'd' reprezinta destinatia. Registrul 'f' specifica registrul ce va fi folosit de instructiune. Destinatia reprezinta locul unde va fi plasat rezultatul operatiei. Daca 'd' este zero rezultatul va fi plasat in registrul de lucru W. Daca 'd' este unu rezultatul va fi plasat in registrul specificat in instructiune.

Pentru instructiunile orientate pe bit, 'b' reprezinta cimpul bit destinatie care selecteaza numarul bitului afectat de operatie, in timp ce 'f' reprezinta numarul 'file' (registru) in care se gaseste bitul.

Pentru operatii literale si de control, 'k' reprezinta o

Tabelul 7-1 :

Descrierile cimpurilor OPCODE

Setul de instructiuni este grupat in trei categorii de baza:

Toate instructiunile sunt executate in cadrul unui singur

ciclu instructiune, in afara de cazul cind un test de conditie este adevarat

sau PC-ul este schimbat ca rezultat a unei instructiuni. Ina acest caz executia

ia doi cicli instructiune cu al doilea ciclu executat ca un NOP. Un ciclu

instructiune este este format din patru perioade de oscilator. Deci pentru o

frecventa a oscilatorului de 4 MHz, timpul de executie a unei instructiuni

normale este 1 us. Daca un test de conditie este adevarat sau daca PC-ul este

modificat ca rezultat al unei instructiuni, timpul de executie a instructiunii

va fi 2 us. In tabelul 7-2 sunt prezentate instructiunile recunoscute de catre

asamblorul MPASM. In figura 7-1 sunt aratate formatele generale pe care le pot

avea instructiunile.

Nota: Pentru a mentine compatibilitatea in sus cu viitoarele produse PIC16CXXX,

nu folositi instructiunile OPTION si TRIS.

Toate exemplele folosesc urmatorul format pentru a reprezenta un numar

hexazecimal: 0xhh , unde h reprezinta un digit hexazecimal.

Fig. 7-1 : Formatul

general al instructiunilor

Tabelul 7-2 : Setul de instructiuni al PIC16CXXX

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |