Taxonomia unitatilor de procesare a datelor

Precizand de la inceput unele elemente de terminologie, aratam ca, in acord cu multe repere de literatura consacrate, dintre care amintim [Hepa 03], [Stal 99], [Haye 98], unitatea centrala de procesare (Central Processing Unit, CPU) poate fi considerata ca avand doua componente de structura esentiale, anume asa numitele unitate de control a programului (Program Control Unit, PCU) si unitate de procesare a datelor (Data Processing Unit, DPU). Pe de o parte, PCU-ul are menirea de a capta, decodifica si interpreta acea informatie constand din instructiunile unui program, declansand secventa de semnale microoperatii a caror inlantuire sa conduca la executia fiecarei instructiuni si, implicit, a programului. Dar nu problematica specifica unui PCU este obiectivul analizelor din prezentul capitol, ci cea corespunzatoare celeilalte componente de structura constituite de DPU. Asa cum rezulta si din denumirea ei aceasta din urma unitate are menirea procesarii acelei parti a informatiei constituita din date. Cum aceastea pot fi si nenumerice, mai precizam ca ne referim la DPU-urile care prelucreaza, in principal, numere.

In esenta, un DPU contine circuistica pentru operarea aritmetica si de implementare a functiilor logice, precum si o memorie rapida si o unitate de control locala. Un prim criteriu decisiv in defalcarea DPU-urilor il constituie factorul tehnologic, in baza caruia distingem intre, pe de o parte, unitati aritmetice si logice (arithmetic - logic units, ALUs) si, pe de alta parte, procesoare aritmetice (Arithmetic Processors, APs). Primele sunt caracteristice acelei etape de dezvoltare tehnologica specifica integrarii pe scara medie catre larga, cand au fost create chip-uri incluzand in structura ALU-uri din ce in ce mai complexe, incepand cu simple sumatoare si scazatoare si mergand pana la unitati intregi care pot fi gasite in familii de circuite VLSI (Very Large Scale Integration) si ASIC (Application Specific Integrated Circuit) [Wake 00]. Pe de alta parte, categoria AP-urilor apartine erei tehnologice a integrarii pe scara larga si foarte larga incluzand in chip-uri, mai intai independente, scheme ale unor intregi procesoare dedicate evaluarii functiilor aritmetice si logice, disponibile, mai intai, in forma miniaturala a unor scheme logice secventiale, dar primind apoi tot mai multe din atributele CPU-urilor propriu-zise. Pe masura rafinarii procedeelor fotolitografice care intervin in procesul tehnologic de fabricare a circuitelor integrate si a necesitatii reducerii intarzierilor pe conductoarele de cablaj, care chiar daca erau microscopice devin "lungi", daca luam in consideratie actualele frecvente ale semnalelor, circuistica AP-urilor migreaza din chip-uri independente in interiorul celor ale procesoarelor putand fi identificate pe layout-uri ca insule in marea reprezentata de pastila de siliciu.

In ceea ce priveste ALU-urile, prin prisma aceluiasi criteriu tehnologic, acestea pot fi divizate in, actualmente, depasita clasa de circuite ALU bit slice, respectiva clasa circuitelor ALU conventionale. Intrucat, la un moment dat, densitatea de impachetare a componentelor intr-un chip era limitata la integrarea circuitelor corespunzatoare unui numar redus, spre exemplu de 4 biti, s-a apelat la strategia juxtapunerii mai multor astfel de chip-uri "felii" (slices) astfel incat cuvintele erau obtinute prin concatenarea bitilor slice-urilor [Poll 90]. Pe de alta parte, ALU-urile conventionale pot fi subimpartite in unele, mai vechi, cu registre predestinate (cum ar fi, spre exemplu, acumulatorul) si unele cu registre generale.

La randul lor, AP-urile pot fi si ele divizate in baza factorului tehnologic, dar si unul functional, in procesoare aritmetice periferice (Peripheral Arithmetic Processors, PAPs) si in coprocesoare aritmetice (Arithmetic Coprocessors, ACs). Pe de o parte, PAP-urile sunt independente de CPU-uri, comunicand cu acestea via un set de registre de comunicatie. Astfel CPU-ul executa instructii de transfer de date trimitand in registrele PAP-ului setul de operanzi, dar si informatia de comanda, aceasta din urma fiind tratata, si ea, ca o data. PAP-ul decodifica informatia de comanda, executa operatia, plasand, in final, rezultatul tot intr-unul dintre registrele de comunicatie, accesibile de CPU. Fie la initiativa PAP-ului prin intermediul unui semnal de intrerupere, fie la initiativa CPU-ului, prin consultarea unui registru de stare, CPU-ul afla ca PAP-ul a terminat executia operatiei si preia, prin acelasi tip de instructii de transfer de date, rezultatul operatiei aritmetice de la PAP. Pe de alta parte, AC-urile nu sunt indepedente, ele sunt "croite" pentru o anumita familie de CPU-uri. Astfel, fiecare CPU este prevazut atat cu circuite de interfatare cu AC-ul, asigurand controlul comunicatiei dintre cele doua, cat si cu instructii speciale menite a fi executate de AC. Se spune ca, uzual, CPU-ul si AC-ul sunt strans cuplate (tightly coupled) in sensul ca tre cele doup exista linii de comunicatie directe care au rolul de a permite intrarea lor rapida in sincronism, intrucat AC-ul este, in deobste, intr-o stare latenta, de asteptare, el trebuind "trezit" atunci cand trebuie executata o instructie de coprocesor [Haye 98]. Tehnologic, CPU-ul si AC-ul erau constituite din doua chip-uri distincte, interconectate printr-un soclu special, dar actualmente intreaga circuistica de operare aritmetica si logica este integrata in aceasi pastila de siliciu corespunzatoare intregului procesor.

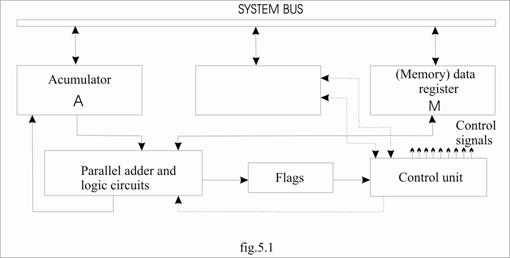

Dar, indiferent ca avem de-a face cu ALU-uri sau AP-uri, ambele pot fi impartite prin prisma domeniului valoric al numerelor pe care le opereaza, in doua parti, una de virgula fixa, cu domeniu mai restrans, dar si cu circuistica mai simpla, si una din virgula mobila, cu domeniu mai extins dar si cu circuistica mai complexa. Pentru a pune in relief elementele distinctive ale celor doua parti, sa ne referim la cazul mai simplu al unui ALU pentru care dam schema sintetica din fig 5.1, acoperitoare pentru operatiile aritmetice abordate in precedentele capitole.

Se recunosc cele trei

registre pentru care am pastrat nume predestinate, dar care pot

fi considerate ca apartinand pilei din registre generale. Toate trei sunt

comutate bidirectional la magistrala de sistem (system bis), iar registrul

M, care gazduieste unul dintre operanzi indiferent de operatie,

este un registru cu date considerat al memoriei. Pe langa sumatorul paralel

cu circuitele logice aferente, schema mai contine un bloc al fanioanelor

(flags), reprezentand bistabile setate pe 1 la indeplinirea anumitor

conditii cum ar fi overflow, carry din msb, rezultat zero sau negativ,

s.a. Unitatea de control genereaza semnalele de control (marcate punctat)

a caror inlatuire asigura implementarea algoritmilor, pe

care, pentru concretete si fara a pierde din generalitate,

ii consideram secventiali. Modalitatea tipica de utilizare a

registrelor consta in ![]() pentru adunare,

pentru adunare, ![]() pentru scadere,

pentru scadere, ![]() pentru impartire, respectiv

pentru impartire, respectiv ![]() pentru inmultire. Aceste operatii se

efectueaza asupra unor operanzi numerici, dar gama operatiilor poate

fi extinsa si asupra unor functii logice, care pot fi realizate

si asupra unor operanzi nenumerici. Caracteristic acestora este operarea

pe perechi de biti, implicand urmatoarea utilizare tipica a

registrelor: A: = A and M

pentru functia logica AND, A: =

A or B pentru functia logica OR, A: = A ex-or M pentru functia logica EXCLUSIVE-OR,

respectiv A: = not A pentru

functia logica de complementare. Implementarea acestor operatii

este simpla implicand porti pe toata lungimea cuvintelor (wordgates)

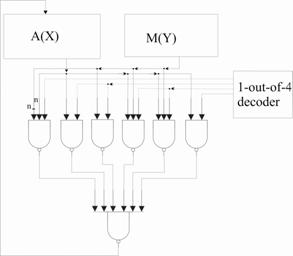

care contribuie la realizarea unei anumite functii. Astfel in fig. 5.2 se

prezinta o posibilitate de realizare a partii care vizeaza

operatiile logice ale unui ALU, cum este, spre exemplu, cel din fig. 5.1.

pentru inmultire. Aceste operatii se

efectueaza asupra unor operanzi numerici, dar gama operatiilor poate

fi extinsa si asupra unor functii logice, care pot fi realizate

si asupra unor operanzi nenumerici. Caracteristic acestora este operarea

pe perechi de biti, implicand urmatoarea utilizare tipica a

registrelor: A: = A and M

pentru functia logica AND, A: =

A or B pentru functia logica OR, A: = A ex-or M pentru functia logica EXCLUSIVE-OR,

respectiv A: = not A pentru

functia logica de complementare. Implementarea acestor operatii

este simpla implicand porti pe toata lungimea cuvintelor (wordgates)

care contribuie la realizarea unei anumite functii. Astfel in fig. 5.2 se

prezinta o posibilitate de realizare a partii care vizeaza

operatiile logice ale unui ALU, cum este, spre exemplu, cel din fig. 5.1.

In cele doua registre, A si M, sunt stocati operanzii X, respectiv Y, care sunt aplicati, dependent de functia logica, la nivelul celor sase wordgate-uri. La iesirile acestora se obtin subfunctii care, negate de wordgate-ul din al doilea nivel logic, sa duca la functiile dorite. Cele patru functii logice sunt comandate prin combinatia de valori a doua semnale de control (co, c1) provenite de la CPU si care sunt decodificate prin 1-out-of-4 decoder. Fiecare iesire a decodificatorului este condusa la wordgate-urile corespunzatoare unei anumite functii logice (cate un singur wordgate pentru functiile and si not si cate doua pentru functiile or si ex-or) si prin valoarea 1 (in timp ce celelalte trei sunt pe 0) determina realizarea respectivei functii. La iesirile wordgate-urilor din primul nivel au fost marcate subfunctiile in termeni de X si de Y ignorand conditionarile prin iesirile decodificatoarelor (se remarca obtinerea functiilor or si ex-or prin aplicarea legilor De Morgan).

Fig. 5.2

Cu precizarile aduse relative la subunitatea de logica a ALU care, coroborate cu cele expuse in capitolele anterioare relative la subunitatea de aritmetica, permit conturarea anvergurii circuisticii unui ALU cu operare in virgula fixa, sa incercam sa punctam diferentele dintre o astfel de unitate si una cu operare in virgula flotanta. Aceasta vizeaza doar o parte aritmetica, dar, pentru a le scoate in evidenta, sa analizam in amanunt executia operatiilor fundamentale in virgula flotanta.

|

Politica de confidentialitate |

| Copyright ©

2026 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |