Circuite de memorie

Un circuit de memorare este un circuit electronic care permite stocarea si regasirea unor informatii reprezentate sub forma binara care au fost anterior stocate. Aceasta implementare se poate realiza in mai multe moduri, in functie de suportul fizic utilizat ca de exemplu: memorii magnetice, memorii optice, memorii semiconductoare. In continuare ne vom referi numai la memoriile realizate cu dispozitive semiconductoare.

Exista doua categorii majore de memorii semiconductoare:

- memorii cu citire si scriere de date, in aceasta categorie intra asa numitele memorii cu acces aleator RAM (Random Access Memory) care permit citirea si inscrierea unor noi date de catre sistemul care le utilizeaza. Pentru acest tip de memorie timpul de acces este egal pentru orice adresa si ele pot fi selectate in orice ordine. Deoarece memoriile RAM isi pierd continutul in lipsa alimentarii ele sunt memorii volatile.

- memorii numai cu citire de date, in aceasta categorie intra memoriile ROM (Read Only Memory), PROM (Programmable Read Only Memory), EPROM (Eraseable Programmable Read Only Memory) care pot fi numai citite de catre sistemul care le utilizeaza, stergerea fiind posibila numai in cazul memoriilor de tip EPROM, dar nu este efectuata de catre sistemul utilizator si nu este selectiva in raport cu informatia inscrisa. De asemenea tot in aceasta categorie intra si memoriile EEPROM (Electricaly Eraseable Programmable Read Only Memory) care pot fi atat citite cat si sterse in mod selectiv si reprogramate de catre sistemul care le utilizeaza. Deoarece memoriile ROM nu isi pierd continutul in lipsa alimentarii ele se numesc nevolatile.

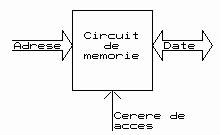

Citirea informatiei stocate necesita furnizarea unor semnale privind locul unde se gaseste aceasta informatie. Aceste semnale constituie intrari pentru circuitul de memorie si se numesc adrese. Cuvintele binare memorate constituie date pentru acest circuit si ele sunt semnale de intrare atunci cand se inscrie in memorie si semnale de iesire atunci cand se citeste din memorie. Accesul la memorie se face la un moment de timp bine determinat, care se comunica circuitului de memorie printr-un semnal. Astfel circuitul de memorie impreuna cu conexiunile sale informationale are structura din figura 7.1.

Figura 7. . Conexiunile memoriei.

Transferul de date este bidirectional in cazul memoriilor RAM si EEPROM si unidirectional in cazul memoriilor ROM, PROM si EPROM.

Fiecare element de stocare din memorie se numeste celula si poate lua valoarea 0 logic sau 1 logic. Memoria este compusa din arii de celule.

Putem definii:

- Geometria sau modul de organizare a memoriei reprezentata de lungimea unui cuvant si numarul de cuvinte memorate;

- Capacitatea memoriei reprezentand numarul total de biti ce pot fi memorati, se exprima in general in multipli de 1 k=1024 biti. Acest numar reprezinta produsul dintre numarul cuvintelor memorate si lungimea cuvantului. De exemplu o memorie de 16k octeti reprezinta o memorie de 16.384 cuvinte de 8 biti.

In figura 7.2 se prezinta diferite moduri de organizare a memoriei folosind ca exemplu o arie de 64 de celule. In figura 7.2.a se prezinta o memorie cu capacitatea de 64 biti organizata ca o memorie de 8 cuvinte de 8 biti adica o memorie de 8 octeti. In figura 7.2.b se prezinta o memorie de aceeasi capacitate dar organizata ca o memorie de 16 cuvinte de 4 biti adica 16 nible. In cele din urma figura 7.2.c reprezinta o memorie de 64 cuvinte de 1 bit.

|

a) arie de 8x8 |

b) arie de 16x4 |

c) arie de 64x1 |

|||||||||||||||||||||

Figura 7. . Arie de memorie de 64 celule organizata in trei moduri diferite

Alte proprietati ale memoriilor sunt:

- Timpul de acces la memorie reprezinta timpul necesar pentru citirea sau scrierea unor informatii in memorie, se exprima in ms sau ns.

- Puterea consumata raportata la un bit de informatie, exprima puterea totala consumata de circuit raportata la capacitatea memoriei adica mW/bit;

- Volatilitatea. O memorie este volatila daca informatia inscrisa se pierde in timp, pierderea informatiei se poate datora fie modului de stocare a acesteia in cazul memoriilor dinamice, fie datorita disparitiei tensiunilor de alimentare ale circuitului.

Modul de adresare depinde de organizarea memoriei. Adresa unui bit este data prin linie si coloana in timp ce adresa unui octet se specifica doar prin linie, ca si in figura 7.3.

|

| |||||||||||||||||||||

|

a) adresa bitului este lina 5 coloana 4 |

b) adresa octetului este linia 4 | ||||||||||||||||||||

Figura 7. . Exemple de adresare a memoriilor.

Avand in vedere ca memoriile stocheaza date binare, acestea trebuiesc puse in memorie si datele de care avem nevoie trebuiesc citite din memorie. Operatia de punere a datelor la o anumita adresa in memorie se numeste scriere iar operatia de scoatere a datelor de la o anumita adresa din memorie se numeste citire din memorie. Operatia de adresare este parte componenta a ambelor operatii si permite selectarea adresei de memorie specificata. Datele se scriu si se citesc prin intermediul magistralei de date care este bidirectionala, adica datele pot circula spre sau dinspre memorie, asa cum se poate vedea si in figura 7.1. Adresa este specificata printr-un cod plasat pe magistrala de adrese. Codul de adresa este decodificat in interiorul memoriei, si se selecteaza adresa dorita. Numarul de linii din magistrala de adrese depinde de capacitatea memoriei. De exemplu un cod de adresa de 12 biti poate selecta 4096 (212) locatii de memorie, un cod de 16 biti poate selecta 655363 (216) locatii, iar un cod de 32 biti cum se intalneste in calculatoarele personale poate selecta 4.294.967.296 (232) locatii, exprimat ca 4G locatii.

Operatia de scriere. O operatie simpla de scriere este reprezentata in figura 7.4. Pentru a stoca un octet de date in memorie, un cod pastrat intr-un registru de adresa este pus pe magistrala de adresa. Decodificatorul de adresa decodifica aceasta adresa si selecteaza locatia de memorie specificata. Dupa aceasta memoria primeste o comanda de scriere si datele pastrate intr-un registru de date sunt plasate pe magistrala de date si stocate la adresa indicata din memorie. Daca se da o comanda de scriere la o adresa la care au mai fost inscrise date, acestea se suprascriu, deci se pierd.

Operatia de scriere se face in felul urmator:

Codul adresei este plasat pe magistrala de adrese si adresa 5 este selectata

Octetul de date se plaseaza pe magistrala de date

Comanda de scriere cauzeaza inscrierea datei la adresa 5, datele precedente sunt inlocuite.

|

Registru de |

Registru de |

||||||||||||||||||||||

|

adresa |

date |

||||||||||||||||||||||

|

|

|||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

Decodificator de adresa | |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

Scriere | |||||||||||||||||||||||

Figura 7. . Operatiei de scriere in memorie.

Operatia de citire. Pentru a citi un octet de date din memorie un cod pastrat intr-un registru de adresa este pus pe magistrala de adresa. Decodificatorul de adresa decodifica aceasta adresa si selecteaza locatia de memorie specificata. Dupa aceasta memorie primeste o comanda de citire si o copie a octetului de date stocat la adresa specificata este plasat pe magistrala de date si incarcat intr-un registru de date. La citirea datelor de la o adresa, acestea raman in continuare in memorie deci nu se pierd. Aceasta se numeste citire nedistructiva. Operatia de citire este prezentata in figura 7.5.

|

Registru de |

Registru de |

||||||||||||||||||||||

|

adresa |

date |

||||||||||||||||||||||

|

|

| ||||||||||||||||||||||

|

Decodificator de adresa | |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

| |||||||||||||||||||||||

|

Citire | |||||||||||||||||||||||

Figura 7. . Operatia de citire a memoriei.

Operatia de citire se face in felul urmator:

Codul adresei este plasat pe magistrala de adrese si adresa 4 este selectata.

Se aplica comanda de citire.

Continutul memoriei de la adresa 4 este plasat pe magistrala de date si se inscrie in registrul de date. Continutul locatiei 4 ramane neschimbat.

Pentru memorarea unui cuvant circuitul registru poate fi un suport flexibil si de mare viteza. La un volum mai mare de cuvinte solutia este o colectie de registre, dar pentru un volum mai mare de ordinul sutelor de cuvinte are urmatoarele dezavantaje: cost ridicat, acces doar pe cuvant si decodificator complex. Pentru un volum mare de informatie solutia eficienta este o memorie realizata ca o colectie de celule de memorare, fiecare celula avand posibilitatea de selectare pentru stergere si inscriere a unui bit.

In cadrul familiei de memorii RAM se disting doua subfamilii si anume memoriile RAM statice - SRAM (Static RAM) si memoriile RAM dinamice - DRAM (Dynamic RAM). Memoriile RAM statice folosesc ca element de memorare circuite basculante bistabile si prin urmare pot memora informatia un timp nedefinit, atat timp cat se pastreaza alimentarea circuitului. Memoriile RAM dinamice folosesc condensatoare ca elemente de stocare si prin urmare ele nu pot memora informatia un timp foarte mare fara ca acestea sa fie reincarcate in cadrul unui proces numit reimprospatare. Ambele tipuri pierd informatia memorata la decuplarea alimentarii si in consecinta fac parte din clasa memoriilor volatile.

Datele pot fi citite mai rapid din memoriile SRAM decat din memoriile DRAM, dar acestea din urma pot stoca mult mai multe date pentru o dimensiune fizica data si la un pret mai mic datorita faptului ca ele sunt mai simple si se pot integra mai multe celule de memorare DRAM pe unitatea de suprafata decat celule SRAM.

Tipurile de baza de memorii SRAM sunt memoria SRAM asincrona si memoria SRAM in rafale (sau cu lucru in avalansa). Tipurile de baza de memorii DRAM sunt memoria FPM DRAM (Fast Page Mode DRAM), EDO DRAM (Extended Data Out DRAM), BEDO DRAM (Burst EDO DRAM) si memoria DRAM sincrona (SDRAM), si mai nou DDRAM (Double Data Rate SDRAM).

|

Memoria cu acces aleator (RAM) | ||||||||||||||||||||||

|

Memoria RAM statica (SRAM) |

Memoria RAM dinamica (DRAM) | |||||||||||||||||||||

|

||||||||||||||||||||||

|

Memoria SRAM asincrona (ASRAM) |

SRAM cu lucru in avalansa (SBRAM) |

DRAM cu acces rapid pe pagina (FPM DRAM) |

DRAM cu iesire extinsa de date (EDO DRAM) |

EDO DRAM cu lucru in avalansa (BEDO DRAM) |

Memorie DRAM sincrona (SDRAM) |

|||||||||||||||||

Figura 7. . Familia de memorii RAM.

Consideram ca fiind o celula de memorie, circuitul elementar care realizeaza memorarea unui bit. Aceasta se poate realiza fie cu tranzistoare bipolare fie cu tranzistoare MOS.

Toate memoriile RAM statice sunt alcatuite din bistabili care de obicei sunt implementati cu tranzistoare MOS. Exista unele memorii de capacitate mica realizate cu tranzistoare bipolare.

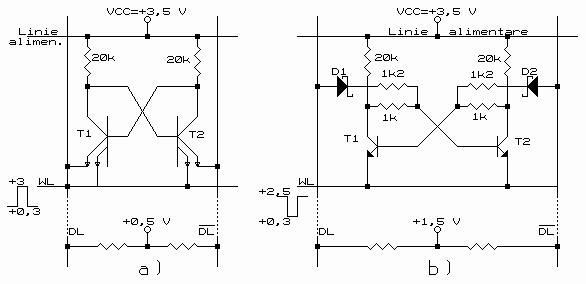

In cazul utilizarii tranzistoarelor bipolare circuitul elementar de memorie il constituie circuitul basculant bistabil (CBB). In figura 7.7 sunt prezentate structuri de bistabile folosite in memoriile RAM avand capacitatea de pana la 1 kbit.

Dupa cum se vede, schemele au la baza un CBB realizat cu tranzistoarele T1 si T2. Liniile de conexiune in afara celulei sunt:

-

2 linii de bit (DL si ![]() ) care folosesc la scrierea si citirea informatiei

in celula, aceste linii sunt comune tuturor celulelor de pe aceiasi

coloana dintr-o matrice de memorie;

) care folosesc la scrierea si citirea informatiei

in celula, aceste linii sunt comune tuturor celulelor de pe aceiasi

coloana dintr-o matrice de memorie;

- o linie de selectie cuvant (WL), reprezentand selectia pe linii in matricea de memorie, actionarea unei selectii cuvant face posibila citirea sau scrierea informatiei in oricare din celulele de memorie situate pe aceeasi linie in matrice;

- o linie de alimentare (sursa de tensiune VCC), aceasta conexiune este comuna tuturor celulelor din matricea de memorie.

Figura 7. . Celula de memorare SRAM cu tranzistoare bipolare.

Celula

de memorie din figura 7.7.a foloseste tranzistoare multiemitor. In starea

neselectata conexiunea selectie cuvant (WL) este mentinuta

la un potential coborat (+0,3 V). Liniile de bit (DL, ![]() ) sunt conexiuni pentru sesizarea starii bistabilului

si in mod normal sunt conectate la capatul coloanei la o tensiune de

0,5 V prin intermediul unor rezistente care sa sesizeze aparitia

inchiderii unui curent. Pentru citire,

selectia cuvant este pusa la un potential mai ridicat (+3 V) apropiat

de VCC. In felul acesta emitoarele conectate la liniile de bit sunt

polarizate la o tensiune mai coborata (+0,5 V) si conductia este

preluata de acestea. Curentul de emitor se va inchide pe rezistentele

senzor conectate la liniile de bit si in functie de semnul tensiunii

obtinute la bornele celor doua linii de bit se poate spune care este

starea bistabilelor. Daca spre exemplu T1 conduce si T2

este blocat, atunci la aplicarea comenzii citire pe selectia cuvant se va

obtine la iesire o tensiune diferentiala cu plusul pe DL

si minusul pe

) sunt conexiuni pentru sesizarea starii bistabilului

si in mod normal sunt conectate la capatul coloanei la o tensiune de

0,5 V prin intermediul unor rezistente care sa sesizeze aparitia

inchiderii unui curent. Pentru citire,

selectia cuvant este pusa la un potential mai ridicat (+3 V) apropiat

de VCC. In felul acesta emitoarele conectate la liniile de bit sunt

polarizate la o tensiune mai coborata (+0,5 V) si conductia este

preluata de acestea. Curentul de emitor se va inchide pe rezistentele

senzor conectate la liniile de bit si in functie de semnul tensiunii

obtinute la bornele celor doua linii de bit se poate spune care este

starea bistabilelor. Daca spre exemplu T1 conduce si T2

este blocat, atunci la aplicarea comenzii citire pe selectia cuvant se va

obtine la iesire o tensiune diferentiala cu plusul pe DL

si minusul pe ![]() . In cazul T1 blocat si T2 conduce

sensul tensiunii se schimba.

. In cazul T1 blocat si T2 conduce

sensul tensiunii se schimba.

Pentru

inscrierea informatiei in

celula se ridica potentialul selectiei cuvant (WL) si

simultan se forteaza cu circuite adecvate pe liniile de bit o diferenta de potential corespunzatoare starii

in care dorim sa se afle bistabilul. De exemplu, pentru a obtine T1

in conductie si T2 blocat se forteaza linia de

bit stanga (DL) la zero iar linia de bit

dreapta (![]() ) la o tensiune de circa +0,5 V. Acest circuit are un consum

de putere in stare neselectata de circa 800 mV si o viteza de

comutatie de 20 ns.

) la o tensiune de circa +0,5 V. Acest circuit are un consum

de putere in stare neselectata de circa 800 mV si o viteza de

comutatie de 20 ns.

Celula din figura 7.7.b foloseste diode Schottky avand un consum de putere in stare neselectata de 60 mV si o viteza de comutatie de 5 ns.

Celula de memorie statica realizata cu tranzistoare NMOS este reprezentata in figura 7.8. Celula foloseste sase tranzistoare NMOS. Tranzistoarele T1 si T2 reprezinta sarcini active, iar T3 si T4 constituie un bistabil. Tranzistoarele T5 si T6 permit conectarea iesirilor bistabilului la liniile de bit pentru citirea sau inscrierea informatiei. In starea neselectata linia WL se afla conectata la potential zero si tranzistoarele T5 si T6 sunt blocate. Liniile de bit sunt conectate prin rezistente la +VDD.

|

|

|

Figura 7. . Celula de memorare SRAM cu tranzistoare NMOS |

Pentru citire se aplica tensiune

ridicata pe linia de selectie cuvant WL. Tranzistoarele T5

si T6 se deschid si permit determinarea starii

bistabilului. De exemplu, cand bistabilul este in starea T3 blocat

si T4 conductie, la comanda de citire linia de bit ![]() va avea un

potential apropiat de zero prin tranzistorul T4.

va avea un

potential apropiat de zero prin tranzistorul T4.

![]() Pentru inscrierea informatiei se ridica potentialul liniei

WL si apoi se forteaza cu circuite adecvate tensiune zero pe

linia de bit in care dorim sa obtinem zero la citire. De exemplu

daca se aplica zero pe linia DL bistabilul va trece in starea T3

conductie si T4 blocat.

Pentru inscrierea informatiei se ridica potentialul liniei

WL si apoi se forteaza cu circuite adecvate tensiune zero pe

linia de bit in care dorim sa obtinem zero la citire. De exemplu

daca se aplica zero pe linia DL bistabilul va trece in starea T3

conductie si T4 blocat.

Acest circuit folosind tranzistoare MOS cu canal n are o viteza de comutatie relativ ridicata si o putere disipata in stare neselectata mica. Ca un dezavantaj trebuie mentionat ca sunt necesare doua linii de alimentare pentru fiecare celula deoarece pentru conductia tranzistoarelor T1 si T2 de tipul MOS cu imbogatire, grilele trebuie sa fie la un potential pozitiv fata de sursele tranzistoarelor.

Se poate vedea ca daca pentru durate scurte de timp tensiunea de alimentare VDD lipseste bistabilul isi pastreaza starea datorita capacitatilor parazite grila sursa ale tranzistoarelor T3 si T4. Aceasta proprietate sugereaza posibilitatea micsorarii puterii consumate (si deci disipate) in celula prin intreruperea si cuplarea periodica a alimentarii. Se poate obtine in felul acesta o reducere a puterii consumate de pana la 1000 de ori (intr-o perioada de 2 ms se alimenteaza circuitul numai un interval de 2 ms).

Figura 7. .Celula de memorare

SRAM cu tranzistoare CMOS

Circuitul din figura 7.9 foloseste un circuit basculant bistabil realizat cu tranzistoare complementare MOS (CMOS). Ca urmare in oricare din starile stabile circuitul nu consuma energie de la sursa de alimentare. Functionarea circuitului este similara cu aceea a circuitului precedent. In stare neselectata linia WL este la un potential coborat si T5, T6 blocate.

Pentru

citire se aplica un

potential ridicat liniei WL iar pentru inscriere se forteaza suplimentar tensiune coborata

pe una din liniile de bit DL sau ![]() . Acest circuit are o singura sursa de

alimentare, deoarece foloseste tranzistoare MOS canal p si canal n.

. Acest circuit are o singura sursa de

alimentare, deoarece foloseste tranzistoare MOS canal p si canal n.

Problema esentiala in realizarea acestor circuite este obtinerea unor circuite de memorie cu o capacitate cat mai mare pe o suprafata de semiconductor cat mai mica. Aceasta se poate realiza urmarind reducerea suprafetei ocupate de o celula si a numarului de interconexiuni. Reducerea suprafetei unei celule este legata de doua aspecte:

reducerea puterii disipate in celula;

reducerea numarului de componente electronice ale unei celule si a dimensiunilor acestora.

Structura celulei de memorie poate fi simplificata in mod considerabil daca pentru stocarea informatiei se foloseste sarcina acumulata intr-un condensator. Starea 0 poate fi reprezentata printr-un condensator descarcat (tensiune zero) iar starea 1 printr-un condensator incarcat (tensiune diferita de zero).

In figura 7.10 se prezinta un astfel de circuit in care capacitatile de memorare sunt realizate cu capacitatile grila-sursa ale tranzistoarelor MOS.

Eliminarea tranzistoarelor de sarcina din bistabil este posibila, starea circuitului ramanand nemodificata datorita sarcinii acumulate in cele doua condensatoare C1 si C2.

|

|

|

Figura 7. . Celula de memorare RAM MOS dinamica |

Cele doua condensatoare nu sunt realizate separat de tranzistoarele T1 si T2 pe circuit ci sunt formate de capacitatea grila canal a tranzistoarelor T1 si T2. Daca bistabilul este in starea T1 blocat si T2 saturat, inseamna ca avem VGS1=0 si VGS2>Vprag respectiv C1 descarcat si C2 incarcat. Pentru situatia cand T3 si T4 conduc, ansamblul T1, T2 , T3, T4 formeaza un bistabil similar cu cel din figura 7.8 si circuitul isi mentine starea. Daca T3 si T4 sunt blocate sarcina acumulata in C2 se pierde lent datorita descarcarii prin jonctiunea drena substrat a tranzistorului T1. Pentru un anumit interval de timp ( 2 ms) se poate considera ca C2 ramane incarcat si informatia inscrisa (T1 blocat si T2 conductie) se pastreaza. Ca urmare circuitul poate functiona fara tranzistoarele de sarcina, folosind pentru memorare sarcina acumulata in condensatoarele C1 sau C2, cu conditia ca ceasta sa fie refacuta periodic. Refacerea ei se face pur si simplu prin deschiderea tranzistoarelor T3 si T4. Trebuie observat ca o comanda de deschidere a tranzistoarelor T3 si T4 afecteaza simultan toate celulele de pe aceeasi linie WL si deci refacerea sarcinii se face in toate celulele de pe linia selectata. Simultan cu refacerea sarcinii la fel ca la circuitele precedente se poate face si citirea starii prin masurarea curentului ce se inchide prin liniile de bit si rezistentele conectate la +VDD. Deosebim deci urmatoarele moduri de lucru:

Citire: se ridica nivelul liniei

WL si se citesc potentialele liniilor de bit DL si ![]() ;

;

Scriere: se ridica

nivelul liniei WL si se forteaza cu circuite adecvate

potentialele corespunzatoare pe liniile de bit DL si ![]() pentru o anumita

stare a bistabilului, de exemplu pentru a pune bistabilul in starea T1

blocat si T2 in conductie se aplica potential

ridicat pe linia

pentru o anumita

stare a bistabilului, de exemplu pentru a pune bistabilul in starea T1

blocat si T2 in conductie se aplica potential

ridicat pe linia ![]() si potential coborat pe linia DL.

si potential coborat pe linia DL.

Refacerea sarcinii (refresh) in condensatoare: se face simultan cu citirea sau scrierea prin comanda WL, pentru o intreaga linie, refacerea sarcinii trebuie facuta pentru toate liniile matricei de memorie in intervalul de timp corespunzator , pentru ca sarcina pierduta sa nu modifice starea bistabilului.

Aceasta structura de circuit are urmatoarele avantaje:

- se folosesc numai patru tranzistoare pe celula;

- sunt necesare numai trei linii de legatura, lipsind linia de alimentare.

Ca urmare, circuitul obtinut permite o densitate mai mare de celule de memorie si respectiv o capacitate mai mare a memoriei pe aceeasi suprafata de siliciu.

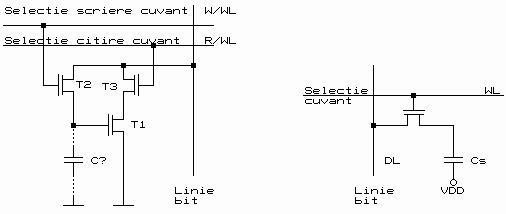

Folosind memorarea prin sarcina electrica a unui condensator, circuitul se poate simplifica in continuare, obtinandu-se o structura cu trei tranzistoare pe celula (figura 7.11).

|

Figura 7. . Celula RAM MOS dinamica cu numar redus de componente |

Figura 7. . Celula RAM MOS dinamica minimala |

Elementul de memorie il constituie condensatorul C constituit din capacitatea grila canal a lui T1. Daca C este descarcat atunci VGS1<Vprag si T1 este blocat, iar daca C este incarcat atunci T1 este in conductie.

Citirea se face prin aplicarea unui potential ridicat (VDD) pe linia R/WL. Aceasta determina intrarea in conductie a lui T3 si aparitia unui curent prin linia de bit daca T1 este in conductie. Sesizarea acestui curent permite recunoasterea starii memorate in C.

Inscrierea informatiei in circuit se face prin comanda cu impuls pozitiv a liniei W/WL, ceea ce duce la deschiderea lui T2 si fortarea liniei de bit in zero sau VDD in functie de informatia ce trebuie inscrisa. Potentialul respectiv se transmite condensatorului C descarcandu-l sau incarcandu-l.

Reimprospatarea sarcinii pe C, in cazul acestui circuit nu se mai face automat la citire, ne mai existand CBB. Ea trebuie facuta in mod explicit dupa o citire. In timpul citirii se inregistreaza informatia prezenta pe toate celulele selectate de R/WL si apoi se reinscrie printr-o comanda pe W/WL impreuna cu prezentarea acestei informatii (0 sau 1) pe liniile de bit. Aceasta duce la complicarea circuitelor anexe pe fiecare coloana.

Avantajul acestei structuri consta in principal in reducerea numarului de elemente pe celula si deci implicit in cresterea capacitatii memoriei pe unitatea de arie.

Cea mai simpla structura a unei celule de memorie care foloseste memorarea pe condensator este cea prezentata in figura 7.12.

In acest circuit capacitatea Cs este realizata independent de tranzistor, constituind o parte componenta a celulei de memorie. Selectia celulei se face prin deschiderea tranzistorului, aplicand potential pozitiv in grila sa (linia WL). Datele sunt citite sau scrise pe linia de bit DL.

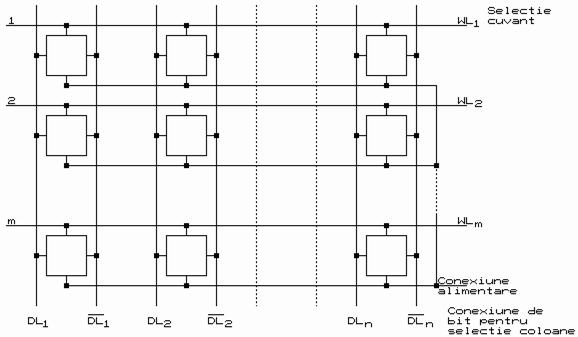

Circuitul

de memorare propriu-zis este aranjat sub forma unei matrici in ale carei

noduri se gasesc celulele de memorie. Structura circuitului de memorie

avand o matrice de m x n celule este data in figura 7.13. Pentru accesul

la celula de memorie (i, j) se face selectia liniei actionand WLi

si selectia coloanei prin perechea DLj![]() . Capacitatea memoriei este data de produsul m x n

si se masoara in biti.

. Capacitatea memoriei este data de produsul m x n

si se masoara in biti.

Celula de memorare

![]()

Figura 7. . Structura unei matrici de memorie.

Celula de memorare dintr-o matrice poate fi cu functionare statica sau dinamica de unde si denumirile corespunzatoare structurii respective de memorie SRAM, pentru memoria cu celule statice si DRAM pentru memoria cu celule dinamice. O celula statica pastreaza un timp nedefinit informatia inscrisa, in schimb la o celula dinamica proprietatea de memorare a informatiei depinde de timp in sensul ca memorarea are loc un timp definit.

Circuitele anexa care asigura functionarea unei celule de memorie sunt:

- circuitele de selectie - decodificatoare de linii si coloane care permit selectarea prin linia WLi si coloana DLj a celulei dorite;

-

circuitele de citire a informatiei din celula, conectate pe liniile

de bit DLj si ![]() j, aceste circuite sunt comune unei intregi

coloane din matricea de memorie, ele sunt activate de decodificatorul de

coloana;

j, aceste circuite sunt comune unei intregi

coloane din matricea de memorie, ele sunt activate de decodificatorul de

coloana;

-

circuite de inscriere a informatiei in celula, conectate de asemenea

pe liniile de bit DLj si ![]() j, acestea asigura fortarea

potentialelor liniilor de bit astfel incat sa se inscrie

informatia corespunzatoare in celula, si aceste circuite

sunt activate de decodificatorul de adresa.

j, acestea asigura fortarea

potentialelor liniilor de bit astfel incat sa se inscrie

informatia corespunzatoare in celula, si aceste circuite

sunt activate de decodificatorul de adresa.

Cand numarul de celule de memorare este mare (>103) complexitatea circuitului de inscriere, citire si in special a celui de selectare pentru aceste doua operatii intrece pe cea a celulelor care de fapt constituie suportul de memorare. Complexitatea circuitului de selectare se poate reduce printr-o structurare a celulelor intr-o retea matriciala cu o selectare bidimensionala, pe linii si coloane. De aceea adresa de n biti este divizata in doua grupe de biti, una se aplica decodificatorului liniilor matricei iar cealalta grupa multiplexoarelor pentru coloane. Din punct de vedere tehnologic este recomandat ca matricea de celule sa fie patrata. O matrice patrata necesita ca n/2 biti de adresa sa fie aplicati la DCD n/2:2n/2 pentru activarea uneia din cele 2n/2 linii iar ceilalti n/2 biti sa fie aplicati circuitului MUX 2n/2:1 pentru selectarea uneia din cele 2n/2 coloane. La intersectia liniei activate cu coloana selectata se afla celula asupra careia se poate realiza o operatie de scriere sau citire (figura 7.14).

Aceasta structurare, realizata doar cu un circuit multiplexor pentru selectarea pe dimensiunea orizontala trebuie completata. Deoarece o celula poate primi date, prin inscriere, si poate genera date, prin citire, circuitul de selectare pe orizontala trebuie sa permita transferul bidirectional al datelor. O astfel de structura, ce poate atat sa distribuie date (DMUX) cat si sa selecteze date (MUX) este referita ca un circuit multiplexor-demultiplexor.

Pentru a prezenta structura circuitelor de memorie de tip SRAM luam ca exemplu memoria uPD43256B care este o memorie SRAM de 32K x8 biti. Simbolul logic este prezentat in figura 7.15.a.

|

|

128 coloane linii |

|

a) Simbolul logic

b) Configuratia ariei de memorie

Figura 7. . Memoria uPD43256B, SRAM de 32K x8 biti

Matricea de memorie contine la intersectia unei linii cu o coloana o celula de memorie de 1 bit. Liniile de intrare si iesire de date I/O1 pana la I/O8 sunt comune. Pentru a putea folosii linii comune pentru intrare si iesire se folosesc circuite tampon cu trei stari (buffere tristate). Figura 7.15.b prezinta organizarea ariei de memorie.

Figura 7. . Schema bloc a memoriei mPD43256B.

Functionarea

memoriei este urmatoarea. Pentru ca memoria sa poata

functiona ea trebuie sa primeasca un semnal ![]() de valoare zero logic.

Liniile de adresa sunt impartite in doua grupe. Opt din

cele 15 linii de dresa sunt decodificate de decodificatorul de linii

pentru a selecta o linie din cele 256 iar restul de sapte de

decodificatorul de coloane care selecteaza o coloana din 128. La

intersectia dintre linia si coloana selectata se

gaseste cuvantul de 8 biti care trebuie citit sau scris.

de valoare zero logic.

Liniile de adresa sunt impartite in doua grupe. Opt din

cele 15 linii de dresa sunt decodificate de decodificatorul de linii

pentru a selecta o linie din cele 256 iar restul de sapte de

decodificatorul de coloane care selecteaza o coloana din 128. La

intersectia dintre linia si coloana selectata se

gaseste cuvantul de 8 biti care trebuie citit sau scris.

Semnalele

sunt transmise in exterior prin intermediul unor circuite de intrare si

iesire. Circuitul de control comanda circuitele care participa

la realizarea functiei de citire sau scriere. De exemplu pentru citire

semnalul ![]() trebuie sa fie 1

logic si semnalul

trebuie sa fie 1

logic si semnalul ![]() zero logic. Bufferele

de intrare sunt dezactivate de poarta G1 si bufferele de

iesire pe coloane sunt activate de poarta G2. Deci cei 8 biti de date

de la adresa selectata sunt trimise prin liniile de I/E pe coloane spre

liniile de date (I/O1 la I/O8) care

functioneaza ca linii de iesire. Pentru scriere semnalul

zero logic. Bufferele

de intrare sunt dezactivate de poarta G1 si bufferele de

iesire pe coloane sunt activate de poarta G2. Deci cei 8 biti de date

de la adresa selectata sunt trimise prin liniile de I/E pe coloane spre

liniile de date (I/O1 la I/O8) care

functioneaza ca linii de iesire. Pentru scriere semnalul ![]() este 0 logic si

este 0 logic si ![]() 1 logic ceea ce duce

la activarea de catre poarta G1 a circuitelor de intrare

si dezactivarea de catre poarta G2 a circuitelor de

iesire. Cei 8 biti de date de la intrare sunt trimise prin circuitul

de control de la intrare si I/E coloane la adresa selectata pentru

memorare.

1 logic ceea ce duce

la activarea de catre poarta G1 a circuitelor de intrare

si dezactivarea de catre poarta G2 a circuitelor de

iesire. Cei 8 biti de date de la intrare sunt trimise prin circuitul

de control de la intrare si I/E coloane la adresa selectata pentru

memorare.

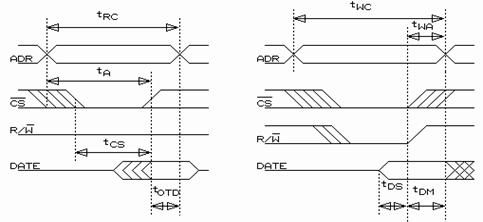

Pentru functionarea corecta a circuitelor de memorie semnalele aplicate la borne trebuie sa satisfaca anumite restrictii de timp. In figura 7.17 sunt prezentate semnalele pentru citirea (a) si scrierea (b) intr-o memorie RAM.

Pentru citire se aplica un

cod de adresa valid pentru un interval de timp tRC - ciclu de

citire care reprezinta intervalul de timp intre doua schimbari

de adresa. Apoi se aplica semnalul ![]() = 0. Dupa un timp

notat tCS - timpul de aparitie a datelor dupa aplicarea

impulsului pe

= 0. Dupa un timp

notat tCS - timpul de aparitie a datelor dupa aplicarea

impulsului pe ![]() , datele valide apar pe liniile de date. Se mai definesc:

, datele valide apar pe liniile de date. Se mai definesc:

- TA - timp de acces la memorie = timpul scurs de la stabilirea adreselor pana la obtinerea datelor valide la iesire;

- tOTD - intervalul de timp cat datele sunt stabile la iesire;

Impulsul de scriere-citire (R/![]() =1) are valoare corespunzatoare citirii din memorie pe

toata durata ciclului.

=1) are valoare corespunzatoare citirii din memorie pe

toata durata ciclului.

a) b)

Figura 7. . Diagrame de timp pentru ciclu de citire si scriere

Pentru scriere se aplica un

cod de adresa valida pentru un interval de timp numit ciclu de

scriere tWC. Apoi semnalele ![]() si R/

si R/![]() (

(![]() ) se pun in zero logic si datele se aplica pe

intrare. Notatiile din figura

7.17.b au urmatoarea semnificatie:

) se pun in zero logic si datele se aplica pe

intrare. Notatiile din figura

7.17.b au urmatoarea semnificatie:

- tWA - intervalul de timp in care adresele trebuie sa ramana stabile in raport cu frontul posterior al impulsului de scriere;

- tW - durata impulsului de scriere;

- tDS - timp de pregatire a datelor in raport cu momentul inscrierii;

- tDM - timp de mentinere a datelor dupa disparitia impulsului de scriere.

Dupa

cum se observa din figura 7.17.b datele ce se inscriu in memorie trebuie

sa ramana stabile un interval de timp tDS + tDM

in jurul frontului posterior al impulsului de scriere. De asemenea impulsul de

scriere R/![]() =0 nu poate veni inaintea stabilirii adreselor si poate

fi simultan cu

=0 nu poate veni inaintea stabilirii adreselor si poate

fi simultan cu ![]() .

.

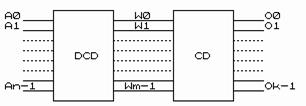

In esenta memoria ROM (Read Only Memory) este un convertor de cod compus dintr-un decodificator si un codificator. Interpretand vectorul de intrare al DCD ca un cod de adresa, datele obtinute la iesirea CD reprezinta informatia inmagazinata la adresa respectiva. Rezulta ca sediul informatiei memorate in ROM este codificatorul, a carui structura determina cuvantul binar de iesire pentru fiecare adresa in parte. Structura codificatorului este stabilita in procesul de fabricatie al CI sau poate fi impusa de utilizator prin programare. In aceste conditii ROM devine o memorie fixa (care poate fi numai citita), nevolatila al carui continut nu se modifica in functionare. O memorie ROM memoreaza date care se folosesc in mod repetat in aplicatii cum ar fi tabele, conversii, sau instructiuni de program pentru initializarea sistemului.

Figura 7.18 prezinta clasificarea memoriilor ROM.

|

ROM | |||||||||||||

|

ROM programat prin masca la producator |

ROM programabil la utilizator (PROM) |

PROM cu stergere (EPROM) |

EPROM cu stergere cu ultraviolete (UV EPROM) |

PROM cu stergere electrica (EEPROM) |

|||||||||

Figura 7. . Familia de circuite ROM

Memoria ROM programata prin masca este tipul in care datele sunt inscrise in timpul procesului de fabricare. Memoriile PROM sau memoriile ROM programabile sunt memoriile in care datele sunt inscrise pe cale electrica de catre utilizator cu ajutorul unui echipament special numit programator de memorii. Ambele tipuri de memorie de mai sus pot fi realizate atat in tehnologie bipolara cat si MOS. Memoria EPROM sau memoria PROM care poate fi stearsa se poate realiza numai in tehnologie MOS. Memoria UV EPROM poate fi programata pe cale electrica de catre utilizator, dar poate fi stearsa numai prin expunere la raze ultraviolete pentru o perioada de cateva minute. Memoria EPROM care poate fi stearsa pe cale electrica se numeste memorie EEPROM sau E2PROM si poate fi stearsa in cateva milisecunde.

Schema bloc a unei memorii ROM este prezentata in figura 7.19. Cele n linii de adresa (intrarile A0, A1,.An-1) sunt decodificate in m = 2n linii de cuvant (W0,.,Wm-1), iar (CD), care constituie matricea de memorie, furnizeaza la iesire m cuvinte de cate k biti (O0,.,Ok-1). Capacitatea C a unei memorii fixe este determinata de numarul de biti ai matricei de memorie (C=mk). Ea se exprima de cele mai multe ori in kilobiti (1 kbit = 1024 biti).

Figura 7. . Schema bloc a unei memorii ROM.

Din punctul de vedere al tehnologiei se deosebesc memorii ROM realizate in tehnologie bipolara sau in tehnologie MOS. Primele sunt utilizate in aplicatiile in care timpul de acces la informatia memorata trebuie sa fie mic (zeci de ns), iar cea de a doua categorie este proprie aplicatiilor care necesita capacitati mari de memorare la un timp de acces de ordinul sutelor de ns. Programarea memoriilor ROM este procesul prin care se stabileste continutul memoriei, in conformitate cu aplicatia avuta in vedere, actionand asupra codificatorului (matricei de memorie). Metodele folosite pentru programare depind de tipul memoriei.

Memoriile bipolare pot fi programate atat la producator prin masca (Mask ROM) cat si la utilizator (PROM), prin aplicarea unor proceduri de programare.

Considerand codificatorul realizat cu tranzistoare in conexiunea colector comun, fiecarui bit corespunzandu-i un tranzistor si reprezentand doar tranzistoarele ce corespund unei singure linii de cuvant Wp (figura 7.20). In primele etape ale procesului tehnologic se realizeaza matricea de memorie lasand intrerupte legaturile bazelor tranzistoarelor la linia de cuvant (sau ale emitoarelor la linia de bit L0, L1,L2,L3).

Figura . ROM programat prin masca |

Programarea constituie o etapa a procesului de fabricatie in care cu ajutorul unei masti, in conformitate cu cerintele utilizatorului, se realizeaza unele dintre legaturile l0,..,l3 pentru fiecare cuvant in parte. De exemplu daca liniei Wp ii corespunde cuvantul 1010, se realizeaza conectarea bazei tranzistoarelor T3 si T1. Astfel la selectia liniei de cuvant Wp tranzistoarele T3 si T1 intra in conductie si caderea de tensiune pe rezistentele din emitor transmit un 1 logic pe liniile de bit respective (O3 si O1). Celelalte tranzistoare fiind blocate potentialul liniilor O2 si O0 este zero. Principalul dezavantaj al acestei metode este costul ridicat, mai ales pentru serii mici de circuite.

|

|

|

Figura 7. . ROM programat la utilizator |

In figura 7.21 se prezinta partea corespunzatoare unei linii de cuvant pentru codificatorul unei memorii fixe programabile de catre utilizator (PROM). Aici elementele de memorie pot fi considerate pelicule subtiri de crom-nichel (f0, f1, f2, f3), care pot fi intrerupte sau nu de catre utilizator, prin trecerea unui curent de programare Ip, intens (zeci sau sute de mA) si de scurta durata (zeci de ms) prin circuitul marcat cu linie intrerupta. Diodele d au rolul de a impiedica ramificarea curentului de programare spre f2, f1 si f0. Daca se doreste programarea cuvantului 1010 se intrerup f3 si f1. La selectia liniei de cuvant tranzistorul T intra in conductie si pune la masa liniile de bit care au conexiunea neintrerupta (O2 si O0), restul liniilor fiind in 1 logic in mod permanent. Evident ca legaturile intrerupte nu mai pot fi refacute si modificarea continutului memoriei programate se poate face numai daca fata de prima programare sunt necesare doar treceri ale valorii unor biti de pe 0 pe 1.

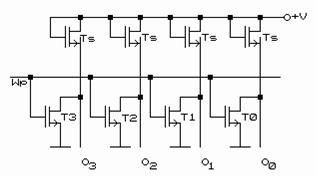

La fel ca si memoriile bipolare, memoriile realizate in tehnologie unipolara pot fi: programabile prin masca si programabile la utilizator.

Aceasta se face de

producator pe baza tabelului privind continutul matricei de memorie,

furnizat de utilizator. In primele etape ale procesului de fabricatie se realizeaza toate

tranzistoarele MOS din nodurile matricei codificatorului, cu exceptia

depunerii stratului izolant al portii si a electrodului poarta.

In etapa de programare, tranzistoarele inactive se realizeaza cu o grosime

mai mare a stratului izolant al portii, iar cele active cu o grosime mai

mica. In situatia prezentata in figura 7.22, pentru programarea

cuvantului 1010, tranzistoarele T3 si T1 vor f

realizate cu un strat izolant al portii de grosime mai mare, ramanand

blocate indiferent de nivelul logic aplicat la linia de cuvant Wp.

In aceasta figura cu Ts s-au notat tranzistoarele de

sarcina.

Aceasta se face de

producator pe baza tabelului privind continutul matricei de memorie,

furnizat de utilizator. In primele etape ale procesului de fabricatie se realizeaza toate

tranzistoarele MOS din nodurile matricei codificatorului, cu exceptia

depunerii stratului izolant al portii si a electrodului poarta.

In etapa de programare, tranzistoarele inactive se realizeaza cu o grosime

mai mare a stratului izolant al portii, iar cele active cu o grosime mai

mica. In situatia prezentata in figura 7.22, pentru programarea

cuvantului 1010, tranzistoarele T3 si T1 vor f

realizate cu un strat izolant al portii de grosime mai mare, ramanand

blocate indiferent de nivelul logic aplicat la linia de cuvant Wp.

In aceasta figura cu Ts s-au notat tranzistoarele de

sarcina.

In tehnologia MOS exista doua metode pentru realizarea memoriilor fixe, programabile pe cale electrica de catre utilizator (EPROM). Prima dintre ele este similara cu cea folosita la programarea la utilizator a memoriilor ROM bipolare si consta in arderea unor legaturi fuzibile prin intermediul unui curent controlat. Cea de a doua se bazeaza pe folosirea unei porti flotante neconectate la circuitul exterior si plasata izolat intre poarta propriu-zisa si substrat. In cazul utilizarii tranzistoarelor cu canal N, incarcarea portii flotante cu o sarcina electrica negativa echivaleaza cu cresterea tensiunii de prag poarta-sursa. Aceasta crestere poate fi atat de mare incat tranzistorul ramane blocat chiar daca la poarta se aplica un potential corespunzator nivelului logic superior. Deci, incarcarea cu sarcina negativa a portii flotante duce la dezactivarea tranzistorului respectiv. In procesul de programare la utilizator, prin aplicarea impulsurilor de programare este realizata dezactivarea unor tranzistoare din nodurile matricei codificatoare, in conformitate cu programul ce urmeaza sa fie inscris. Stergerea informatiei inscrise, adica readucerea tuturor tranzistoarelor in stare activa, se poate face prin iradierea matricei de memorie cu radiatii ultraviolete prin fereastra de cuart cu care este prevazuta capsula. Dupa stergere, memoria poate fi programata din nou. Operatiile de stergere si reprogramare pot fi repetate de mai multe ori.

In afara de memoriile ROM amintite mai sus, sunt de mentionat si memoriile EAROM (Electricaly Alterabile ROM) sau EEPROM (Electricaly Erasable PROM) realizate in tehnologie MOS, prevazute cu posibilitatea stergerii pe cale electrica.

In figura 7.23 este aratata organizarea tipica a unei memorii ROM de 8 kbiti.

![]()

Figura 7. .Organizarea tipica a unei memorii de 8 kbiti

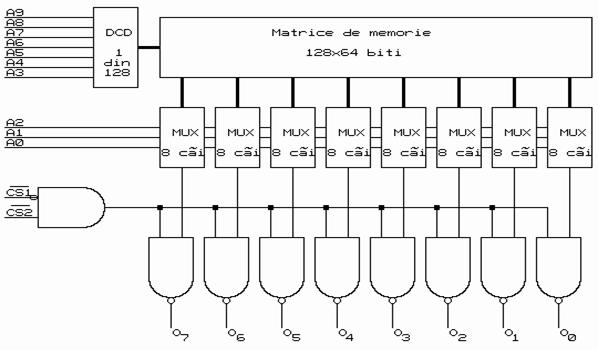

Se constata ca selectia unui cuvant de iesire de 8 biti (O7, .,O0) nu se face cu ajutorul unui DCD cu 1024 linii de iesire ci, in scopul reducerii numarului de porti folosite sunt utilizate: un DCD cu 128 de linii si 8 MUX cu 8 cai. Intrarile CS1 si CS2 permit selectarea sau deselectarea capsulei de memorie prin intermediul celor 8 amplificatoare de iesire (circuite SI-NU) care sunt prevazute cu etaje de iesire avand colectorul in gol sau sunt circuite cu trei stari. Aceste doua tipuri de circuite de iesire fac posibila interconectarea iesirilor a mai multor capsule de memorie respectiv conectarea capsulei la o magistrala.

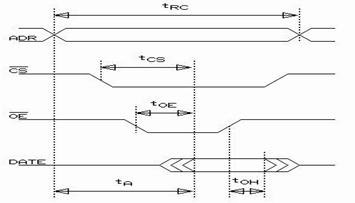

Pentru memoriile ROM un ciclu tipic este dat in figura 7.24. Semnificatia notatiilor este urmatoarea:

- tRC - durata ciclului de citire;

- tA - timp de acces la memorie;

- tCS - intervalul de

timp in raport cu ![]() dupa care apar

date stabile la iesire;

dupa care apar

date stabile la iesire;

- tOE - intervalul de

timp dupa care apar date stabile la iesire in raport cu impulsul ![]() ;

;

- tOH - timp de

mentinere a datelor la iesire dupa disparitia impulsului ![]() .

.

Impulsul de comanda a

iesirii OE in general se poate aplica simultan cu ![]() .

.

Figura 7. . Ciclu tipic pentru citirea unei memorii ROM

In cazul memoriilor programabile la utilizator, operatia de programare se efectueaza in stare neselectata a capsulei, iar pentru memoriile EPROM, capsula este prevazuta cu o intrare suplimentara la care sunt aplicate impulsurile de programare.

Figura 7. . Structura interna a unei memorii PROM, EPROM

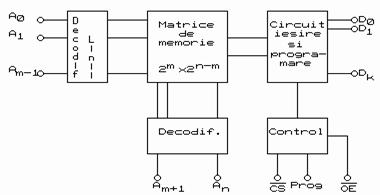

Structura interna a unei

memorii PROM, EPROM este prezentata in figura 7.25. Circuitul de

iesire trebuie sa asigure posibilitatea programarii memoriei in

cazul memoriilor PROM sau EPROM. Semnalul de control ![]() face selectia

circuitului controland si starea iesirilor (mare impedanta

sau conectate la magistrala de date) in timp ce semnalul

face selectia

circuitului controland si starea iesirilor (mare impedanta

sau conectate la magistrala de date) in timp ce semnalul ![]() (output enable)

controleaza numai starea circuitelor de iesire. Pentru

(output enable)

controleaza numai starea circuitelor de iesire. Pentru ![]() =1 iesirea este in stare de mare impedanta.

Acelasi lucru se intampla si daca

=1 iesirea este in stare de mare impedanta.

Acelasi lucru se intampla si daca ![]() =1 indiferent de valoarea lui

=1 indiferent de valoarea lui ![]() .

.

Trebuie amintit ca in

general deselectarea circuitului (![]() =1) atrage dupa sine si scaderea puterii

consumate de circuit de la sursa de alimentare fara a se altera

informatia memorata. Acest lucru il intalnim atat la memoriile RAM

cat si ROM (PROM, EPROM).

=1) atrage dupa sine si scaderea puterii

consumate de circuit de la sursa de alimentare fara a se altera

informatia memorata. Acest lucru il intalnim atat la memoriile RAM

cat si ROM (PROM, EPROM).

Forma impulsurilor si duratele lor pentru programarea unei memorii (PROM, EPROM) se da in cataloagele circuitelor respective.

Avand in vedere dublul caracter al memoriilor ROM (PROM, EPROM), de convertor de cod si memorie, aria de utilizare a acestora este extrem de larga. Dintre principalele aplicatii se pot mentiona urmatoarele:

Memorarea instructiunilor si datelor in sisteme de calcul si automate secventiale.

Efectuarea transformarilor de adresa si inmagazinarea microinstructiunilor, in microprogramare.

Implementarea CLC cu un numar mare de variabile de intrare si cu mai multe iesiri. In cazul acestei aplicatii este de remarcat faptul ca datorita structurii interne a memoriei ROM fiecare linie de cuvant reprezinta un termen al formei canonice, iar codificatorul permite insumarea acestor termeni in conformitate cu tabelul de adevar, eliminandu-se necesitatea minimizarii.

Conversia de cod este de asemenea una din aplicatiile frecvente ale memoriilor fixe. Sunt de amintit aici convertoarele pentru afisarea prin 7 segmente sau 35 de puncte, precum si generatoarele de caracter care deservesc sistemele pentru afisarea alfanumerica a datelor pe ecranul unui tub catodic.

Realizarea unor tabele de functii in cadrul sistemelor de calcul sau conducere numerica, care constituie in fond un sistem de conversie a codului binar reprezentand argumentul functiei in codul de iesire care furnizeaza valorile corespunzatoare ale functiei. Se realizeaza astfel de tabele pentru functii frecvent intalnite ca cele logaritmice, trigonometrice sau exponentiale.

Generarea unor secvente de impulsuri cu ajutorul memoriei ROM, realizabila prin programarea corespunzatoare a acesteia si modificarea secventiala a adresei de intrare cu ajutorul unei numarator binar. La cele k iesiri de date se poate obtine acelasi numar de secvente distincte.

Este de mentionat ca in toate aplicatiile memoriei fixe este necesar sa se urmareasca utilizarea cat mai completa a capacitatii sale, respectiv sa se adopte masuri de reducere a capacitatii necesare prin codificare la intrare sau decodificare la iesire.

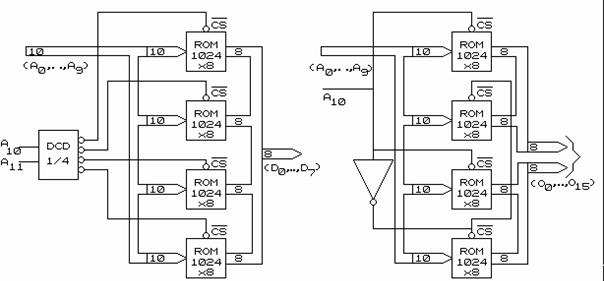

Data fiind capacitatea unei capsule de memorie prin produsul dintre numarul de cuvinte m si numarul de biti ai cuvantului de iesire k, exista posibilitatea de a realiza o memorie de capacitate mai mare prin utilizarea unui numar sporit de capsule. Extinderea capacitatii se poate obtine actionand asupra numarului de cuvinte, lasand numarul bitilor pe cuvant neschimbat (extindere la intrare sau de adresa), modificand numarul bitilor de iesire la un numar neschimbat de cuvinte (extindere la iesire), respectiv atat prin modificarea lui m cat si a lui k (extindere mixta). Figura 7.26 ilustreaza extinderea de adresa de la o capacitate de (1x8) Kbiti pe capsula la (4x8) Kbiti, iar in figura 7.27 este prezentata extinderea mixta de la (1x8) Kbiti pe capsula la (2x16) Kbiti.

![]()

|

Figura 7. . Extinderea de adresa a capacitatii memoriilor |

Figura 7. . Extinderea mixta a capacitatii memoriilor |

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |