Circuite TTL

Caracteristica de intrare

arata dependenta tensiunii de intrare in functie de curentul de intrare ui=f(ii) ; ii=f(ui);

a) toate intrarile au valoarea "1"; (SI NU - cand pe intrarile portii se aplica tensiune de nivel inalt "1" curentul pe fiecare intrare este 40μA)

b) o intrare la "0" si restul intrarilor la "1" ; IiH = 40μA ; IiL = 1,6 mA

Caracteristica de iesire

a) tensiunea de iesire "0" logic

b)

tensiunea

de iesire "1" log ic

ic

Fan-out - reprezina numarul de porti logice pe care le poate

comanda poarta logica (fara sa o distruga,

fara a depasii curentii)

Timpul de propagare a semnalului printr-o poarta logica

Pentru poarta TTL standard timpul de propagare este de 10 ns.

Puterea medie consumata este de 10 mW.

tpLH - timp de propagare la variatia iesirii de la nivel L la

nivel H.

tpHL - timp de propagare la variatia iesirii de la nivel H la

nivel L.

De regula cei doi timpi nu sunt egali si sunt influentati de

sarcina circuitului. Valorile date in catalog se refera

la o incarcare nominala a circuitului ( de asemenea indicata

in catalog ).

Pentru masurarea timpului de propagare a informatiei (timpul de intarziere la propagarea informatiei logice) se simuleaza incarcarea circuitului la un fan-out de 10.

Pentru poarta TTL standard valorile tipice sunt :

- tpLH = 12 ns

- tpHL = 8 ns

![]()

Tipuri de circuite TTL

Circuite Trigger-Schmitt

In cazul unor semnale de intrare cu fronturi lente (durata de crestere de la minim la maxim este mai mare de 100ns) iesirea portilor logice poate sa comute in mod eronat. Motivul functionarii eronate este dat de intrarea in conductie in mod simultan a celor 3 tranzistoare din etajul defazor si etajul final a portii. Pentru a evita acest comportament defectuos se implementeaza in structura interna un circuit de tip Trigger-Schmitt, care introduce in caracteristica de transfer un histerezis.

Poarta TTL de mica putere(TTL-LP)(Low Power)

In scopul reducerii puterii medii consumate, s-au proiectat circuite TTL de mica putere. Acest lucru s-a realizat prin marirea valoarii rezistentei de pe poarta TTL standard intre 4 si 10 ori.

|

tp |

R1 R2 R3 R4 |

PmW |

|

|

10 ns |

TTL | ||

|

20 ns |

TTL-LP 4XR | ||

|

33 ns |

TTL-LP 10XR |

Porti TTL de viteza mare(HTTL)

Pentru a mari viteza de lucru a portilor TTL se modifica schema portii TTL standard in felul urmator:

tranzistorul T3 se inlocuieste cu o structura Darlington formata din T3, T5 si R6;

rezistenta R4 din circuitul portii standard se inlocuieste cu o rezistenta neliniara formata din R4, R5, T6

Structura Darlington are o rezistenta de iesire RCE de valoare mai mica decat valoarea rezistentei tranzistorului T3 din schema standard. Acest lucru face ca incarcarea capacitatii de sarcina sa aiba loc mai rapid si deci se micsoreaza timpul de comutatie. Pe de alta parte tranzistorul T3 din actuala structura nu se poate satura datorita faptului ca intre colector si baza avem tensiunea de saturatie a tranzistorului T5. Neintrand in saturatie tranzistorul T3 comuta rapid din conductie in blocare, situatie care determina tot o micsorare a timpului de comutare.

Rezistenta neliniara formata din R4, R5 si T6 lucreaza astfel:

- la intrarea in conductie a lui T4 valoarea rezistiva este mare, determina ca tot curentul de emitor al lui T2 sa intre in baza lui T4 si sa il satureze rapid.

- la comanda de blocare a lui T4 rezistenta echivalenta a ansamblului R4, R5 si T6 este mica determinand evacuarea rapida a sarcinii stocate in baza lui T4, deci iesirea rapida din saturatie a lui T4.

- jonctiunea baza-emitor a tranzistorului T3 indeplineste rolul diodei D din schema portii TTL standard.

O astfel de configuratie are timpul de propagare de 6 ns si puterea disipata de 22mW.

Poarta TTL - Schottky (TTL-S)

reduce timpul de propagare prin evitarea intrarii in saturatie a tranzistoarelor. Acest lucru este posibil prin utilizarea in paralel cu jonctiunea baza-colector a tranzistorului a unei diode Schottky.

Datorita faptului ca dioda se polarizeaza la 0,3 V, jonctiunea baza-colector nu va avea niciodata tensiunea necesara intrarii in saturatie.

tp= 3ns, Pd=22mW

Advanced Low Schottky - 4ns/1mW

Circuite TTL cu colectorul in gol

Se considera iesirile a doua porti TTL standard conectate impreuna, o iesire avand 1 logic si cealalta 0 logic. Intereseaza valoarea curentului

Doua circuite TTL cu iesirile legate

![]()

poarta care este in "0" se distruge;

circuitele logice TTL nu se conecteaza

cu iesirile in paralel. Pentru a utiliza circuitele conectate in paralel

s-au proiectat circuite logice cu colectorul in gol sau circuite logice cu 3

stari. Circuitul standard pentru poarta cu colectorul in gol este

urmatorul:

circuitele logice TTL nu se conecteaza

cu iesirile in paralel. Pentru a utiliza circuitele conectate in paralel

s-au proiectat circuite logice cu colectorul in gol sau circuite logice cu 3

stari. Circuitul standard pentru poarta cu colectorul in gol este

urmatorul:

Rezistenta R se conecteaza in

exteriorul circuitului si se calcueaza in functie de

numarul de porti logice conecatate in paralel, astfel incat sa

asigure pragurile logice la iesire si la intrare. Aceasta

rezistenta se poate conecta la o sursa de tensiune diferita

de sursa de +5 V a circuitului .Acest lucru este un avantaj pentru a conecta un

circuit cu colector in gol cu circuite din alte familii logice .Simbolul unei

porti cu conectori in gol :

Presupunem ca o sa conectam un numar de porti logice:

Cazul I:

Toate cele M porti se afla in 1 logic ;

Cazul II:

O singura poarta din cele M de

iesire este in 0 restul in 1:

O singura poarta din cele M de

iesire este in 0 restul in 1: ![]()

UOLmax

Aplicatii ale circuitelor cu colectorul in gol

Exista circuite cu colectorul in gol care au drept tranzistor de iesire un tranzistor de putere (ce poate rezista blocat pentru tensiuni de colector mari de 15 V, 30 V, sau care pot debita curenti mari). Astfel de circuite cu colectorul in gol pot fi utile in cazul interfatarii cu alte tipuri de circuite (fie logice fie analogice), caz in care rezistenta R exterioara poate fi conectata la o sursa V exterioara marita si se dimensioneaza in mod adecvat dupa aceleasi principii care au fost expuse mai sus.

Dintre aplicatiile circuitelor cu colectorul in gol amintim:

- Realizarea functiei SI cablat fara a necesita un circuit logic suplimentar. Solutia este adoptata si in interiorul unor structuri logice mai complexe (de exemplu, in cazul circuitelor reprogramabile GAL, in implementare cu tranzistoare MOS, in varianta similara denumita 'open drain').

- Circuite de interfata cu alte circuite logice sau analogice.

Dezavantajele legate de folosirea acestor circuite ar fi:

- impedanta de iesire mare in starea H (In acest caz impedanta de iesire este tocmai R exterioara care este mult mai mare decat impedanta de iesire a repetorului pe emitor din structura in contratimp);

timpi de propagare mari, mai ales la comutarea iesirii din L in H (capacitatea parazita se incarca prin impedanta de iesire marita);

- imunitate scazuta la zgomot (tot datorita impedantei de iesire marita);

- necesitatea folosirii unei rezistente exterioare care trebuie calculata de fiecare data, in functie de conditiile de lucru.

Observatie

Circuitele cu trei stari si cu colector in gol exista in toate seriile TTL, constructia si functionarea lor respectand particularitatile seriei si ale acestor tipuri de circuite.

Circuite cu 3 stari

- porti normale care au in plus un pin de selectie CIP select. Cand acest pin este coectat la 1 logic poarta functioneaza ca o poarta normala, cand pinul CIP select este in 0 logic poarta trece in a treia stare de impedanta ridicata fiind inactiva pe linia 0 date.

Stari

-0 (primeste curent),

-1(debiteaza curent),

- High-Z (nici nu cedeaza nici nu primeste curent).

Cs - CIP select (selector cip)

Ts - tranzistor de selectie

Ds - dioda de selectie

Daca Cs= "1", atunci tranzistorul de selectie Ts si dioda de selectie Ds sunt blocate, jonctiunea BE corespunzatoare tranzistorului T1 este blocata. In aceste conditii poarta logica functioneaza conform starii logice a semnalului ui1 si ui2. Daca Cs="0", tranzistorul T1 se va satura indiferent de semnalele ui1 si ui2, T2 va fi blocat si T4 va fi blocat, Ts se satureaza, Ds se deschide (conduce) si potentialul bazei T3 va scade (UM scade) astfel incat T2-T3 se blocheaza. In aceste conditii circuitul se afla in Hi-z (stare de mare impedanta). Iesirea portilor logice este izolata si fata de masa si fata de +U. Astfel de circuite se utilizeaza pentru legarea mai multor sisteme la aceeasi magistrala. O aplicatie a circuitelor cu 3 stari o reprezinta sistemul de transmisie de date bidirectionale.

(Bidirectionale - primesc si emit; activez numai portile care ma intereseaza, sunt activate prin CIP select. Celelalte avand pe magistrala starea de inalta impedanta si nu influenteaza magistrala; receptoarele < 10, emitator - 1 are CIP select pe 1)

Pentru inversor tabelul de adevar este: (circuitul este selctat cand Cs=1, lucreaza normal)

|

CS / in |

Out |

|

0 0 0 1 |

Hi-z Hi-z |

|

1 0 1 1 |

Un singur semnal Cs trebuie sa ia valoarea 1 la un moment dat, celelalte 2 trebuie sa ia valoarea 0.

Ex: Cs1 = 1, Cs2 = Cs3 = 0, atunci : S1 transmite prin inversorul I11, iar celelalte sisteme S2 si S3 receptioneaza informatii prin I22 si I32. Cs2 = 1, Cs3 = Cs1 = 0

Reguli de utilizare ale circuitelor integrate TTL

In sistemele logice pot sa apara mai multe tipuri de zgomote (tensiuni si curenti paraziti) care sa deranjeze functionarea acestora. Astfel se pot distinge:

zgomote exterioare, care intervin din mediul exterior prin radiatii, putand induce comutari nedorite. Pot fi produse de exemplu, de comutatoare mecanice, statice, periile motoarelor etc;

zgomote provenite de la reteaua de alimentare induse tot prin radiatii si avand specific frecventa retelei;

diafonia - zgomote induse in caile de semnal ale circuitelor logice de catre caile de semnal alaturate;

reflexii pe liniile de transmisie - datorat neadaptarii liniilor de transmisie; pot produce oscilatii si supracresteri ale semnalului;

varfuri tranzitorii ale curentului de alimentare - datorat comutarii etajului de iesire dintr-o stare logica in alta.

Ca reguli de proiectare a cablajului imprimat astfel incat sa se asigure protectia contra acestor zgomote, se recomanda:

Decuplarea alimentarii

Un factor de stabilizare de 5% este suficient pentru sursele de alimentare. Este deosebit de important insa, sa se realizeze decuplarea alimentarii la intrarea pe placa imprimata. Aceasta se poate realiza cu o inductanta de 2,10mH si un condensator C1 de valori 10 mF in

paralel cu unul de valoare 10, 100nF (C2 - ceramic) pentru inalta frecventa. In cazul circuitelor mai complicate este de asemenea recomandabil sa se foloseasca decuplarea cu condensatoare distribuite pe intregul cablaj, in imediata apropiere a circuitelor TTL, cel putin cate 100nF la 20 porti.

- 50 μF / 16V

Traseul de masa este recomandabil sa fie mai gros si sa nu se formeze o bucla de masa in jurul placii. In cazul circuitelor dublu placate, ambele fete ale placii sa fie aduse la sistemul de masa prin borne separate. Este recomandabil de asemenea, sa existe un plan de masa.

Ecranarea. In cazul functionarii in medii industriale cu radiatii perturbatoare puternice este obligatorie ecranarea montajului logic cu ecrane din metal feros (numai el asigura ecranare contra campurilor magnetice). Intreg sistemul de ecrane trebuie legat la o singura borna si aceasta plasata cat mai aproape de borna de pamant (de care evident este legata). De asemenea, se are in vedere ecranarea si filtrarea sistemului de alimentare de la retea.

Este bine de retinut ca datorita impedantelor de intrare scazute, circuitele TTL sunt mai putin sensibile la zgomote decat circuitele CMOS sau chiar alte circuite logice.

Liniile de semnal. In cazul traseelor paralele este bine sa se evite apropierea excesiva intre linii pe distante mari. In cazul folosirii legaturilor prin cablu, pentru lungimi mici (sub 25 cm) se pot folosi conexiuni din conductoare simple (neecranate) fara precautii deosebite. Conductoarele cu semnal in acelasi sens pot fi plasate la distante 0,3 ~ 5 mm (trunchi comun). Conductoarele cu semnale de sensuri opuse trebuie sa fie la cel putin 10 mm distanta sau separate de un plan de masa. Daca legatura depaseste 50 cm este obligatorie folosirea unui cablu coaxial avand ecranul legat la masa cat mai aproape de punctul de masa al circuitului integrat, in ambele capete (si langa poarta emitatoare si langa poarta receptoare) si, de asemenea, avand ecranul decuplat prin condensator la sursa +VCC.

Intrari si porti neutilizate

In cazul circuitelor TTL o intrare lasata in aer echivaleaza cu aplicarea unui semnal 1 logic. In cazul in care raman intrari nefolosite nu este recomandabil ca ele sa fie lasate in gol chiar daca aceasta nu deranjeaza din punct de vedere logic. Se recomanda legarea lor la +VCC (deci tot la 1 logic) fie direct, fie printr-o rezistenta de cca. 1kW. Intrarile nefolosite pot fi legate impreuna cu celelalte intrari ale portii daca nu se depaseste fan-out-ul portii de comanda. Se reaminteste ca prin legarea impreuna a mai multor intrari ale aceleiasi porti, curentul de intrare pentru 0 logic ramane acelasi in schimb curentul de intrare pentru 1 logic creste proportional cu numarul intrarilor.

In cazul in care raman porti nefolosite intr-un circuit integrat, se recomanda legarea la masa a intrarilor acestora.

Se reaminteste faptul ca, datorita etajului de iesire in contratimp, este cu desavarsire interzis a se lega impreuna mai multe iesiri de circuite TTL.

Variante circuite TTL:

-seria comerciala: U = 4,75 ÷ 5,25V; T0C = 00 ÷ 750C

-seria militara: U = 4,5 ÷ 5,5V; T0C = -500 ÷ 1250C

Circuite realizate in tehnologia unipolara - circulatia curentului prin dispozitivele unipolare se face pe baza unui singur tip de purtatori (goluri sau electroni)

Circuitul CMOS - circuitul de baza utilizat este inversorul CMOS

ui=0; Qn blocat; Qp conduce; u0=+U

ui=1; Qn conduce; Q'p blocat; u0=0

Poarta SI-NU

|

u1 |

u2 |

u3 |

u1 = 0 => QP1 conduce, Qn1 blocat

u2 = 0 => QP2 conduce, Qn2 blocat

Poarta SAU-NU - "nu" scoate 1 pe iesire cand ambele intrari sunt pe 0;

"SAU" scoate 1 pe

iesire daca una din intrari este pe 1.

1.

|

u1 |

u2 |

u3 |

|

u1 |

u2 |

u3 |

u0 |

|

|

|||

|

| |||

![]()

![]()

Circuite basculante

- sunt acele circuite logice secvențiale care trec dintr-o stare in alta. In functie de modalitatea de trecere si de stabilitatea starii exista urmatoarele tipuri de circuite basculante :

1. CBB(circuite basculante bistabile) - sunt acele circuite logice care au 2 stari stabile (0 și 1 logic), trecerea dintr-o stare in alta facandu-se datorita semnalelor de comanda aplicate la intrari. Se mai numesc si circuite de memorare.

2. CBM(circuite basculante monostabile) - sunt circuitele care au o stare stabila si o stare cvasistabila. Trecerea din starea stabila in starea cvasistabila se face cu un semnal de comanda, iar in trecerea inversa se face automat in functie de componentele circuitului.

3. CA(circuite astabile-multivibratoare) - prezinta 2 stari cvasistabile, trecerea dintr-o stare in alta facandu-se in mod automat (periodic) in functie de componentele circuitului.

Circuitele basculante bistabile(CBB)(discrete, integrate) (se pot realiza in varianta asincrona,

Circuitele basculante bistabile(CBB)(discrete, integrate) (se pot realiza in varianta asincrona,

sincrona sau ,Master- Slave'.)

Bistabilul de tip RS

-se poate realiza cu porți SI-NU si SAU - NU

|

|

|

|

|

|

neperminsa |

|||

|

starea nu se schimba |

|||

- este un circuit transparent in sensul ca orice comanda de la intrare se transmite la iesire.

- nu se face distinctie intre intrarile care arata cum sa comute iesirea si cand sa comute iesirea (nu are intrari de sincronizare = varianta asincrona).

- cunoscut si sub denumirea de ,lach' (,zavor'), datorita proprietatilor sale de memorare.

|

R |

S |

|

|

|

starea nu se schimba |

|||

|

neperminsa |

|||

![]()

![]()

Schema bloc a bistabilului de tip RS

Bistabilul de tip RST

comuta in ritmul intrarii de clock sau tact T (in functie de semnalul de intrare de ceas).

face distinctie intre intrarile care arata cum sa comute iesirea (intrarile S si R) si cele care arata cand sa comute iesirea (intrarea T)

nu elimina starea nepermisa (situatia de nedeterminare)

|

|

R |

|

|

|

|

starea nu se schimba |

||||

|

starea nu se schimba |

||||

|

comanda neperminsa |

||||

Schema bloc

Bistabilul D (date)

La bistabilul RST situatia R = S = 1 este nepermisa. Eliminarea acestei situatii se poate face prin obtinerea bistabilelor de tip D si J-K.

La bistabilul D informatia de la intrarea de date D se transmite la iesire daca impulsul de tact este activ. In caz contrar, daca impulsul de tact nu este activ, informatia de la iesire se pastreaza.

|

T D |

Q |

|

0 1 0 1 |

stare neschimbata stare neschimbata 1 |

![]()

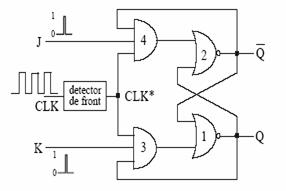

Bistabil JK (Jam-Keep)

Inconvenientul circuitelor basculante RST, referitor la starea de nedeterminare a iesirilor atunci cand cele doua intrari sunt aduse simultan la nivel logic 1, este inlaturat prin folosirea la intrare a doua porti logice SI cu trei intrari si a doua circuite de reactie, asa cum se arata in figura urmatoare.

|

T J K |

Qt+1 |

|

0 0 0 1 1 0 1 1 |

Stare neschimbata Qt |

|

0 0 0 1 1 0 1 1 |

Qt

|

Bistabilul T (trigger)

- se obtine prin conectarea impreuna a intrarilor de date ale bistabilului J-K

|

T |

Q |

|

stare neschimbata starea se completeaza |

- cu intrare de date

|

Clk |

Q |

|

stare neschimbata starea se completeaza |

- fara intrare de date

conversia D - T

fara intrare de date cu intrare de date

Circuite MASTER-SLAVE

elimina neajunsurile legarii in cascada a mai multor CBB de tip RS (posibila situatie de nedeterminare a starilor fiecarui CBB)

primul CBB, numit CBB master (RSTM) este comandat de intrarile de date R si S, iar al doilea CBB din secventa se numeste CBB slave (RSTS) si este comandat de iesirile CBB master.

cand

semnalul de ceas se afla in "1" circuitul RSTM comuta

iesirile ![]() si

si ![]() conform R si S de

la intrare;

conform R si S de

la intrare;

deoarece

semnalul de ceas al RSTS, TS

este in "0", el nu este transparent si iesirile ![]() si

si ![]() nu se modifica;

nu se modifica;

la trecerea semnalului de ceas T in "0" RSTM nu mai este transparent iar RSTS devine transparent;

in aceste conditii iesirile RSTM vor determina starea RSTS la iesire. Am obtinut astfel un circuit care comuta pe front.

Starea M - S poate fi folosita in constructia tuturor tipurilor de bistabil situatie in care nu mai sunt transparente si comuta pe front.

- datele aplicate la intrare sunt luate in considerare atunci cand semnalul de clock creste in 1, iar rezultatul este reflectat la iesire abia cand semnalul de clock devine 0. Datorita acestei particularitati, semanlele la intrare trebuie sa fie stabile inaitea aparitiei frontului pozitiv si starea intrarii nu trebuie sa se schimbe inainte de aparitia frontului negativ al pulsului. Daca nu se respecta aceasta restrictie pot aparea raspunsuri necontrolate.

Intrarile asincrone

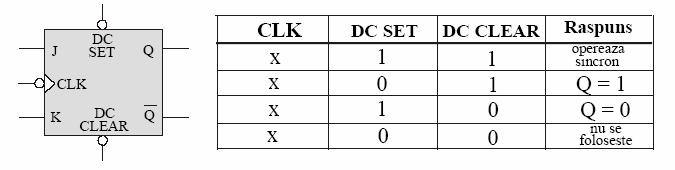

Pe langa intrarea de sincronizare (de tact sau de clock) si intrarile de date (sincronizate), CBB-urile pot fi prevazute si cu intrari asincrone de control care opereaza independent de intrarile sincronizate si de semnalul de tact. Ele se mai numesc intrari prioritare de inscriere (PRESET) si de stergere (CLEAR) si pot fi active atunci cand sunt la nivel logic 0 sau la nivel logic 1. In figura urmatoare este prezentat simbolul unui CBB JK cu doua intrari asincrone, active atunci cand sunt la nivel logic 0, iar alaturat tabelul sau de adevar. Simbolul x din tabel ne arata ca intrarile asincrone pot actiona asupra iesirilor in orice moment de timp, independent de semnalul de tact.

In stare normala intrarile asincrone

sunt mentinute la nivelul logic 1 neafectand

functionarea sincrona a CBB. Aducerea intrarii asincrone DC SET

la nivel logic 0 va aduce iesirea CBB in starea Q = 1, ![]() = 0, deci informatia este inscrisa la

iesirea normala. Activarea intrarii DC CLEAR are ca efect

stergerea informatiei (daca ea exista) de la iesirea

normala. Trebuie mentionat faptul ca intrarile asincrone

raspund si la semnale continue de tensiune (nu numai la impulsuri),

astfel incat un CBB poate fi mentinut intr-o anumita stare un

interval de timp oricat de lung.

= 0, deci informatia este inscrisa la

iesirea normala. Activarea intrarii DC CLEAR are ca efect

stergerea informatiei (daca ea exista) de la iesirea

normala. Trebuie mentionat faptul ca intrarile asincrone

raspund si la semnale continue de tensiune (nu numai la impulsuri),

astfel incat un CBB poate fi mentinut intr-o anumita stare un

interval de timp oricat de lung.

Circuite basculante monostabile(CBM)

Circuitele monostabile au o sigura stare stabila, trecerea din starea stabila in starea cvasistabila se face cu ajutorul unui impuls de comanda iar timpul in care circuitul ramane in starea cvasistabila este determinat de elementele externe ale circuitului.

CBM pot fi realizate cu circuite integrate si elemente discrete.

Circuitul BA555 (LM555)

![]()

![]()

![]()

![]()

Cele 3 rezistente

de 5kΩ determina doua praguri de tensiune fixe: ![]()

Comparatorul AO1

![]()

Comparatorul AO2

![]()

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |