Este un program care modeleaza comportamentul unui circuit care poate sa contina orice combinatie de dispozitive analogice sau digitale. Este utilizat pentru testarea si rafinarea schemei, inainte de implementarea fizica.

Facilitati:

Se pot schimba caracteristicile fara a se crea componente noi. PSpice A/D dispune de modele ai caror parametri pot fi modificati. Comportamentul digital sau analogic poate fi modelat putandu-se descrie blocuri functionale din circuit, cu ajutorul unor expresii sau functii matematice.

Tabel 1 Analize de baza

|

Analiza de curent continuu |

Pspice A/D calculeaza: |

|

DC sweep |

Tensiuni de stare stabila, curenti si stari logice |

|

Bias point detail |

Punct stabil (ca valoare), in plus fata de ceea ce se calculeaza automat, in orice simulare |

|

DC sensitivity |

Precizia unui net sau tensiune a unei componente, ca functie a unui punct stabil (bias) |

|

Small-signal DC transfer |

Castig in curent al unui semnal de nivel scazut, rezistenta de intrare si iesire, ca functie de punctul de bias |

Analiza formelor de unda

Dupa incheierea simularii, se afiseaza formele de unda rezultate respectiv, se vizualizeaza comportamentul circuitului putandu-se astfel determina validitatea proiectarii.

Analiza post-simulare - presupune adaugarea de informatie de reprezentat pe diagramele de timp.

Cand se detecteaza: erori de setare si mentinere, de hazard de temporizare, PSpice A/D afiseaza mesaj detaliat, impreuna cu forma de unda corespunzatoare. Permite de asemenea localizarea problemelor in schema.

Utilizarea PSpice A/D impreuna cu alte programe

Pregatirea simularii in Capture

Permite definirea formei semnalelor cu variatie in timp utilizate pentru testarea raspunsului circuitului pe durata simularii. Cu ajutorul editorului de stimuli se pot defini:

stimuli analogici sinusoidali, impuls, lineari, etc;

stimuli digitali, de la semnale de tact pana la tipuri complexe de impulsuri si secvente de bus.

Editarea se face prin click pe axa timpului, in punctele care corespund valorilor de intrare dorite la tranzitii.

Este un extractor de modele care genereaza definitii de modele pe care PSpice A/D le utilizeaza in timpul simularii. Acest editor necesita informatii despre dispozitive, gasite in cataloage.

Fisierele necesare pentru simulare

Pentru ca simularea sa aiba loc, PSpice trebuie sa detina informatii despre:

Fisierele generate in Capture sunt:

Biblioteca de modele

O biblioteca de modele este un fisier care contine definitiile electrice ale uneia sau mai multor componente. Informatiile continute in aceste modele sunt utilizate pentru a determina modul in care componentele vor reactiona la diferiti stimuli.

Aceste definitii iau forma:

Caracteristicile de baza ale unui model digital complet:

comportamentul functional - descries de primitivele la nivel de poarta cele comportamentale care cuprind subcircuitul

comportamentul de I/O - descries de modelul de I/O, subcircuitele de interfata si alimentarile legate de o anumita familie logica si

comportamentul temporal- descries de unul sau mai multe modele de temporizare, primitive de intarziere pin-la-pin sau primitive de control al restrictiilor.

Extensia fisierelor cu modele este LIB.

Daca este necesar, se pot crea propriile modele si biblioteci fie:

Fisierul stimul

Contine definirea semnalelor in timp si se pot genera:

Nu toate definirile de stimuli necesita crearea unui fisier. In unele cazuri, ca de exemplu sursele de tensiuni continue sau alternative, este suficienta folosirea simbolului pe schema si setarea atributelor sale.

Fisiere include

Sunt fisiere definite de utilizator si contin :

Dupa citirea fisierului circuit, netlist, a bibliotecilor de modele si a oricaror altor intrari, PSpice A/D porneste simularea. Pe masura ce aceasta evolueaza, rezultatele se salveaza in doua fisiere: unul de date si unul rezultat PSpice.

Fisierul de date diagrama de timp (Waveform) contine rezultatele simularii afisabile intr-o forma grafica. PSpice A/D il citeste automat si afiseaza forma de variatie in timp care reflecta raspunsul circuitului in punctele marcate (legaturi, pini, componente) pe schema. Se poate seta ca afisarea grafica sa aiba loc in timpul simularii sau, dupa incheierea ei. Dupa ce PSpice A/D a citit fisierul de date si afiseaza setul de rezultate initiale, se mai pot adauga diagrame de timp, analiza datelor putandu-se face post-simulare.

Fisierul rezultat PSpice (output file) este un fisier text ASCII care contine:

Continutul acestui fisier este determinat de:

tipurile de analiza rulate,

Pregatirea pentru simulare

Daca portiunea aceasta de circuit necesita o sursa de curent continuu, atunci trebuie sa includa elementul corespunzator. Pentru specificarea unei astfel de surse, se foloseste unul dintre obiectele:

Tabel 2

|

Pentru sursa de tip: |

Se foloseste: |

|

tensiune |

VDC sau VSRC |

|

curent |

IDC or ISRC |

Pentru interfetele A/D in circuite mixte :

Alimentarea digitala implicita

Fiecare componenta digitala din bibliotecile OrCAD are alimentare implicita definita pentru subcircuitul de interfata AtoD sau DtoA. Aceasta inseamna ca daca se proiecteaza un circuit cu semnale mixte, exista o alimentare digitala implicita de 5V inclusa la fiecare interfata.

Alimentare definita de utilizator

In caz de nevoie, se pot personaliza sursele de alimentare pentru diverse familii logice.

Pentru simularea circuitului este necesar sa se conecteze una sau mai multe surse pentru componente care descriu semnalul de intrare la care circuitul trebuie sa raspunda.

Bibliotecile OrCAD furnizeaza mai multe componente sursa descrise in Tabel 3. Acestea depind de:

a. Stimuli analogici

Includ atat sursele de curent cat si pe cele de tensiune

Tabel 3

|

Intrare de tipul: |

Componenta de tensiune |

|

Pentru analize DC | |

|

DC bias |

VDC sau VSRC |

|

Pentru analize AC | |

|

Marimea si faza AC |

VAC sau VSRC |

|

Pentru analize tranzitorii | |

|

Exponentiala |

VEXP sau VSTIM* |

|

Impuls periodic |

VPULSE sau VSTIM* |

|

Linear |

VPWL sau VSTIM* |

|

piecewise-linear care se repeta la infinit |

VPWL_RE_FOREVER sau VPWL_F_RE_FOREVER** |

Pentru a determina numele componentei pentru o sursa de curent echivalenta in tabelul cu elemente sursa de tensiune se inlocuieste in numele acestora V cu I

VSTIM si ISTIM

Se pot utiliza pentru a defini orice tip de semnal cu variatie in timp. Pentru specificarea semnalului se foloseste Editorul de stimuli.

b. Stimuli digitali

Tabel 4

|

Intrare de tipul |

Componenta |

|

Pentru analize tranzitorii semnal sau bus |

DIGSTIMn* |

|

Semnal ceas |

DIGCLOCK |

|

Semnal de un bit |

STIM1 |

|

bus pe 4 biti |

STIM4 |

|

bus pe 8 biti |

STIM8 |

|

bus pe16 biti |

STIM16 |

|

semnal din fisier sau bus (any width) |

FILESTIMn |

DIGSTIM necesita utilizarea editorului de stimuli pentru definirea semnalului de intrare.

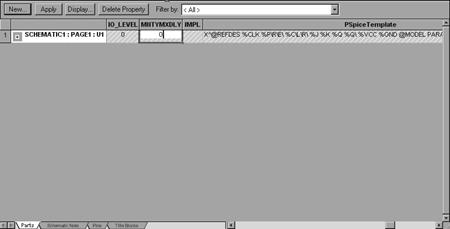

Daca sunt create componente care dorim sa ia parte in simulare, este necesara atasarea implementarii modelului.

Daca au fost definite corect, componentele care sunt utilizabile in simulare trebuie sa aiba proprietatile:

· PSPICETEMPLATE (macheta PSpice) pentru simulare

· PART si REFDES pentru identificare

Se mai pot adauga proprietati specifice simularii pentru componentele digitale: IO_LEVEL, MNTYMXDLY si PSPICEDEFAULTNET (pentru pini).

De exemplu, daca o componenta are comportamentul electric descris de definitia de subcircuit care incepe cu:

|

.SUBCKT 7400 A B Y + optional: DPWR=$G_DPWR DGND=$G_DGND + params: MNTYMXDLY=0 IO_LEVEL=0 |

atunci proprietatile corespunzatoare pentru componenta sunt:

|

IMPLEMENTATION = 7400 MNTYMXDLY = 0 IO_LEVEL = 0 PSPICETEMPLATE = X^@REFDES %A %B %Y %PWR %GND @MODEL PARAMS:IO_LEVEL=@IO_LEVEL MNTYMXDLY=@MNTYMXDLY |

PSPICETEMPLATE

Este o proprietate care defineste sintaxa PSpice A/D pentru lista de conexiuni a componentei. Cand se creaza o lista de conexiuni, Capture substituie valorile actuale din circuit cu cele corespunzatoare din sintaxa PSPICETEMPLATE, apoi salveaza declaratia in fisierul netlist.

Orice componenta care participa la simulare trebuie sa aiba definita proprietatea PSPICETEMPLATE. Aceste reguli se aplica:

Sintaxa

PSPICETEMPLATE contine:

Caracterele uzuale:

Un identificator este o colectie de caractere de forma:

caracter alfabetic [orice alt caracter uzual]*.

Numele de proprietati sunt precedate de unul dintre caracterele speciale:

[ @ | ? | ~ | # | & ]<identificator>

Editorul de pagina cu scheme proceseaza proprietatea conform cu caracterul special intalnit inainte de identificator (vezi Tabel 5).

Tabel 5

|

Sintaxa* |

Inlocuita cu: |

|

@<id> |

Valoarea <id>. Eroare daca nu este asignat nici un <id> sau nici o valoare. |

|

&<id> |

Valoare a <id> daca acesta este definit. |

|

?<id>ss |

Textul dintre separatorii ss daca este definit <id> . |

|

?<id>ss ss |

Textul dintre primii separatori ss daca <id> este definit altfel, a doua clauza ss . |

|

~<id>ss |

Textul dintre separatorii ss daca <id> daca identificatorul nu este definit. |

|

~<id> ss ss |

Textul dintre primii separatori ss daca <id> nu este definit altfel, al doilea ss . |

|

#<id>ss |

Textul dintre ss daca <id> este definit dar sterge restul template daca identificatorul nu este definit. |

* s este un caracter de separare

Caracterele separator includ virgula (,), punctul (.), punct-virgula (;), per (/), bara verticala

bars ( | ). Trebuie intotdeauna utilizat acelasi caracter pentru a preciza o pereche de separatori de inchidere-deschidere.

Caracterul ^ . Editorul pagina schema il va inlocui cu calea completa catre dispozitivul caruia i se face lista de conexiuni.

Secventa n este inlocuita cu linie noua (new line). Utilizand n, se poate specifica o lista de conexiuni cu linii multiple dintr-un template cu o singura linie.

Caracterul % serveste la numirea pinilor:

%<nume pin>

In editorul de pagina, clauza %<nume pin> este inlocuita cu numele net conectat la acel pin

Pentru a se evita conflictul de nume in PSpice, editorul de pagina traduce urmatoarele caractere continute in numele de pini:

< devine l (L), > devine g, = devine e si XXX devine XXXnegat

Exemple:

Macheta unei rezistente (R)

Componenta R are:

· doi pini: 1 si 2

· doua proprietati necesare: REFDES si VALUE

Template

R^@REFDES %1 %2 @VALUE

Transpunere:

R_R23 abc def 1k

unde REFDES este R23, VALUE este 1k, si R este legata la net-urile abc si def.

Componente de tip stimul digital cu template cu pini de latime variabila

In cazul unui model de stimul digital (DIGSTIM de exemplu), numele unui pin poate fi precedat de un caracter, ceea ce are semnificatia ca pinul poate fi conectat la o magistrala, latimea fiind setata egala cu cea a magistralei.

Template

U^@REFDES STIM(%#PIN, 0) %*PIN

n+ STIMULUS=@STIMULUS

unde #PIN se refera la o latime variabila.

Transpunere

U_U1 STIM(4,0) 5PIN1 %PIN2 %PIN3 %PIN4

+ STIMULUS=mystim

stimulul este conectat la un bus pe patru biti a[0-3].

IO_LEVEL

Este o proprietate care defineste nivelul modelului subcircuitului de interfata care trebuie folosit pentru o componenta digitala conectata la una analogica.

Pentru a utiliza proprietatea IO_LEVEL, aceasta trebuie adaugata la componenta si sa i se asigneze o valoare conform :

Tabel 6

|

Valoarea de asignat |

Pentru utilizarea subcircuitului de interfata (nivel) |

|

Implicit |

|

|

AtoD1 si DtoA1 |

|

|

AtoD2 si DtoA2 |

|

|

AtoD3 si DtoA3 |

|

|

AtoD4 si DtoA4 |

Aceasta proprietate se foloseste in definitia PSPICETEMPLATE (IO_LEVEL este de asemenea un parametru de subcircuit utilizat in apelul subcircuitelor digitale).

Exemplu:

PSPICETEMPLATE=X^@REFDES %A %B %C %D %PWR

%GND

@MODEL PARAMS:n+

IO_LEVEL=@IO_LEVEL

MNTYMXDLY=@MNTYMXDLY

MNTYMXDLY

MNTYMXDLY este proprietatea care defineste nivelul intarzierii de propagare digitala care trebuie aplicat pentru o componenta de acest tip. Pentru utilizare, trebuie adaugata proprietatea MNTYMXDLY si asignata o valoare conform celor din Tabel 7.

Tabel 7

|

Valoarea de utilizat |

Intarzierea de propagare |

|

implicita |

|

|

minima |

|

|

tipica |

|

|

maxima |

|

|

cazul cel mai defavorabil (min/max) |

Se foloseste in definirea PSPICETEMPLATE (MNTYMXDLY fiind de asemenea un parametru de subcircuit).

Exemplu:

PSPICETEMPLATE=X^@REFDES %A %B %C %D %PWR

%GND

@MODEL PARAMS:n+

IO_LEVEL=@IO_LEVEL

MNTYMXDLY=@MNTYMXDLY

PSPICEDEFAULTNET este proprietate a pinilor si defineste numele legaturii la care este conectat un pin setat invizibil. Fiecarei proprietati PSPICEDEFAULTNET i se asigneaza numele legaturii digitale.

Exemplu: Daca pinii de alimentare (PWR) si masa (GND) ai unei componente digitale se conecteaza la legaturile digitale $G_DPWR si $G_DGND, atunci proprietatile PSPICEDEFAULTNET ai acestor pini vor fi:

PSPICEDEFAULTNET=$G_DPWR

PSPICEDEFAULTNET=$G_DGND

Se foloseste numele pinului invizibil corespunzator in definirea PSPICETEMPLATE Exemplu: Daca numele pinului de alimentare este PWR si al celui de masa GND, atunci modelul trebuie sa arate astfel:

PSPICETEMPLATE=X^@REFDES %A %B %C %D %PWR

%GND

@MODEL PARAMS:n+

IO_LEVEL=@IO_LEVEL

MNTYMXDLY=@MNTYMXDLY

Crearea si editarea modelelor

Daca in fereastra rezultat a PSpice apare mesajul :

![]()

Inseamna ca: fie a fost plasata o componenta care nu este disponibila pentru simulare, fie o componenta editata dar careia ii lipseste descrierea completa pentru simulare. In aceasta situatie, componenta trebuie inlocuita cu una echivalenta dintr-una din bibliotecile din Tabel 8. si Tabel 9. Pentru a avea siguranta ca respectiva componenta poate fi utilizata in simulare, trebuie verificat daca are o proprietate PSPICETEMPLATE si ca are (tip de implementare) Implementation Type = PSpice MODEL.

Tabel 8

|

Bibliotecile analogice cu componente modelate (instalate in CaptureLibraryPSpice) |

||

|

1_SHOT |

EPWRBJT |

MOTOR_RF |

|

ABM |

FILTSUB |

NAT_SEMI |

|

ADV_LIN |

FWBELL |

OPAMP |

|

AMP |

HARRIS |

OPTO |

|

ANALOG |

IGBT* |

PHIL_BJT |

|

ANA_SWIT |

JBIPOLAR |

PHIL_FET |

|

ANLG_DEV |

JDIODE |

PHIL_RF |

|

ANL_MISC |

JFET |

POLYFET |

|

APEX |

JJFET |

PWRBJT |

|

BIPOLAR |

JOPAMP |

PWRMOS |

|

BREAKOUT |

JPWRBJT |

SIEMENS |

|

BUFFER |

JPWRMOS |

SWIT_RAV |

|

BURR_BRN |

LIN_TECH |

SWIT_REG |

|

CD4000 |

MAGNETIC* |

TEX_INST |

|

COMLINR |

MAXIM |

THYRISTR* |

|

DIODE |

MIX_MISC** |

TLINE* |

|

EBIPOLAR |

MOTORAMP |

XTAL |

|

EDIODE |

MOTORMOS |

ZETEX |

|

ELANTEC |

MOTORSEN | |

Tabel 9

|

Bibliotecile digitale cu componente modelate |

||

|

74AC |

74ACT |

|

|

74ALS |

74AS |

74F |

|

74H |

74HC |

74HCT |

|

74L |

74LS |

74S |

|

DIG_ECL |

DIG_GAL |

DIG_MISC |

|

DIG_PAL |

DIG_PRIM | |

Tinand cont de faptul ca in Capture exista posibilitatea de editare a unor componente care nu se regasesc in biblioteci, in cazul in care se doreste includerea acestora in simulare, trebuie sa li se editeze modele de functionare.

Modelele definesc comportamentul electric al unei componente. Pe o pagina cu schema, aceasta corespondenta este definita de o proprietate a componentei si anume: Implementation. Aceasta este asignata numelui modelului (.).

In functie de tipul de dispozitiv pe care il descrie, modelul este definit de:

Un set de parametri;

Lista de conexiuni subcircuit.

Ambele moduri descriu modelul sub forma de text, cu respectarea unor reguli specifice de sintaxa.

PSpice A/D dispune de algoritmi inclusi (modele) care descriu comportamentul multor tipuri de dispozitive; descriere realizata de un set de parametri model. Comportamentul unui dispozitiv descris de un model inclus, se poate defini prin atribuirea de noi valori tuturor, sau unora dintre parametrii model.

Exemplu:

|

.MODEL MLOAD NMOS |

|

+ (LEVEL=1 VTO=0.7 CJ=0.02pF) |

Pentru dispozitivele care nu dispun de modele incluse, modelele se definesc utilizand sintaxa subcircuit: .SUBCKT/ .ENDS. Aceasta sintaxa include: liste de conexiuni care descriu structura si functiile unei componente si parametrii de intrare ai variabilei pentru reglarea modelului.

Exemplu:

|

* FIRST ORDER RC STAGE |

|

.SUBCKT LIN/STG IN OUT AGND |

|

+ PARAMS: C1VAL=1 C2VAL=1 R1VAL=1 R2VAL=1 |

|

+ GAIN=10000 |

|

C1 IN N1 |

|

C2 N1 OUT |

|

R1 IN N1 |

|

R2 N1 OUT |

|

EAMP1 OUT AGND VALUE= |

|

.ENDS |

Modelele sunt salvate in fisiere numite biblioteci de modele. In functie de configuratie, bibliotecile sunt disponibile fie unui anumit proiect, fie tuturor (global).

Bibliotecile de modele sunt fisiere text care contin una sau mai multe definitii de model. Extensia tipica este .LIB.

Configurarea bibliotecilor de modele

PSpice A/D cauta bibliotecile dupa numele de modele specificate in implementarea modelelor pentru componentele din schema.

Bibliotecile trebuie configurate pentru ca PSpice A/D sa stie unde sa caute definitiile modelelor:

Figura 1

Figura 1

Modele locale - acestea sunt utilizate intr-un singur proiect. Editorul de scheme creeaza automat un model de acest tip, de fiecare data cand este modificata definitia modelului pentru o anumita componenta de pe schema. Modelele se pot genera si extern urmand sa fie realizata o configurare manuala pentru o anumita plansa.

Modelele globale - sunt disponibile tuturor planselor create.

Bibliotecile de modele instalate odata cu programele OrCAD se pot regasi in NOM.LIB. Acest fisier demonstreaza felul in care se pot inlantui referirile catre alte biblioteci si modele. NOM.LIB contine definitii de model globale.

Bibliotecile standard contin o mare varietate de componente digitale produse intr-o gama variata de tehnologii. Aceste componente sunt descrise din punct de vedere electric cu ajutorul unui model, in forma unei definitii de subcircuit, pastrata in biblioteca de modele. Numele de subcircuit corespunzator este definita in valoarea atributului MODEL a componentei. Alte atribute cum ar fi: MNTYMXDLY, IO_LEVEL si setul PSPICEDEFAULTNET apartin subcircuitului, oferind astfel posibilitati de influentare a comportamentului modelului dispozitivului digital.

In general, componentele digitale continute in biblioteci sunt suficiente pentru cele mai multe tipuri de proiecte. Cu toate acestea, se pot ivi situatii in care este necesara utilizarea unei componente care nu se regaseste nici in bibliotecile standard, nici in cele de modele. In aceasta situatie, se impune crearea de modele corespunzatoare noilor componente introduse.

Un model complet, are urmatoarele caracteristici(Figura 2):

Comportamentul functional descris de primitive la nivel de poarta si de comportament digital;

Comportamentul de I/O descris de modelul corespunzator, subcircuite de interfata si alimentari specifice unei familii logice si

Comportamentul in timp descris de unul sau mai multe modele, primitive de intarzieri pin-la-pin sau, primitive de verificare a restrictiilor.

Comportamentul functional

Modelul de comportament functional al unei componente digitale este descris prin intermediul uneia sau mai multor primitive logice, interconectate. O parte a acestor primitive digitale sunt exemplificate in Tabelul 10 (Anexa 1 cuprinde toate primitivele logice).

Tabel 10

|

Formatul primitivelor digitale este similar cu cel al primitivelor analogice. Diferenta consta in aceea ca cele mai multe primitive logice necesita doua modele si nu unul:

Motivul pentru care a fost nevoie de introducerea celor doua tipuri de modele este acela ca daca informatia de temporizare este specifica fiecarui tip de componenta, cea de intrare/iesire este caracteristica unei intregi familii logice .

Sintaxa primitivelor logice

Formatul general:

U<nume> < tip primitiva > [( < valoare parametru >* )]

+ < nod alimentare digitala > < nod masa digitala >

+ <nod>*

+ <Nume model temporizare> < Nume model I/O >

+ [MNTYMXDLY=< valoare selectie intarziere >]

+ [IO_LEVEL=< valoar eselectie interfata subckt >]

unde:

<primitive type>

[( <parameter value>* )] - este tipul dispozitivului digital, cum

ar fi:

<digital power node> <digital ground node> - sunt nodurile folosite de subcircuitele de interfata care conecteaza nodurile analogice cu cele digitale sau invers.

<node>* unul sau mai multe noduri de intrare si iesire. Numarul de noduri depinde de tipul de primitiva parametrii acesteia. Dispozitivele analogice, cele digitale sau ambele, pot fi conectate la un nod. Daca un nod are legaturi atat analogice cat si logice, atunci PSpice A/D insereaza automat un subcircuit de interfata pentru a face translatarea intre starile logice de iesire si tensiuni.

<Timing model name> - este numele modelului de temporizare care descrie caracteristicile de temporizare ale dispozitivului cum ar fi: intarzieri de propagare si timpi de setare si mentinere. Fiecare parametru de acest tip o valoare minima, tipica si maxima care poate fi selectata pe timpul simularii.

<I/O model name> - este numele unui model de I/O care descrie caracteristicile de incarcare si dirijare. Modelele de I/O contin de asemenea numele a pana la patru subcircuite de interfata DtoA si AtoD, numite automat de PSpice A/D sa manevreze nodurile de interfata analog/digitale.

MNTYMXDLY[2] - este un parametru optional care selecteaza valorile minime, maxime sau tipice ale intarzierilor din modelul de temporizare al componentei respective. Valoarea implicita este 0. Valorile acceptate sunt:

0 = valoarea curenta a optiunii DIGMNTYMX[3] (implicit=2)

1 = minima

2 = tipica

3 = maxima

4 = cazul cel mai defavorabil (worst-case timing - min-max)

IO_LEVEL - este un parametru optional care selecteaza unul dintre subcircuitele de interfata AtoD sau DtoA din modelul de I/O. PSpice A/D apeleaza subcircuitul selectat automat in situatia in care un nod care conecteaza o primitiva conecteaza si un dispozitiv analogic. Valoarea implicita este 0. Valori admise:

0 = valoarea curenta a optiunii DIGIOLVL[4] (implicit=1)

1 = AtoD1/DtoA1

2 = AtoD2/DtoA2

3 = AtoD3/DtoA3

4 = AtoD4/DtoA4

Cand se adauga componente digitale in biblioteci, trebuie create modele corespunzatoare prin legarea dispozitivelor U in definitii de subcircuite, similare celor din exemplul de mai jos

Este recomandabila crearea unei biblioteci de modele utilizator, configurabila pentru folosirea in anumite proiecte.

* 74HC533 Octal D-TYPE Transparent Latches with 3-STATE Outputs

* The High-Speed CMOS Logic Data Book, 1988, TI

* atl 9/18/89 Update interface and model names

* rbh 11/11/92 Added bus I/O model

..subckt 74HC533 OCBAR C 1D 2D 3D 4D 5D 6D 7D 8D 1QBAR 2QBAR 3QBAR 4QBAR 5QBAR

6QBAR 7QBAR 8QBAR

optional: DPWR=$G_DPWR DGND=$G_DGND

params: MNTYMXDLY=0 IO_LEVEL=0

UOC inv DPWR DGND

OCBAR OC

D0_GATE IO_HC IO_LEVEL=

UQI dltch(8) DPWR DGND

$D_HI $D_HI C

1D 2D 3D 4D 5D 6D 7D 8D

$D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC $D_NC

1QI 2QI 3QI 4QI 5QI 6QI 7QI 8QI

D_HC533_1 IO_HC MNTYMXDLY= IO_LEVEL=

UQBAR buf3a(8) DPWR DGND

1QI 2QI 3QI 4QI 5QI 6QI 7QI 8QI

OC

1QBAR 2QBAR 3QBAR 4QBAR 5QBAR 6QBAR 7QBAR 8QBAR

D_HC533_2 IO_HC_BUS MNTYMXDLY= IO_LEVEL=

.ends

Caracteristici de temporizare

Cele mai multe primitive au asociat un model de temporizare in care sunt specificate intarzierile de propagare si restrictiile de timp. Aceasta metoda este utilizata cand este mai usoara partitionarea intarzierilor intre primitivele individuale, in special atunci cand numarul primitivelor este mic

Se utilizeaza primitivele PINDLY si CONSTRAINT care pot modela direct intarzierile pin-la-pin si restrictiile de timp pentru intregul model de dispozitiv. Cu aceasta metoda, toate celelalte primitive functioneaza cu intarziere nula.

In plus fata de intarzierile de propagare explicite, mai exista factori care pot afecta timpul de propagare total prin dispozitiv.

Modelul de temporizare

Figura 3

Cu exceptia dispozitivelor PULLUP, PULLDOWN si PINDLY, toate primitivele digitale au un model de temporizare care furnizeaza simulatorului parametrii de temporizare. Acest model este unic pentru fiecare primitiva (respectiv numele modelului si parametrii care pot fi definiti pentru el difera de la primitiva la primitiva).

Tipurile de parametri:

Intarzieri de propagare (Propagation delays - TP)

Timpi de setare (Setup times - TSU)

Timpi de mentinere (Hold times - TH)

Durata impulsului (Pulse widths - TW)

Timpi de comutare (Switching times - TSW)

Fiecare parametru este in continuare divizat in trei valori: minime (MN), tipica (TYP) si maxime (MX). De exemplu, valoarea tipica a intarzierii de propagare de la nivel coborat la unul ridicat (low to high) pe o poarta, este specificata cu parametrul TPLHTY. Sunt utilizate mai multe tipuri de modele de temporizare. In Figura 25. este prezentat modelul de temporizare (D_HC533_1) al circuitului 74HC533.

Cand se creeaza propriul model, este util, sa fie salvat intr-o biblioteca utilizator care poate fi configurata pentru a fi folosita pentru un anumit proiect. Sunt parametri care pot lipsi din model deoarece cataloagele nu ofera intotdeauna specificatiile pentru toate cele trei tipuri de valori: minime, tipice si maxime. Modul in care simulatorul trateaza parametrii lipsa depinde de tipul acestora.

Tratarea intarzierilor de propagare nespecificate

Deseori, in cataloagele de componente, sunt precizate doar valorile tipice si maxime ale intarzierilor. Daca, in acest caz, simulatorul atribuie valoarea zero minimului, se pot produce disfunctionalitati in anumite situatii.

Din acest motiv, exista doua optiuni configurabile: DIGMNTYSCALE si DIGTYMXSCALE,, utilizate pentru a extrapola intarzierile de propagare nespecificate.

DIGMNTYSCALE - aceasta optiune calculeaza intarzierea minima cand se cunoaste cea tipica, conform formulei:

TPxxMN = DIGMNTYSCALE × TPxxTY

Valoarea implicita a DIGMNTYSCALE este 0.4 sau 40% din intarzierea tipica. Valoarea sa trebuie sa se situeze intre 0.0 si 1.0.

DIGTYMXSCALE - este o optiune care calculeaza intarzierea maxima pe baza celei tipice cu formula:

TPxxMX = DIGTYMXSCALE × TPxxTY

DIGTYMXSCALE are valoarea implicita 1.6. Valoarea sa trebuie sa fie mai mare decat 1.

Cand nu este specificata o intarziere tipica, valoarea sa se deduce din intarzierile minime sau maxime. Daca se cunoaste atat maximul cat si minimul, valoarea tipica va fi media aritmetica a celorlalte doua. Daca se cunoaste doar intarzierea minima, valoarea tipica se obtine utilizand optiunea DIGMNTYSCALE. Similar, daca se cunoaste valoarea maxima DIGTYMXSCALE. Evident, daca nu se precizeaza nici una dintre cele trei valori, se va folosi valoarea zero pentru toate.

Tratarea restrictiilor de timp nespecificate

Celelalte restrictii de temporizare sunt tratate diferit fata de cele de intarziere. In cataloage, se regasesc deseori valorile minime pentru durata impulsului, timp de setare si de mentinere.

In situatia in care lipsesc una sau mai multe restrictii, simulatorul parcurge urmatoarele etape pentru a le completa:

Daca valoarea minima este omisa, este folosita o valoare implicita: zero.

Daca este omisa valoarea maxima, se ia valoarea tipica, daca aceasta exista; in caz contrar, se ia valoarea minima.

Daca este omisa valoarea tipica, se ia media aritmetica a valorii minime si maxime.

Calculul intarzierii de propagare

Caracteristicile de temporizare ale primitivelor digitale sunt determinate atat de modelele de temporizare si de cele de I/O. Modelele de temporizare precizeaza intarzierile de propagare si restrictiile de temporizare. Modelele de I/O precizeaza incarcarea de intrare si iesire, rezistentele de cuplare si timpii de comutare.

Cand iesirea unui dispozitiv se leaga la un alt dispozitiv digital, intarzierea totala de propagare peste un dispozitiv este determinata adunand intarzierea de incarcare (pe terminalul de iesire), cu intarzierea specificata in modelul de temporizare. Intarzierea de incarcare se calculeaza din incarcarea totala pe iesire si rezistentele de comanda. Intarzierea totala pe o iesire este calculata insumand incarcarile de intrare si de iesire (OUTLD si INLD din modelul de I/O) ale tuturor dispozitivelor comandate de acea iesire. Aceasta incarcare totala combinata cu rezistentele de comutare ale dispozitivului (DRVL si DRVH din modelul de I/O), permit calculul intarzierii de incarcare: Intarzierea de incarcare = RDRIVE·CTOTAL·ln(2)

Aceasta intarziere se calculeaza pentru fiecare terminal de iesire al fiecarui dispozitiv inainte de inceperea simularii. Intarzierea totala de propagare este calculata cu usurinta in timpul simularii adaugand intarzierile de incarcare pre-calculate la intarzierea de temporizare a diapozitivului. Nu se folosesc specificatiile de timp cu valoarea zero.

Cand iesirile se leaga la dispozitive analogice, intarzierea de propagare este redusa de timpii de comutare precizati in modelul de I/O.

Intarzierea inertiala si de transport

Simulatorul utilizeaza doua tipuri diferite de functii de intarziere interna cand simuleaza portiunea digitala a circuitului: intarzierea inertiala si cea de transport. Aplicarea acestor concepte se face intern primitivelor digitale, motiv pentru care nu pot fi selectabile de catre utilizator.

Intarzierea inertiala

Simularea unui dispozitiv poate fi descrisa ca aplicarea unor stimuli (S) unei functii (F) si preconizarea raspunsului (R).

Daca dispozitivul este electric prin natura sa, aplicarea stimulului implica energie care determina schimbarea de stare a acestuia. Cantitatea de energie este functie de amplitudinea semnalului si durata acestuia. Daca stimulul se aplica pe o durata prea mica, dispozitivul nu va comuta. Durata minima necesara pentru ca o modificare la intrare sa provoace o schimbare de stare a acesteia, se numeste intarziere inertiala. Pentru simularea digitala, toti parametrii de intarziere din modelul de temporizare sunt considerati inertiali cu exceptia primitivei linie de intarziere (DLYLINE).

Pentru a modela corect comportamentul de imunitate la zgomot, se poate seta in modelul de I/O parametrul TPWRT (pulse width rejection threshold). Cand durata impulsului este mai mare decat TPWRT, si mai mica decat intarzierea de propagare, dispozitivul genereaza un impuls: 0-R-0, 1-F-1, sau un impuls X.

Intarzierea de transport

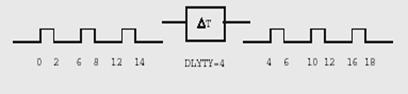

Primitiva linie de intarziere este unicul model de simulare

care poate propaga impulsuri de orice durata aplicate la intrarea sa.

Functia acesteia este de a deplasa impulsul aplicat la intrare su o

valoare de timp

Figura 26

Modelul de I/O

Modelele de I/O sunt comune unei familii logice intregi. De exemplu, in bibliotecile de modele exista doar patru modele de I/O pentru intreaga familie 74LS. IO_LS, pentru intrari sau iesiri standard; IO_LS_OC, pentru intrari standard si iesiri cu colector in gol (open-collector); IO_LS_ST, pentru intrari trigger Schmitt si iesiri standard; IO_LS_OC_ST, pentru intrari trigger Schmitt si iesiri cu colector in gol. In schimb, modelele de temporizare sunt unice pentru fiecare dispozitiv.

Modelele de I/O sunt specificate:

.MODEL <I/O nume model > UIO [parametri model]*

Valorile admise ale acestor parametri rezulta din Tabel 11:

Tabel 11

|

Parametru |

Descriere |

|

INLD |

Capacitatea de incarcare la intrare |

|

OUTLD |

Capacitatea de incarcare la iesire |

|

DRVH |

Rezistenta iesirii la nivel inalt |

|

DRVL |

Rezistenta iesirii la nivel coborat |

|

DRVZ |

Rezistenta de pierdere la iesire in starea Z |

|

INR |

Rezistenta de pierdere la intrare |

|

TSTOREMN |

Durata de stocare minima pentru net-ul simulat ca sarcina |

|

TPWRT |

Pragul de rejectie a duratei impulsului |

|

AtoD1 (Level 1) |

Numele subcircuitului de interfata AtoD |

|

DtoA1 (Level 1) |

Numele subcircuitului de interfata DtoA |

|

AtoD2 (Level 2) |

Numele subcircuitului de interfata AtoD |

|

DtoA2 (Level 2) |

Numele subcircuitului de interfata DtoA |

|

AtoD3 (Level 3) |

Numele subcircuitului de interfata AtoD |

|

DtoA3 (Level 3) |

Numele subcircuitului de interfata DtoA |

|

AtoD4 (Level 4) |

Numele subcircuitului de interfata AtoD |

|

DtoA4 (Level 4) |

Numele subcircuitului de interfata DtoA |

|

DIGPOWER |

Numele subcircuitului de alimentare |

|

TSWLH1 |

Durata de comutare de la coborat la inalt pentru DtoA1 |

|

TSWLH2 |

Durata de comutare de la coborat la inalt pentru DtoA2 |

|

TSWLH3 |

Durata de comutare de la coborat la inalt pentru DtoA3 |

|

TSWLH4 |

Durata de comutare de la coborat la inalt pentru DtoA4 |

|

TSWHL1 |

Durata de comutare de la inalt la coborat pentru DtoA1 |

|

TSWHL2 |

Durata de comutare de la inalt la coborat pentru DtoA2 |

|

TSWHL3 |

Durata de comutare de la inalt la coborat pentru DtoA3 |

|

TSWHL4 |

Durata de comutare de la inalt la coborat pentru DtoA4 |

Primitivele logice cuprinse in circuitul 74HC533 (biblioteca Dig_IO.lib):

.model IO_HC uio (

+ drvh=87 drvl=87

+ inld=3.5pF

+ AtoD1='AtoD_HC' AtoD2='AtoD_HC_NX'

+ AtoD3='AtoD_HC' AtoD4='AtoD_HC_NX'

+ DtoA1='DtoA_HC' DtoA2='DtoA_HC'

+ DtoA3='DtoA_HC_E' DtoA4='DtoA_HC_E'

tswhl1=2.742ns tswlh1=2.758ns

tswhl2=2.742ns tswlh2=2.758ns

tswhl3=2.751ns tswlh3=2.763ns

tswhl4=2.751ns tswlh4=2.763ns

+ DIGPOWER='DIGIFPWR' tpwrt=2ns

+ )

Definirea puterilor de iesire

Simulatorul este rulat pentru a putea calcula valori in fiecare nod dintr-un circuit. In cazul nodurilor analogice, valorile sunt tensiuni. Pentru nodurile digitale aceste valori sunt stari. Starea se calculeaza din puterile de iesire ale dispozitivelor care comanda nodul si de nivelul logic al acestuia.

Scopul acestor puteri este acela de a permite simulatorului sa gaseasca valoarea unui nod atunci cand este comandat de mai multe iesiri. Un exemplu simplu este acela al unei linii de bus care este comandata de mai mult decat un tri-state. In conditii normale, toate driver-ele, mai putin unul, comanda trecerea in stare de impedanta ridicata (Z). Linia va lua deci valoarea portii care o comanda cu o putere mai mare (impedanta mai mica).

Crearea subcircuitelor de interfata

In cazul in care componenta digitala nu exista in bibliotecile de modele, se poate intampla sa fie nevoie de crearea subcircuitelor de interfata. Daca obiectele nou create apartin unei familii logice existente, atunci trebuie facuta referire la modelele de I/O deja existente. Formatele pentru AtoD si DtoA sunt:

.SUBCKT ATOD <name suffix>

+ <analog input node>

+ <digital output node>

+ <digital power supply node>

+ <digital ground node>

+ PARAMS: CAPACITANCE=<input load value>

.ENDS

si:

.SUBCKT DTOA <name suffix>

+ <digital input node> <analog output node>

+ <digital power supply node> <digital

+ ground node>

+ PARAMS: DRVL=<0 level driving resistance>

+ DRVH=<1 level driving resistance>

+ CAPACITANCE=<output load value>

.ENDS

Spre deosebire de cele mai multe tipuri de dispozitive analogice, cea mai mare parte a dispozitivelor digitale nu sunt primitive compilate in simulator. Cele mai multe modele digitale sunt macromodele sau subcircuite care sunt construite din cele cateva primitive existente.

Aceste subcircuite fac referiri la modelele de interfata si de temporizare pentru a trata interfetele AtoD si DtoA si totalitatea parametrilor de temporizare ai dispozitivelor fizice. Pentru cele mai multe familii de circuite logice, modelele de interfata sunt definite si se gasesc in Dig_IO.lib .

In simulator, aceste primitive sunt dispozitive sau functii compilate direct in cod. Primitivele servesc ca blocuri constructive de baza pentru macromodele mai complexe.

Primitivele din simulator sunt de doua tipuri: la nivel de poarta si comportamentale. O primitiva la nivel de poarta se refera in mod normal la o componenta fizica (buffere, porti SI, inversoare, etc.). O primitiva comportamentala ajuta in definirea parametrilor unui model de nivel mai inalt. Ambele tipuri de primitive sunt intrinseci simulatorului.

In exemplul referitor la circuitul 74160, cele patru bistabile de tip J-K sunt patru primitive la nivel de poarta. Cu toate ca bistabilele sunt mai complexe fizic decat portile din punctul de vedere al modelarii, sunt definite la acelasi nivel cu acestea. Dat fiind faptul ca toate patru au RESET, Clear si Clock comune, pot fi combinate intr-o retea de bistabile

Primitiva LOGICEXP

Urmarind modelul 74160, putem observa ca exista trei parti principale ale subcircuitului: .SUBCKT care contine lista pinilor de interfata si lista parametrilor, LOGICEXP care contine tot ceea ce poate fi exprimat prin logica simpla combinationala. Dispozitivele expresii logice servesc de asemenea la bufferarea altor semnale de intrare care vor merge la primitiva PINDLY. In acest caz, LOGICEXP buffereaza CLK_I, ENP_I, ENT_I, CLRBAR_I, LOADBAR_I si patru semnale de date.

Pentru 74160 LOGICEXP are 14 intrari si 20 iesiri. Intrarile constau din noua pini de interfata de intrare in subcuircuit plus cinci semnale de feedback care vin de la bistabilii: QA, QB, QC, QD si QDBAR (iesirea QD negata). Bistabilii sunt primitive si nu fac parte din expresia logica. Iesirile sunt: cele opt intrari de date J-K ale bistabililor, RCO, cele patru linii de date, utilizate intern expresiei logice (A, B, C, D) si sapte linii de control CLK, CLKBAR, EN, ENT, ENP, CLRBAR, si LOADBAR. (BAR are semnificatia de negat).

In model se folosesc D0_GATE care este modelul de temporizare al unei primitive de tip poarta, cu intarziere zero.

IO_STD este modelul standard de I/O. Determina caracteristicile de interfata AtoD si DtoA. D0_EFF este un model de temporizare cu intarziere zero, specific bistabililor. (biblioteca Dig_IO.lib)

Primitiva PINDLY (intarziere pin-la-pin )

Specificatiile de intarziere si restrictiile ale modelului se realizeaza cu primitiva PINDLY. Aceasta este evaluata de cate ori intrarile sau iesirile sale se modifica.

Primitiva PINDLY permite de asemenea verificarea restrictiilor modelului. Verifica timpii de setare, de mentinere, durata impulsului si frecventa. Mai dispune de un mecanism care permite raportarea conditiilor definite de utilizator. Avand in vedere ca parametrii de temporizare sunt specificati in general la nivel de pin, verificarea se face in mod normal la pinii de interfata ai circuitului dupa ce s-a facut bufferarea adecvata.

BOOLEAN

Cuvantul cheie BOOLEAN incepe asignarile booleene care definesc variabilele temporare care pot fi folosite ulterior in primitiva PINDLY. Formatul este:

Variabila booleeana =

Parantezele acolada sunt necesare. Operatorii booleeni, dupa precedenta de sus in jos, sunt:

Operatorii booleeni iau ca operanzi, urmatoarele valori:

Functii referinta

Functii de tranzitie

Variabile booleene asignate anterior

Constantele booleene TRUE si FALSE.

Functiile de tranzitie (primitive comportamentale) au forma generala: TRN_pn, unde p este variabila de stare anterioara si n este variabila de stare curenta. Valorile starilor sunt luate din setul: . $ are semnificatia de stare indiferenta. Setul complet de functii de tranzitie este: TRN_LH TRN_LZ TRN_L$ TRN_HL TRN_HZ TRN_H$ TRN_ZL TRN_ZH TRN_Z$ TRN_$L TRN_$H si TRN_$Z. Functiile TRN_pZ si TRN_Zn iau valoarea TRUE doar daca sunt utilizate in TRISTATE.

PINDLY

Contine intarzierile actuale si expresiile restrictiilor pentru fiecare dintre iesiri. Functia CASE defineste o expresie a intarzierilor mai complexa, bazata pe reguli si lucreaza. Fiecare expresie din functia CASE este evaluata in ordine, pana se ajunge la una al carei rezultat este adevarat. In acest punct, portiunea de expresie a intarzierii din regula este asociata cu nodul de iesire care este in evaluare, restul functiei CASE fiind ignorat. Daca nici o expresie nu este adevarata, se foloseste intarzierea implicita, motiv pentru care trebuie introdusa o valoare implicita in fiecare functie CASE. Expresiile trebuie separate prin virgula. Formatul CASE:

CASE(

<boolean expression>, <delay expression>,; Rule 1

<boolean expression>, <delay expression>,; Rule 2

<delay expression> ; Default delay

CONSTRAINT (primitiva)

Furnizeaza un mecanism de verificare a restrictiilor. Verifica timpii de setare si mentinere, verifica frecventa si include mecanisme de introducere a conditiilor definite de utilizator. Verificari:

Setup_Hold - expresia din aceasta specificatie trebuie poate fi afisata in orice ordine.

CLOCK defineste nodul care trebuie utilizat ca referinta pentru setup/hold/release (setare/mentinere/refacere). Trecerea se face din LH sau HL ( stare logica 0 in 1 sau din 1 in 0).

DATA precizeaza care este nodul (nodurile) al carui timp de setare/mentinere se masoara.

SETUPTIME defineste durata minima cat nodurile de date trebuie sa fie stabile inainte frontul activ al clockului.

HOLDTIME este folosit in acelasi mod ca si SETUPTIME si dispune si de variantele de format _LH si _HL si conditia de valoare 0.

RELEASETIME determina simulatorul sa execute o verificare de setup special. Este o durata care se refera timpul minim in care un semnal poate deveni inactiv inainte de frontul activ al clockului.

WIDTH este durata minima de impuls la verificare. MIN_HI si MIN_LO sunt timpii minimi cat nodul poate ramane in starea HIGH sau LOW. O valoare 0 inseamna ca este permisa orice durata de impuls.

FREQ verifica frecventa. MINFREQ / MAXFREQ este valoarea minima respectiv maxima de frecventa permisa pe nodul in chestiune.

* 74160 Synchronous 4-bit Decade Counters with

asynchronous clear

* Modeled using LOGICEXP, PINDLY, & CONSTRAINT devices

.SUBCKT 74160 CLK_I ENP_I ENT_I CLRBAR_I LOADBAR_I A_I B_I

C_I D_I

+ QA_O QB_O QC_O QD_O RCO_O

+ OPTIONAL: DPWR=$G_DPWR DGND=$G_DGND

+ PARAMS: MNTYMXDLY=0 IO_LEVEL=0

U160LOG LOGICEXP(14,20) DPWR DGND

+ CLK_I ENP_I ENT_I CLRBAR_I LOADBAR_I A_I B_I C_I D_I

+ QDBAR QA QB QC QD

+ CLK ENP ENT CLRBAR LOADBAR A B C D

+ CLKBAR RCO JA JB JC JD KA KB KC KD EN

+ D0_GATE IO_STD IO_LEVEL=

+ LOGIC:

+ CLK = ;Buffering

+ ENP =

+ ENT =

+ CLRBAR =

+ LOADBAR =

+ A =

+ B =

+ C =

+ D =

+ CLKBAR = ;Logic expressions

+ LOAD =

+ EN =

+ I1A =

+ I2A =

+ JA =

+ KA =

+ I1B =

+ I2B =

+ JB =

+ KB =

+ I1C =

+ I2C =

+ JC =

+ KC =

+ I1D =

+ I2D =

+ JD =

+ KD =

+ RCO =

UJKFF JKFF(4) DPWR DGND $D_HI CLRBAR CLKBAR JA JB JC JD KA

KB KC KD

+ QA QB QC QD QABAR QBBAR QCBAR QDBAR D0_EFF IO_STD

U160DLY PINDLY (5,0,10) DPWR DGND

+ RCO QA QB QC QD

+ CLK LOADBAR ENT CLRBAR ENP A B C D EN

+ RCO_O QA_O QB_O QC_O QD_O

+ IO_STD MNTYMXDLY= IO_LEVEL=

+ BOOLEAN:

+ CLOCK =

+ CNTENT =

+ PINDLY:

+ QA_O QB_O QC_O QD_O =

+ RCO_O =

+ FREQ:

+ NODE = CLK

+ MAXFREQ = 25MEG

+ WIDTH:

+ NODE = CLK

+ MIN_LO = 25NS

+ MIN_HI = 25NS

+ WIDTH:

+ NODE = CLRBAR

+ MIN_LO = 20NS

+ SETUP_HOLD:

+ DATA(4) = A B C D

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ WHEN =

+ SETUP_HOLD:

+ DATA(2) = ENP ENT

+ CLOCK LH = CLK

+ SETUPTIME = 20NS

+ WHEN =

+ SETUP_HOLD:

+ DATA(1) = LOADBAR

+ CLOCK LH = CLK

+ SETUPTIME = 25NS

+ WHEN =

+ SETUP_HOLD:

+ DATA(1) = CLRBAR

+ CLOCK LH = CLK

+ RELEASETIME_LH = 20NS

.ENDS

Simularea logica

Reprezinta analiza comportamentului logic si temporal al componentelor digitale. Pspice A/D simuleaza acest comportament pe durata analizei tranzitorii. Cand calculeaza punctul de stabilitate, considera dispozitivele logice impreuna cu oricare dispozitiv analogic din circuit.

PSpice A/D realizeaza o analiza de temporizare detaliata, tinand cont de restrictiile precizate pentru componente. Raporteaza orice incalcari de temporizare sau hazard sub forma unor mesaje in fisierele rezultat.

Etape in simularea logica:

Desenarea schemei

Definirea stimulilor

Starea duratei simularii

Ajustarea parametrilor de simulare

Lansarea simularii

Analiza rezultatelor

Concepte utilizate:

Stari

Cand circuitul este operational, nodurile logice (vezi simularea mixta analog/digitala) pot sa ia valori sau stari de iesire, conform cu tabelul de mai jos:

Tabel 12

|

Stare |

Semnificatie |

|

Low, fals, negat, deconectat (off) Low - coborat |

|

|

High, adevarat, direct, activ(on) High - ridicat |

|

|

R |

Crescator (se schimba din 0 in 1, undeva in intervalul R) |

|

F |

Cazator ( trece din 1 in 0, undeva in intervalul R ) |

|

X |

Indiferenta : poate fi high, low, intermediara sau instabila |

|

Z |

Impedanta ridicata: poate fi high, low, intermediara sau instabila |

Starile nu corespund neaparat unui nivel de tensiune specific sau chiar stabil. Un nivel logic 1, inseamna doar aceea ca, tensiunea este undeva in intervalul de nivel ridicat din domeniul familiei respective de circuite. Nivelurile crescatoare sau cele cazatoare indica doar ca tensiunea traverseaza pragul 0 - 1 la un anumit moment din intervalul F sau R si nu aceea ca modificarea tensiunii ar urma o anumita panta.

Puteri (Strengths)

Cand un nod logic este comandat de mai mult decat un dispozitiv, PSpice A/D determina nivelul corect al nodului. Fiecare iesire are o valoare de putere (tarie), pe care PSpice o compara cu cele ale iesirilor care comanda nodul. Cel mai puternic, determina nivelul rezultatului la nod. Daca iesirile de aceleasi puteri, dar nivele diferite, comanda un nod, nivelul acestuia va deveni X.

PSpice A/D recunoaste 64 de puteri (strengths). Cea mai slaba este numita Z. Cea mai puternica este numita cea de fortare (forcing strengths). Z -numita impedanta ridicata, este iesirea specifica portilor tristate inactive, sau iesirile dispozitivelor cu colector in gol.

Definirea unui stimul logic

Stimulul defineste intrarea portiunilor logice din circuit, avand un rol similar cu al surselor independente de tensiune sau curent, pentru portiunile analogice ale circuitului. In tabelul urmator sunt cuprinsi stimulii digitali existenti in bibliotecile PSpice A/D:

Tabel 13

|

Daca se specifica semnalul de intrare cu: |

Atunci se utilizeaza: |

Pentru tipul de intrare digitala: |

|

Editorul de stimuli |

DIGSTIM |

semnal sau bus |

|

Definirea proprietatilor |

DIGCLOCK |

semnal de tact |

|

STIM1 |

stimul de un bit |

|

|

STIM4 |

stimul pe patru biti |

|

|

STIM8 |

stimul pe 8 biti |

|

|

STIM16 |

16 biti |

|

|

FILESTIM1 |

stimul de un bit, dintr-un fisier |

|

|

FILESTIM2 |

2 biti - // - |

|

|

FILESTIM4 |

idem pentru 4 biti |

|

|

FILESTIM8 |

idem pentru 8 biti |

|

|

FILESTIM16 |

idem pentru 16 biti |

|

|

FILESTIM32 |

idem pentru 32 biti |

Definirea tranzitiilor de tact

Pentru crearea unui stimul de tact, in editorul de stimuli alege stimulul pe care dorim sa-l folosim ca si clock. Din meniul Stimulus, se alege Change Type - si Clock. Se introduc apoi valorile pentru proprietatile semnalului de tact, dupa cum urmeaza:

Tabel 14

|

Proprietate |

Valoare de introdus |

|

Frequency (frecventa) |

rata tactului |

|

Duty Cycle (ciclul de lucru) |

Procent de stari high, fata de low, in unitati zecimale sau intregi |

|

Initial Value (Valoare initiala) |

valoarea de pornire: 0 sau 1 |

|

Time Delay (intarziere) |

durata de timp scursa dupa inceperea simularii, cand semnalul de ceas are efect |

Exemplu:

Pentru un semnal de tact cu frecventa de 20MHz, ciclul de lucru 50%, valoarea de pornire 1 si intarzierea de 5ms, proprietatile se seteaza astfel:

|

Frequency |

=20Meg |

|

Duty Cycle |

=0.50 (sau 50) |

|

Initial Value | |

|

Time Delay |

=5ms |

In Capture, pentru definirea semnalului de clock, se editeaza componenta DIGCLOCK dupa cum urmeaza:

Tabel 15

|

Pentru proprietatea: |

Se specifica: |

|

DELAY |

durata pana la prima tranzitie a tactului |

|

ONTIME |

durata starii High, pentru fiecare perioada |

|

OFFTIME |

durata starii Low pentru fiecare perioada |

|

STARTVAL |

valoarea Low a ceasului ( implicit : 0) |

|

OPPVAL |

valoarea High a ceasului (implicit: 1) |

Aceste componente au cate un singur pin pentru conexiune. STIM1 este utilizat pentru a comanda o singura legatura. STIM4, STIM8 si STIM16 comanda busuri care au cate 4, 8 si 16 biti.

Tabel 17 Proprietatile componentelor STIMn:

|

Proprietate |

Descriere |

|

WIDTH |

Numar de semnale de iesire (noduri) |

|

FORMAT |

Secventa binara care defineste numarul de semnale corespunzatoare unui numar in oricare termen <value> care apare intr-o proprietate COMMANDn. Fiecare cifra trebuie sa fie 1, 3, sau 4 ( binar, octal si hexazecimal); suma cifrelor din FORMAT trebuie sa fie egala cu valoarea WIDTH |

|

IO_MODEL |

model de I/O care descrie caracteristicile de comanda ale stimulului |

|

IO_LEVEL |

Selectia unui subcircuit de interfata dintr-unul dintre cele patru subcircuite analogice/digitale furnizate cu modelul de I/O al componentei |

|

DIG_PWR |

Pinul de alimentare logica utilizat de subcircuitul de interfata |

|

DIG_GND |

Pinul de masa logica utilizat de subcircuitul de interfata |

|

TIMESTEP |

Numarul de secunde/ ciclu sau pas de tact |

|

COMMAND1-COMMAND16 |

Declaratiile de specificare a tranzitiei stimulului, inclusiv etichete timp/valoare si constructii conditionale |

In plus fata de DIGSTIMn, specificatiile stimulului se fac intr-un fisier extern. FILENAME reprezentand numele fisierului care contine specificatiile stimulilor, iar SIGNAME - numele semnalului de iesire.

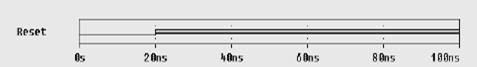

De exemplu, FILESTIMn, poate fi folosit pentru resetarea unui bistabil:

Setarea stimulului RESET

Dorim sa-l setam in asa fel incat sa reseteze bistabilul dupa 40ns.

Se creeaza un fisier stimul RESET.STM, care contine:

Reset

0ns 1

40ns 0

Linia de inceput contine numele tuturor semnalelor descrise in fisier. In acest caz, avem unul singur. Celelalte linii sunt iesirile tranzitiilor de stare corespunzatoare semnalelor din header. Proprietatea FILENAME a lui U2 se completeaza cu numele fisierului care contine descrierea semnalului (RESET.STM). Etichetei de pe firul care leaga U2 cu pinul de CLR al bistabilului, i se da acelasi nume Reset (ca si in fisier) si astfel proprietatea SIGNAME se poate lasa nedefinita. In meniul Edit Simulation Settings, fisierul RESET.STM se trece ca si fisier include.

Acest tip de dispozitive aplica unui nod forme de unda digitale. Scopul este de a furniza intrarea pentru un circuit digital sau portiunea logica a unui circuit mixt. Ele indeplinesc in simulatorul digital rolul pe care-l au sursele independente de tensiune si curent (dispozitivele V si I) in simulatorul analogic.

Exista doua tipuri de dispozitive stimul: generatorul de stimuli (STIM) care foloseste o comanda simpla pentru a genera o gama larga de forme de unda si stimulul fisier (FSTIM) care obtine formele de unda dintr-un fisier extern. Spre deosebire de primitivele digitale, dispozitivele stimul nu dispun de un model de temporizare. Aceasta chestiune este similara cu dispozitivele analogice V si I: caracteristicile de temporizare sunt descrise in dispozitiv si nu intr-un model separat.

Formatul:

U<name> STIM(<width>, <format array>)

+ <digital power node> <digital ground node>

+ <node>*

+ <I/O model name>

+ [STIMULUS=<stimulus name>]

+ [IO_LEVEL=<interface subckt select value>]

+ [TIMESTEP=<stepsize>]

+ <command>*

unde:

<width> precizeaza numarul de semnale (noduri) de iesire

<format array> - specifica formatul <value> (valorilor) utilizate in definirea stimulului. Este o secventa de cifre care care specifica numarul de semnale (noduri) pe care il reprezinta cifra corespunzator din <value> Fiecare cifra din <value> se presupune a fi in baza 2, unde <m> este cifra corespunzatoare din <format array>. Fiecare <value> trebuie sa aiba acelasi numar de cifre ca si <format array>. Suma cifrelor <format array> trebuie sa fie <width> si fiecare bit trebuie sa fie 1, 3 sau 4 (adica binar, octal sau hexazecimal).

<digital power node> <digital ground node>

Aceste noduri sunt utilizate de dispozitivele de interfata care conecteaza nodurile analogice la cele digitale sau invers.

<node>*

Unul sau mai multe noduri carora generatorul de stimuli le genereaza iesirea. Numarul de noduri specificate trebuie sa fie acelasi cu <width>.

<I/O model name>

Numele unui model de I/O, care descrie caracteristicile de comanda ale generatorului de stimuli. Modelele de I/O mai contin numele a pana la patru subcircuite de interfata DtoA, care sunt apelate automat de simulator sa trateze nodurile de interfata. In cele mai multe cazuri, modelul I/O numit IO_STM poate fi utilizat din biblioteca "dig_io.lib".

STIMULUS

Parametru optional pentru a face referire la definitia unui stimul.

IO_LEVEL

Parametru-dispozitiv optional care selecteaza unul dintre cele pana la patru subcircuite de interfata DtoA din modelul de I/O. Simulatorul apeleaza automat subcircuitul selectat in situatia in care un <node> se conecteaza la un dispozitiv analogic. IO_LEVEL este implicit 0. Valorile valide sunt:

0 = Valoarea curenta a .OPTIONS DIGIOLVL (implicit=1)

1 = DtoA1

2 = DtoA2

3 = DtoA3

4 = DtoA4

TIMESTEP

Numarul de secunde per ciclu sau pas tact Timpii de tranzitie specificati in ciclurile de clock (cu sufixul C) sunt multiplicati cu aceasta cantitate pentru a determina momentul actual al tranzitiei (vezi <time> in cele ce urmeaza). Daca TIMESTEP nu este precizat, valoarea implicita se ia zero secunde. TIMESTEP nu are nici un efect asupra valorilor <time>,specificate in secunde (sufixul S)

<command>*

Descriere a stimulilor de generat, folosind una sau mai multe din urmatoarele:

<time> <value>

LABEL=<label name>

<time> GOTO <label name> <n> TIMES

<time> GOTO <label name> UNTIL GT <value>

<time> GOTO <label name> UNTIL GE <value>

<time> GOTO <label name> UNTIL LT <value>

<time> GOTO <label name> UNTIL LE <value>

<time> INCR BY <value>

<time> DECR BY <value>

REPEAT FOREVER

REPEAT <n> TIMES

ENDREPEAT

FILE=<file name>

<time>

Specifica momentul producerii unei noi comenzi <value>, GOTO, or INCR/DECR.

Unitati de timp

Valorile de timp pot fi declarate in secunde sau cicluri de clock (TIMESTEP). Pentru a specifica o valoare de timp in cicluri de clock, se foloseste sufixul C. Altfel, unitatile de masura implicite sunt secundele.

Timpi relativi si absoluti

Valorile de timp pot fi absolute cum ar fi: 45ns sau 10c, sau relative la valori anterioare. Pentru a preciza timpi relativi, valorile se prefixeaza cu "+" (+5ns sau +2c).

<value> este valoarea pentru fiecare nod ( 0, 1, R, F, X, or Z ) si este interpretata folosind <format array>.

<label name> este numele etichetei folosite in declaratiile GOTO.

GOTO <label name> salt la urmatoarea declaratie ne-etichetata, dupa declaratia <LABEL = <label name>>

<n> numarul de repetari ale buclei GOTO. -1 specifica o bucla infinita.

Trebuie retinute urmatoarele:

Tranzitiile care utilizeaza valori de timp absolute intr-o bucla GOTO sunt convertite in timpi relativi pe baza timpilor din comanda anterioara si dimensiunea actuala a pasului.

O sintaxa mai simpla pentru construirea buclelor contorizate in stimulii digitali este sa se utilizeze REPEAT/ENDREPEAT. Se specifica valoarea contorului, de exemplu:

REPEAT 3 TIMES

+ 5ns 0

+ 5ns 1

ENDREPEAT

Pentru o bucla infinita, se foloseste REPEAT FOREVER (echivalent cu REPEAT -1 TIMES). Totdeauna in bucla REPEAT timpii sunt interpretati ca fiind relativi la inceputul buclei.

Informatia de tranzitie (de exemplu. Perechile timp-valoare) poate fi plasata intr-un fisier si accesata o data sau de mai multe ori din dispozitivul STIM, utilizand FILE= declaratie. Sintaxa pentru continutul fisierului este identica cu ceea ce poate sa apara in corpul dispozitivului STIM in sectiunea <command>.

Exemple de STIM

A Primul exemplu creeaza un semnal de reset, utilizabil pentru setarea sau stergerea unui bistabil la inceputul simularii. Nodul, numit Reset, este setat la un nivel zero la momentul zero si la Z, la momentul t=20ns.

UReset STIM(1,1) $G_DPWR $G_DGND

+ Reset

+ IO_STM

+ 0s 0

+ 20ns Z

Figura 5

Acesta este util atunci cand nodul Reset este comandat de un alt dispozitiv care nu reseteaza bistabilul la momentul zero. Utilizand biblioteca de modele de I/O IO_STM, generatorul de stimuli, comanda cu o putere mare si astfel supra-alimenteaza cealalta iesire. Prin aducerea lui in stare de impedanta ridicata pe durata simularii, generatorul de stimuli nu poate afecta nodul.

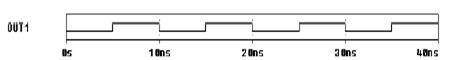

B Al doilea exemplu ( ) este unul simplu al unui stimul de ceas, cu impulsuri la fiecare 5ns. Are un nod de iesire OUT1, si formatul este reprezentat in binar. Acest exemplu, descrie timpul relativ la pasul anterior, se utilizeaza IO_STM care este modelul de I/O pentru dispozitivele stimul si este disponibil in biblioteca dig_io.lib

UEx2 STIM( 1, 1 ) $G_DPWR $G_DGND Out1 IO_STM

+ 0s 0 ;La t=0 initializeaza Out1 la zero.

+ REPEAT FOREVER; ;se repeta bucla pentru un timp nedefinit

+ +5ns 1 ;dupa 5ns Out1 este setat la 1

+ +5ns 0 ;dupa 5ns Out1 este setat pe 0

+ ENDREPEAT

Figura 6

C In exemplul din () este ilustrata utilizarea timestep; un ciclu este egal cu 1ns.

UEx3 STIM( 2, 11 ) $G_DPWR $G_DGND 1 2

+ IO_STM TIMESTEP=1ns

+ 0c 00 ;La momentul t =0ns, ambele noduri sunt setate pe 0.

+ REPEAT 4 TIMES ;Continutul buclei se repeta de patru ori

+ +1c 01 ;dupa 1ns nodul 1 este setat pe 0 ;si nodul 2 setat pe 1.

+ +2c 11 ;dupa 2ns ambele noduri setate pe 1.

+ ENDREPEAT

Figura 7

Dispozitivul stimul fisier, FSTIM, permite obtinerea stimulilor digitali dintr-un fisier. Aceste fisiere sunt utile in special cand numarul de stimuli este foarte mare sau, atunci cand intrarile pentru o simulare provin dintr-o alta simulare (sau chiar de la un alt simulator).

Formatul fisierelor stimul

Formatul acestor fisiere este unul simplu si consta din doua parti:

Antetul (header) care contine o lista de nume de semnale si tranzitii care sunt descrise pe doua coloane care contin momentele tranzitiei si valorile corespunzatoare.

Antetele si tranzitiile trebuie sa fie separate de cel putin o linie libera. In exemplul urmator este prezentat un fisier stimul simplu:

* Antet - contine nume de semnale (sunt permise comentariile standard)

Clock, Reset, In1, In2 ; patru nume de semnale

*Inceputul tranzitiilor

0000 ; valorile sunt binare

10ns 1100

20ns 0101

30ns 1110

40ns 0111

Formatul antetului:

[TIMESCALE=<value>]

<signame 1><signame n>

OCT(<signame bit 3> <signame lsb>)

HEX(<signame bit 4> <signame lsb>)

Antetul consta dintr-o lista nume de semnale si o valoare TIMESCALE optionala. .Numele de semnale pot fi separate prin virgula, spatii sau tab. Lista se poate intinde pe mai multe linii dar nu trebuie sa includa caracterul de continuare +. Numele de semnale trebuie sa corespunda coloanelor cu valori in ordinea aparitiei lor in lista. Antetul poate sa contina pana la 255 de nume, cu toate ca este permis un numar maxim de caractere pe linie.

Functiile radacina OCT si HEX permit gruparea a trei respectiv patru semnale intr-o singura cifra octala sau hexazecimala in coloanele valorilor. De retinut ca trebuie incluse exact trei semnale in functia OCT si exact patru in functia HEX. Semnalele afisate fara functiile radacina vor fi luate implicit ca fiind binare.

In exemplul urmator este prezentata utilizarea functiei HEX.

Clock Reset In1 In2

HEX(Addr7 Addr6 Addr5 Addr4) HEX(Addr3 Addr2 Addr1 Addr0)

ReadWrite

0000 00 0 ; spatiile pot fi utilizate pentru a grupa valorile

10n 1100 4E 0

20n 0101 4E 1

30n 1110 4E 1

40n 0111 FF 0

In exemplu avem patru semnale binare, urmate de producerea a doua functii radacina HEX, urmate de un singur semnal binar. In lista tranzitiilor, sunt sapte valori care corespund in ordine listei de semnale.

Asignarea optionala TIMESCALE este folosita pentru a scala valorile de timp din tranzitii. TIMESCALE trebuie sa se gaseasca pe o linie separata. Daca nu este specificata, ia valoarea 1.0.

Formatul tranzitiilor

<time> <value>* Imediat dupa linia libera de dupa antet, simulatorul cauta liniile care contin tranzitiile. Tranzitiile constau dintr-o valoare de timp urmata de una sau mai multe valori corespunzatoare numelor de semnale din antet.

<time> si lista de valori <values> trebuie sa fie separate de cel putin un spatiu sau tab.

<time>

momentele tranzitiilor sunt intotdeauna exprimate in secunde. Pot fi absolute 45ns, 1.2e-8, sau 10; sau relative la momentul anterior. Pentru specificarea timpului relativ, este necesar sa se foloseasca prefixul +: +5ns sau +1e-9. Valorile de timp sunt intotdeauna scalate cu valoarea TIMESCALE. Este util daca valorile de timp din fisier sunt exprimate ca valori intregi dar, unitatile actuale sunt de exemplu 10ns. In cele ce urmeaza, este prezentat un exemplu de utilizare TIMESCALE.

<value>*

Fiecare valoare corespunde unui singur semnal binar (implicit) sau intregului grup de semnale din functiile radacina OCT sau HEX Numarul de valori listate trebuie sa fie acelasi cu numarul total de semnale binare si functii radacina din antet. <values> valide sunt:

Tabel 17

|

Binar |

OCT |

HEX |

|

|

Logic/Numeric |

0-7 |

0-F |

|

|

Indiferent |

X |

X |

X |

|

Impedanta ridicata |

Z |

Z |

Z |

|

Crescator |

R |

R | |

|

Cazator |

F |

F |

Cand valoarea din coloana HEX sau OCT este un numar, simulatorul il converteste in binar si asigneaza valoarea corespunzatoare a fiecarui bit (zero sau unu) semnalelor din functia radacina. Bitii sunt asignati de la msb la lsb. Cand <value> este X, Z, R, sau F, toate semnalele din functia radacina iau acea valoare. Trebuie mentionat ca in coloana HEX nu poate sa existe o valoare cazatoare (F), deoarece F este utilizat ca valoare numerica.

TIMESCALE=10ns ; trebuie sa apara pe o linie separata

Clock, Reset, In1, In2

HEX(Addr7 Addr6 Addr5 Addr4) HEX(Addr3 Addr2 Addr1 Addr0)

ReadWrite

0 0000 00 0

1 110R 4E 0 ; tranzitia se produce la 10ns

2 0101 4E 1

+ 3 1111 4E 1 ; tranzitia se produce la 50ns

7 011F C3 0 ; tranzitia se produce la 70ns

8 11X0 C3 1

Dispozitivul FSTIM

FSTIM este utilizat pentru a accesa unul sau mai multe semnale dintr-un fisier stimul. Acelasi fisier poate fi accesat de mai mult de un FSTIM. Un dispozitiv FSTIM poate chiar sa faca referire la acelasi semnal ca si alt FSTIM. In timpul simularii poate fi utilizat orice numar de fisiere stimul.

U<name> FSTIM(<# outputs>)

+ <digital power node> <digital ground node>

+ <node>*

+ <I/O model name>

+ FILE=<stimulus file name>

+ [IO_LEVEL=<interface subckt select value>]

+ [SIGNAMES=<stimulus file signal name>*]

Exemple:

U1 FSTIM(1) $G_DPWR $G_DGND

+ IN1 IO_STM FILE=DIG1.STM

U2 FSTIM(4) $G_DPWR $G_DGND

+ ADDR3 ADDR2 ADDR1 ADDR0

+ IO_STM

+ FILE = DIG_2.STM

+ SIGNAMES = AD3 AD2 AD1 AD0

U3 FSTIM(4) $G_DPWR $G_DGND

+ CLK PRE J K

+ IO_STM

+ FILE = FLIPFLOP.STM

+ SIGNAMES = CLOCK PRESET

Optiuni si argumente

<# outputs> specifica numarul de noduri comandate de acest dispozitiv.

<digital power node> <digital ground node>

Aceste noduri sunt utilizate de dispozitivele de interfata care conecteaza nodurile analogice la nodurile digitale sau invers.

<node>*

Unul sau mai multe nume de noduri care rezulta din fisierul stimul. Numarul de noduri precizat trebuie sa fie acelasi cu <# outputs>.

<I/O model name>

Numele unui model de I/O, care descrie caracteristicile de comanda ale stimulului. Modelele de I/O mai contin si numele a pana la patru subcircuite de interfata DtoA apelate automat de simulator pentru a trata nodurile de interfata. In cele mai multe cazuri, modelul de I/O, numit IO_STM poate fi folosit din biblioteca dig_io.lib.

FILE

Numele fisierului stimul care trebuie accesat de catre acest dispoztiv. <stimulus file name> se poate specifica fie ca sir intre ghilimele sau ca expresie text.

IO_LEVEL

Parametru optional care selecteaza unul dintre cele patru subcircuite de interfata AtoD sau DtoA din modelul de I/O. Simulatorul apeleaza subcircuitul selectat in eventualitatea ca un nod care conecteaza o primitiva, conecteaza de asemenea si un dispozitiv analogic. Daca nu se specifica altfel, IO_LEVEL este implicit 0. Valorile valide sunt:

0 = valoarea curenta a.OPTIONS DIGIOLVL (implicit =1)

1 = AtoD1/DtoA1

2 = AtoD2/DtoA2

3 = AtoD3/DtoA3

4 = AtoD4/DtoA4

SIGNAMES

Specifica numele semnalelor din fisierul stimul la care va face referire dispozitivul FSTIM. Numele de semnale corespund, in ordine, nodurilor conectate la dispozitiv.

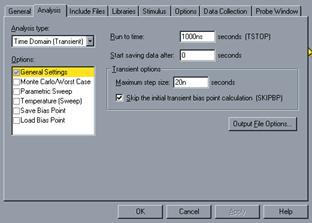

Setarea analizei tranzitorii

Din meniul PSpice

al Capture, se alege New Simulation

Profile (Figura

8 ) si i se da un nume. Dintre optiunile

tipurilor de analiza, se selecteaza Time Domain (Transient), iar in

caseta Run to Time, se introduce durata analizei.

|

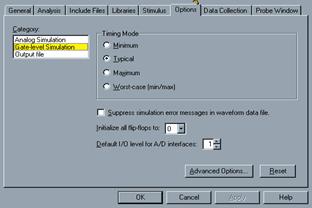

Din fereastra de setare a simularii, se alege Options, pentru a stabili comportamentul componentelor logice, pe parcursul simularii.

In fereastra Options, se alege simulare la nivel de poarta - Gate-level Simulation.

Selectarea intarzierilor de propagare

Toate dispozitivele digitale - inclusiv

primitivele si modelele din biblioteci - deruleaza simulari,

folosind caracteristici de temporizare dintre urmatoarele

posibilitati: minime, tipice, maxime, sau pentru cazul cel mai

defavorabil. Intarzierea se poate seta pentru intreg circuitul sau, pentru

dispozitive individuale.

![]()

Intarzieri de propagare pentru intreg circuitul - sunt setate

implicit in fereastra Options. Daca se doreste stabilirea

intarzierilor de propagare pe dispozitiv individual, se deschide fereastra de

editare a proprietatilor componentei respective si in

pozitia corespunzatoare MNTYMXDLY, se completeaza cu valori de

la 1 la 4, unde:

1 - reprezinta minimul

2 - tipic

3 - maximul

4 - cazul cel mai defavorabil (min/max)

Implicit, valoarea respectiva este setata pe 0, ceea ce inseamna utilizarea valorii setate in fereastra Options, pentru intreg circuitul.

Initializarea bistabilelor

X - stare indiferenta (necunoscuta). Este o stare in care raman pana la setarea sau resetarea explicita, sau pana la intrarea intr-o stare cunoscuta, pe clock.

0 - toate dispozitivele de acest tip, vor fi aduse la zero

1 - toate dispozitivele de acest tip sunt presetate

Pornirea se face cu comanda Run din meniul PSpice (din Capture) sau butonul de pe bara de utilitati.

Analiza rezultatelor

Afisarea formelor de unda se face cu un osciloscop soft. Diagrama de timp produsa de simulare, poate fi observata si modificata interactiv. In cazul simularilor mixte analogice/digitale, se poate face afisarea simultana a celor doua tipuri de variatii in timp.

Se genereaza doua forme de iesire: fisierul cu rezultatul simularii si cel cu datele diagramelor de timp. Calculele si rezultatele raportate in fisierele de simulare, reprezinta o contabilizare a simularii si totodata o metoda informativa si flexibila de evaluare a rezultatelor simularii.

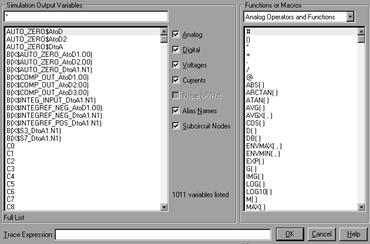

Din meniul comenzii Trace, se alege Add Trace, pentru a mai adauga semnale la afisare.

Se pot construi expresii, selectand operatorii, functiile si/sau macrourile din lista Functions and Macros si Simulation Output Variables. In caseta Trace Expression, se pot tasta direct expresiile de urmarit IN1, OUT2, etc.

Adaugarea de semnale logice la o diagrama (Figura 10)

La definirea expresiilor logice de urmarire (trace), se pot include combinatii de semnale digitale, busuri, semnale constante, constante de bus operatori logici, macro, etc.

In acest scop, se aplica urmatoarele reguli:

O expresie sau o operatie logica dintre doi operanzi bus, va avea ca rezultat o valoare bus suficient de larga incat sa poata contine rezultatul.

O

operatie aritmetica sau logica dintre un operator semnal si

unul bus, rezulta intr-o valoare de bus.

Sintaxa pentru exprimarea unei variabile sau expresii de iesire, este:

digital_output_variable[;display_name]

sau:

digital_expression[;display_name]

Adaugarea busurilor la afisarea diagramelor de timp

Pot fi evaluate si afisate pana la 32 de semnale ca bus, chiar daca n-au facut parte initial din magistrala. Cand se adauga un bus, lista de semnale trebuie inchisa intre paranteze acolada.

Sintaxa completa este:

[;[display_name][;radix]]

sau

[;display_name][;radix]]

unde:

|

signal_list |

Lista de nume de noduri digitale (pana la 32), separate de virgula sau spatiu, intr-o ordine descrescatoare |

|

bus_prefix[msb:lsb] |

Varianta de exprimare a semnalelor de pe bus |

|

[;display_name] (optional) |

Sir text, pentru etichetarea busului pe grafic, in locul folosirii numelor implicite |

|

[;radix] (optional) |

Sistemul de numeratie utilizat pentru afisarea valorilor de pe bus |

Valorile acceptate pentru radix sunt:

Binar - B

Zecimal - D

Hexazecimal - H sau X

Octal - O

Exemple:

; A; O - semnifica un bus de trei biti, Q0 fiind cel mai putin semnificativ. Reprezentarea grafica se va face in octal, avand eticheta A.

; ;d - bus de date de patru biti. Valorile vor avea o reprezentare zecimala si, din moment ce nu s-a specificat nici o eticheta, va aparea cu numele din lista de semnale.

este echivalenta cu

Urmarirea

incalcarilor de temporizare si a hazardului

Cand apar probleme in schema cum ar fi: violari de setare/mentinere, latimea impulsurilor sau hazardul de temporizare pentru situatia cea mai defavorabila, PSpice A/D, va salva mesaje in fisierele rezultat sau in cele de date (.out, .csd) Se pot selecta mesaje sau formele de unda asociate si mesajul detaliat, apare imediat. PSpice poate detecta deasemenea hazardurile persistente, care pot avea efect potential asupra iesirii primare a circuitului sau, asupra starii interne a schemei.

Hazardul persistent

Problemele logice constau de obicei in incalcari si/sau hazarduri de temporizare. Incalcarile temporizarii, le includ pe cele de SETUP, HOLD sau de durata minima a impulsului WIDTH, din specificatiile de componenta. Acest tip de violare poate produce o modificare in comportamentul de stare al schemei si posibil a rezultatului (respectiv iesirea schemei).

De exemplu, (Figura 13) se poate considera o schimbare asincrona a

datelor la intrarea circuitului. O modificare a datelor foarte aproape de frontul

tactului e1, duce la o violare de SETUP. Intr-o implementare hard, iesirea

bistabilului, se poate modifica sau nu. Totusi, unele scheme nu sunt

sensibile la aceste date individuale pierdute, deoarece la al doilea clock (e2

in exemplu), stocheaza datele. Proiectantul trebuie sa tina

cont de importanta erorilor de temporizare asupra comportamentului global

al schemei.

Hazardurile de temporizare sunt mai usor de identificat prin simularea unei scheme pentru functionare in cazul cel mai defavorabil, de regula aproape de limitele de timp critice. In asemenea situatii, PSpice raporteaza conditii de ambiguitate (AMBIGUITY CONVERGENCE). Aceste situatii, pot sa creeze sau nu probleme in functionarea schemei.

Totusi, se pot identifica situatii in care pot provoca probleme majore. In exemplul urmator este prezentata o asemenea situatie. Datorita sosirilor simultane a doua ambiguitati de temporizare (cu origini independente), la intrarile portii G1, se semnaleaza hazard (AMBIGUITY CONVERGENCE), ceea ce inseamna ca la iesirea G1 poate aparea un glitch. Trebuie retinut faptul ca iesirea portii G1, comanda doua dispozitive: G2 si L1. Efectele glitch-ului asupra iesirii portii G2 nu exista deoarece, pe cealalta intrare avem in permanenta 0 (adica iesirea va fi 0, indiferent de semnalul de pe intrarea cealalta ). In schimb, poate determina functionarea incorecta a bistabilului. Acesta este un exemplu de hazard persistent.

Datorita faptului ca poate avea influenta negativa asupra functionarii, hazardul trebuie eliminat, corectand schema.

Simulare mixta analog/digitala

Interconectarea componentelor analogice si digitale

Inaintea simularii, rularea programului Netlist, traduce schema intr-o lista de componente legate prin noduri. Lista de conexiuni contine o vedere plana a circuitului (fara ierarhii). Pspice A/D extrage definitiile tuturor componentelor modelate, ca subcircuite, privindu-le ca si o colectie de componente primitive si conexiuni prin noduri.

Primitivele logice care intra in componenta dispozitivelor, determina modul in care PSpice A/D proceseaza o interfata analogica/logica, cu componenta. Adica, modelul de I/O al fiecarei primitive logice conectate la interfata, ofera PSpice, informatia necesara.

PSpice recunoaste trei tipuri de noduri: analogice, logice si de interfata. Tipul nodului, este determinat de componenta legata la el. Daca toate componentele legate la un nod sunt analogice, atunci nodul este analogic. Daca sunt logice, avem de-a face cu un nod logic si in situatia in care sunt mixte, nodul este de interfata.

PSpice A/D "rupe" automat nodurile de interfata intr-un nod pur analogic si unul sau mai multe noduri digitale prin inserarea unuia sau mai multor sub-circuite analogice/digitale de interfata. Conecteaza deasemenea o alimentare la sub-circuitul de interfata, pentru a completa generarea interfetei.

Pentru vizualizarea rezultatelor simularii la o interfata analog/digitala din schema, utilizand analizorul grafic de forme de unda:

Trebuie plasat un marcaj pe netul de interfata corespunzator. Nodurile aditionale create de PSpice raman transparente.

Se vizualizeaza rezultatele selectand observatii (traces) din lista variabilelor de iesire.

Selectia subcircuitului de interfata

Subcircuitul de interfata analog-digital (AtoD) si cel digital-analog (DtoA), trateaza translatia dintre tensiunile analogice/impedante si starile logice, sau invers. Componenta principala a unui subcircuit de interfata este sau o componenta N (intrare logica: DtoA), sau O (iesire logica: AtoD). Componentele N si O, apar incapsulate in bibliotecile de modele, nefiind astfel necesara definirea lor atunci cand se utilizeaza bibliotecile standard.