PROIECT DE TEHNOLOGIE DIDACTICA

- Schema bloc a circuitului pentru determinarea celui mai mare divizor comun -

Anul de studiu: anul IV

Subiectul lectiei: Schema bloc a circuitului pentru determinarea celui mai mare divizor comun

Capitolul: Limbajul de descriere a circuitelor numerice VHDL

Data: 18.11.2002

Datorita implicatiei pe care Proiectare asistata de calculator o are azi in toate profesiile, rezulta caracterul ei interdisciplinar. Proiectare asistata de calculator nu poate fi privita numai ca o disciplina independenta si nu poate fi tinuta intre bariere create artificial.

In diverse domenii de activitate, rezolvarea problemelor concrete impune foarte des o faza de modelare. Proiectare asistata de calculator este printre putinele discipline care ofera instrumentar adecvat pentru invatarea modelarii logice. De asemenea, Proiectare asistata de calculator pune la dispozitie cele mai spectaculoase posibilitati de simulare care este o parte a modelarii (neclasica si necostisitoare).

Studentii trebuie sa inteleaga conexiunile dintre Proiectarea asistatǎ de calculator si necesitǎtile societǎtii si sa fie capabili sa se adapteze dinamicii schimbarilor determinate de aceste conexiuni. ).

Analiza grupului:

Grupul de studenti este un grup omogen in care nu exista probleme in asimilarea cunostintelor, atitudinea lor pentru disciplina proiectare asistata de calculator fiind pozitiva, interesati de obiect. Studentii sunt interesati de descoperirea a noi tehnici de rezolvare a problemelor existind situatii in care dezbat solutiile si le analizeaza dpdv al performantelor.

Orele au un caracter dinamic in care studentii sunt incurajati sa cunoasca opiniile fiecaruia, sa-si dezvolte gindirea critica si creativa, sa evalueze solutiile posibile la probleme, sa participe deschis la discutiile pe tema propusa, devenind spontani si siguri pe sine.

Obiective de referinta:

(Obiectivele de referinta, specifica rezultatele asteptate ale invatarii si urmaresc in special progresul realizat in acumularea de cunostinte si in formarea deprinderilor, de regula pe perioada unui an de studiu.

Obiective de referinta

a) cunoasterea pana la un anumit nivel de detaliu, a sistemele de operare/mediilor de programare cele mai des folosite (MS-DOS, Windows, UNIX, LINUX);

b) cunoasterea unui limbaj de programare de nivel inalt (Pascal, C, etc.) ca bazǎ pentru dezvoltarea cunostintelor unui limbaj de descriere a circuitelor numerice (VHDL, Verilog);

c) cunoasterea principalelor tehnici de testare a unui circuit numeric;

d) cunoasterea unui program de simulare a circuitelor numerice (Modelsim, ActiveHDL);

e) cunoasterea unui program de sintezǎ numericǎ a circuitelor numerice (Leonardo, Synplicity);

f) cunosterea unui program de proiectare in tehnologia ariilor logice programabile (FPGA) a schemei bloc a circuitului obtinut (Xilinx ISE 4.1i);

g) cunoasterea tehnicilor de proiectare a produselor program cu caracter stiintific, a metodelor de elaborare a algoritmilor si circuitelor, algoritmilor fundamentali, algoritmilor optimali, tehnicilor de optimizare a algoritmilor si circuitelor; studentii trebuie sa aiba si capacitatea de apreciere a complexitatii unor algoritmi si circuite;

h) cunoasterea structurii si arhitecturii sistemelor de calcul si a notiunilor elementare de hard, care sa le permita sa-si faca o impresie precisa despre caracteristicile tehnice ale oricarui calculator;

i) cunoasterea celor mai uzitate programe utilitare, editoare de texte si editoare grafice, pachete de programe de compresie (arhivare), programe antivirus, notiuni primare de inginerie de sistem, etc.;

j) cunoasterea principalelor modalitati de exploatare ale facilitatilor oferite de retele (locale si interconectate), servicii Internet, documente Html, facilitati multimedia, etc.

Tipul lectiei: mixt

Durata lectiei: 50 min

Locul de desfasurare: laboratorul de proiectare asistatǎ de calculator. (in laboratoare se lucreaza pe grupe astfel incit majoritatea studentilor lucreaza individual la cite un calculator. Laboratorul de proiectare asistata de calculator este dotat cu 8 calculatoare conectate la Internet pe care se afla instalate atit programe folosite la orele de proiectare a circuitelor numerice:VHDL, Verilog cit si programe de simulare, programe de sintezǎ logicǎ a circuitelor numerice, programe de implementare in tehnologia ariilor logice programabile cit si editoare grafice, procesoare de texte, foi de calcul tabelar/ baze de date etc.

B. RESURSE DIDACTICE NECESARE:

RESURSE MATERIALE

Calculatoare (calculatorul e un mediator eficient, care ne ajuta in integrarea notiunilor si informatiilor intr-un ansamblu ordonat si coerent. Facilitatile de prelucrare automata a datelor, de afisare a rezultatelor, de comanda automata a unor mijloace audiovizuale fac posibila obtinerea unui sistem complet de verificarea cunostintelor. Se realizeaza practic individualizarea invatarii, creste randamentul insusirii constiente a cunostintelor prin aprecierea imediata a raspunsurilor studentilor, obliga la cunoasterea integrala de catre fiecare studentin parte a intregului material predat si asigura munca activa si progresiva a studentilor).

Placǎ de dezvoltare care contine circuitul numeric programabil (circuit FPGA), circuitele conexe si de interfatare. Dupǎ descrierea algoritmului pentru gǎsirea celui mai mare divizor comun a douǎ numere se va obtine schema bloc a circuitului asociat algoritmului. Circuitul va fi apoi descris in limbajul de descriere a circuitelor numerice VHDL si testat. Dupǎ testare, circuitul va fi sintetizat intr-o tehnologie FPGA obtinindu-se astfel reprezentarea realǎ a algoritmului initial. Circuitul sintetizat logic cu ajutorul programului de sintezǎ este folosit pentru programarea circuitului FPGA de pe placa de dezvoltare.

Caiet de laborator (Datorita caracterului aplicativ al orelor de laborator, exista tendinta de a se nota putin si de cele mai multe ori secvente izolate si necorelate intre ele. Textele sursa ale problemelor constituie totusi biblioteca la purtator a studentului, cea mai rapid accesibila, cu conditia ca programele sa fie insotite de explicatii corespunzatoare. Sursele programelor fara enuntul problemelor si specificatiile de programare sunt texte moarte.

Marele dezavantaj al metodei consta in timpul pierdut cu copierea pe caiete, dar acesta este compensat de obtinerea unui text sursa testat, corect si reprezentand o implementare verificata. )

Proiect didactic

Indrumarul de laborator, note de curs

RESURSE PEDAGOGICE

"Psihologia educatiei", autor: dr. Maria Carcea;

"Pedagogie didacticǎ", autor: dr. Mihai Stanciu;

Proiectare asistatǎ de calculator" D. Burdia, G.St.Popescu

RESURSE PROCEDURALE (RP)

Conversatia (Cv): consta in dialogul dintre profesor si elev, in care profesorul nu trebuie sa apara in rolul examinatorului permanent, ci in rolul unui colaborator care nu numai intreaba ci si raspunde la intrebarile studentilor. Prin metoda conversatiei se stimuleaza gandirea studentilor in vederea insusirii, fixarii si sistematizarii cunostintelor si deprinderilor, in vederea dezvoltarii spiritului de colaborare si de echipa. Se asigura astfel o participare activa din partea studentilor, intrebarile putand fi adresate in orice moment al lectiei.

Metoda conversatiei este frecvent utilizata in invatarea Informaticii, determinand un dialog continuu intre studenti si profesor, cu conditia respectarii unor reguli elementare de colaborare constructiva, care sa nu determine diminuarea demersului didactic, ci sa-l amplifice si sa-l consolideze. Indiferent de forma de conversatie, intrebarile trebuie sa fie precise, sa vizeze un singur raspuns. Intrebarea trebuie sa nu contina raspunsul, sa nu ceara un raspuns prin da sau nu, sa contribuie la dezvoltarea gandirii.

Raspunsurile acceptate trebuie sa fie corecte, complete, exprimate in termeni precisi, sa oglindeasca o intelegere deplina a problemei abordate. Cand raspunsurile sunt gresite, trebuie sa fie imediat corectate, prin discutii ample, edificatoare, care sa deduca cauza greselii si sa elimine atat greseala cat si posibilitatea reaparitiei ei.

Conversatia este importanta prin faptul ca ajuta la formarea limbajului informatic, un instrument pretios si indispensabil pentru dezvoltarea rationamentului logic, a gandirii studentului.

Dificultatile pe care studentul le intampina in formarea limbajului de specialitate pot lasa urme in plan afectiv, se pot repercuta asupra dezvoltarii inteligentei acestuia. De aceea, se impune o analiza amanuntita a cauzelor acestor dificultati, scoaterea lor in evidenta, facandu-se prin examinari scrise, orale, reprezentari schematice, utilizarea simbolurilor specifice.

Stapanirea limbajului se reflecta in rezolvarea problemelor si intelegerea textelor si documentatiilor de specialitate. Nestapanirea acestuia provoaca inhibitie, imposibilitatea comunicarii sau chiar o comunicare si o intelegere defectuoasa, facandu-l pe studentul timid, incoerent sau chiar ridicol in exprimare.

Devine clar ca o conversatie se face prin intrebari. Acestea trebuie sa satisfaca urmatoarele conditii:

sa fie precise (vizand un singur raspuns);

sa nu contina raspunsul, sa fie instructive;

sa stimuleze gandirea si capacitatea de creativitate a studentilor (de ce?, din ce cauza?, in ce caz?, etc.);

sa fie formulate prin enunturi variate;

sa se adreseze intregului colectiv vizat;

sa introduca intrebari ajutatoare atunci cand raspunsul este eronat sau partial.

Raspunsurile acceptate trebuie sa fie nu numai corecte ci si exprimate in termeni precisi si sa oglindeasca un anumit nivel de intelegere. Raspunsurile eronate trebuie corectate imediat, prin discutii individuale. Cadrul didactic trebuie sa dirijeze conversatia astfel incat ideile sa fie bine conturate inainte de a trece la altele si lectia sa-si pastreze caracterul unitar.

Exercitiul (Ex): La modul cel mai general, exercitiile pot fi privite ca actiuni concrete efectuate in mod constient si repetat in scopul dobandirii unor priceperi si deprinderi (mai rar cunostinte) noi pentru a usura anumite activitati si a contribui la dezvoltarea unor aptitudini.

Avantajele metodei exercitiului sunt:

Se poate forma o gandire productiva, creatoare, cu implicatie financiara.

Ofera posibilitatea castigarii unei anumite independente.

Ofera posibilitatea initierii unui dialog-conversatie cu obiective precise asupra unor metode si solutii.

Activeaza atitudinea critica si poate creste discernamantul studentilor in privinta celor mai bune metode de lucru.

Ofera posibilitatea depistarii si eliminarii erorilor.

Ofera o anumita posibilitate profesorului pentru a analiza si evalua activitatea sau performantele generale ale unui elev.

Prin urmare exercitiile sunt actiuni efectuate in mod constient si repetat de catre studentcu scopul dobandirii unor priceperi si deprinderi si chiar cunostinte noi, pentru a usura alte activitati si a contribui la dezvoltarea altor aptitudini. Insusirea cunostintelor de proiectare asistatǎ de calculator este organic legata de exersarea utilizarii unor soft-uri de aplicatie, de rezolvarea unor probleme de programare, etc. Nu exista lectie in care sa nu se aplice aceasta metoda.

Este clar ca metoda nu contribuie numai la formarea priceperilor si deprinderilor de lucru cu calculatorul, ci contribuie substantial la dezvoltarea unui rationament flexibil si operant.

Pentru profesor, alegerea, formularea si rezolvarea problemelor si apoi exploatarea rezultatelor obtinute constituie o sarcina de importanta deosebita.

Problematizarea si descoperirea fac parte dintre metodele formativ-participative, care solicita gandirea creatoare a studentului, ii pun la incercare vointa, ii dezvolta imaginatia, ii imbogateste experienta. In lectiile in care se aplica aceste metode profesorul alege problemele, le formuleaza, dirijeaza invatarea si controleaza munca depusa de studentin toate etapele activitatii sale. Aceasta metoda este caracteristica unor lectii de aplicatii practice de laborator.

Metoda invatarii prin descoperire este frecvent aplicata in momentul in care este necesara folosirea programelor utilitare, a soft-urilor de aplicatie, etc.

Procesele care izvorasc din situatii reale, care implica calculatorul in rezolvarea unor probleme apartinand diferitelor sfere ale vietii de zi cu zi, analiza acestor probleme, alegerea structurilor de date pe care se muleaza informatia oferita de mediul inconjurator, pasii algoritmilor si programarea in sine, implica folosirea metodei problematizarii, iar aplicarea acestei metode necesita formarea unor deprinderi ce nu se obtin decat printr-un exercitiu indelungat.

Rezolvarea de probleme, practica curenta in invatarea Informaticii, poate fi privita ca un proces prin care studentul descopera ca o alta combinatie de reguli invatate anterior conduc la rezolvarea unei noi situatii problematice. Formularea de probleme de catre studentii insisi, constituie forme ale creativitatii si presupune ca studentii si-au format deprinderi intelectuale eficace din punct de vedere al generalizarii si aplicabilitatii (orice solutie genereaza o noua problema).

Problemele propuse pot fi inspirate din viata cotidiana, din cunostintele dobandite prin studiul altor discipline, din generalizarea unor probleme de informatica rezolvate anterior, probleme de perspicacitate, jocuri, etc.

Modelarea:

Modelarea, ca metoda pedagogica poate fi descrisa ca fiind un mod de lucru prin care gandirea studentului este condusa la descoperirea adevarului, folosind un asa numit model si utilizandu-se rationamentul prin analogie.

Modelarea are o mare valoare euristica colaterala, prin utilizarea ei putandu-se dezvolta spiritul de observatie, capacitatea de analiza, sinteza, creativitatea. Ideea ar fi sa putem determina studentii sa descopere singuri modelul. Astfel studentul se obisnuieste sa creeze noi probleme ce trebuiesc rezolvate, sa adapteze algoritmi cunoscuti la situatii noi, etc.

Utilizarea modelelor in realizarea algoritmilor presupune stabilirea unor analogii si in organizarea datelor de intrare. Invatarea algoritmilor este legata de cunoasterea modului de organizare a datelor, de structurile de date.

Etapa cea mai importanta este cea a descoperirii algoritmului si a structurii optime a circuitului dpdv al ariei ocupate si vitezei de lucru, urmata de stabilirea modului de organizare a datelor, dar importanta acestui aspect este esentiala in determinarea performantelor produsului program care implementeaza algoritmul si circuitul.

Modelarea ca metoda pedagogica, este definita ca un mod de lucru prin care gandirea studentului este condusa la descoperirea adevarului cu ajutorul modelului, gratie rationamentului prin analogie.

Modelarea similara, consta in realizarea unui sistem de aceeasi natura cu originalul, care sa permita evidentierea trasaturilor esentiale ale originalului.

O gama variata de probleme de analizǎ sunt exprimate algoritmic. Pentru implementarea intr-un limbaj de descriere a circuitelor (hardware) a unui algoritm pentru determinarea celui mai mare divizor comun, studentul are nevoie de un model reprezentat de un program, cum ar fi cel de si prin mici modificari, el poate obtine multe alte programe care implementeaza algoritmi care rezolva probleme clasice, cum ar fi: determinarea celui mai mic multiplu comun, determinarea produsului a douǎ numere binare, etc.

Momentele cunoasterii in procesul simulǎrii sunt:

trecerea de la algoritm la modelul descriptibil in limbaj VHDL;

transformarea modelului sau experimentarea(testarea) pe model;

transferul pe circuitul numeric a rezultatelor obtinute pe model;

verificarea experimentala pe circuitul implementat in tehnologie FPGA, a proprietatilor obtinute pe model.

Invatarea Proiectǎrii asistatǎ de calculator prin modelare presupune doua etape. Intr-o prima etapa, invatarea se va face pe baza modelelor construite de profesori, etapa in care se vor analiza trasaturile modelului si compararea lui cu originalul. Pentru a reliefa conditiile pe care trebuie sa le indeplineasca modelul se vor da si contraexemple. In a doua etapa, studentii vor fi deprinsi sa construiasca singuri modele. Importanta descoperirii modelului de catre student consta in faptul ca studentul este obisnuit a reprezenta intr-o forma standard conditiile impuse de problema si adanceste convingerea sa ca Proiectare asistata de calculator este un domeniu in care rezultatele pozitive se obtin doar printr-o inlantuire logica de rationamente.

Se va pune accentul pe intelegerea pasilor unui algoritm descris in VHDL si se va incuraja prezentarea oricaror metode care exclud modelul si care se impun prin eleganta si eficienta. Studentii vor fi incurajati sa-si dezvolte si sa-si prezinte ideile proprii, contribuind in acest fel la cresterea increderii in posibilitatile lor, in valoarea ideilor lor. Ei nu trebuie sa fie obligati sa reproduca ideile altora, sa astepte ca totul sa fie prezentat de profesor, sa asimileze retete, ci sa descopere metode noi, sa le prezinte, analizeze si perfectioneze printr-o comunicare continua si constructiva.

Explicatia (E)

PROCEDEE DE EVALUARE

A evalua rezultatele scolare inseamna a determina, a cuantifica masura in care obiectivele programului de instruire au fost atinse, precum si eficienta metodelor de predare-invatare folosite. Evaluarea este o componenta esentiala a procesului de invatamant, indeplinind functii bine conturate:

functia de constatare si diagnosticare a performantelor obtinute de studenti, explicate prin factorii si conditiile care au condus la succesul sau insuccesul scolar si care sunt de o mare diversitate (psihologica, pedagogica, sociala, etc.);

functia de reglare si perfectionare a metodologiei instruirii pe baza informatiilor obtinute din explicarea factorilor si conditiilor care au determinat rezultatele la invatatura;

functia de predictie si decizie care vizeaza desfasurarea in viitor a activitatii didactice;

functia de selectie si clasificare a studentilor in raport cu rezultatele scolare obtinute;

functia formativ-educativa, de ameliorare a metodelor de invatare folosite de studenti, de stimulare si optimizare a invatarii;

functia de perfectionare a intregului sistem scolar.

Forme de evaluare :

a) Evaluarea initiala care conduce la formarea unei imagini despre bagajul de cunostinte cu care studentul porneste la drum. Trebuie sa ne asiguram de ceea ce cunoaste studentul inainte de a-l invata alte lucruri. Aceasta forma de verificare creeaza si o imagine asupra posibilitatilor de progres ale studentului, asupra capacitatii lui de invatare, in functie de care se va stabili programul de instruire.

b) Evaluarea formativa (continua) este forma de evaluare pe care profesorul o aplica pe intreaga durata a programului de instruire in cadrul lectiilor si la incheierea unui capitol. Aceasta forma de verificare ofera permanent informatii cu privire la eficienta programului de instruire si permite profesorului sa ia cele mai potrivite masuri de prevenire a insuccesului scolar, ajutand totodata la ameliorarea metodelor de predare-invatare. Verificarea ritmica ofera, pe baza mecanismului de feed-back continuu, semnalele necesare atat studentului cat si profesorului, fiind un veritabil metronom al activitatii didactice.

Examinarea prin probe practice este caracteristica disciplinelor cu pronuntat caracter aplicativ, iar Informaticii cu atat mai mult. Ea se poate desfasura in forme variate, de la realizarea de programe simple sau editari de texte sau grafica pe durata unei ore, lucrandu-se individual sau in grup, pana la aplicatii complexe, realizate intr-un interval mai lung de timp. Sunt verificate si evaluate cunostintele teoretice necesare realizarii lucrarii, cat si deprinderile si dexteritatile necesare executarii ei.

Este necesara formarea la studenti a capacitatii de autoevaluare, prezentandu-le criteriile de apreciere, ceea ce va mari increderea studentului in propriile sale forte si va inlatura orice urma de suspiciune.

FORME DE ORGANIZARE A CLASEI

activitatea frontala, activitate individuala

C. COMPETENTE SPECIFICE

Cunoasterea algoritmului de determinarea a celui mai mare divizor comun, a metodei de descriere in limbajul de descriere a circuitelor numerice VHDL;

Formarea deprinderilor de lucru cu solutiile la nivel de circuit ale algoritmilor;

D. COMPETENTE DERIVATE

Cunoasterea algoritmului si a posibilitǎtilor de descriere in limbajul VHDL: descriere comportamentalǎ, descriere la nivel de registru, descriere la nivel de poartǎ logicǎ (netlist);

Identificarea datelor din algoritm cu cele din descrierea la nivel comportamental in limbaj VHDL;

Identificarea metodei optime de descriere a algoritmului cu ajutorul metodei de descriere la nivel de registru;

Intelegerea legaturii dintre descrierea comportamentalǎ si descrierea la nivel de registru;

Bibliografie

-"Proiectare asistatǎ de calculator" - D.Burdia, G.ST. Popescu.

E. STRUCTURA LECTIEI PE SECVENTE DE INSTRUIRE:

|

Timp |

Activitate desfasurata de profesor |

Activitate desfasurata de studenti |

|

3 min |

MOMENT ORGANIZATORICefectuarea prezentei studentilor si consemnarea absentelor verificarea starii de functionare a calculatoarelor se capteaza atentia prin anuntarea tilului lectiei "Schema bloc a circuitului pentru determinarea celui mai mare divizor comun" si se explica modul de desfasurarea a activitatii |

raportarea absentilor raportarea eventualelor defectiuni |

|

12 min |

REACTUALIZAREA CUNOSTINTELORSe propune un test de verificare a cunostintelor legate de algoritmul celui mai mare divizor comun (ca si mecanism general) Se discuta apoi variantele corecte, timp in care studentii isi vor nota singuri testul (vezi anexa) Atentia profesorului va fi indreptata asupra modului in care studentii au receptat testul si se urmareste manifestarile si starile lor emotionale. Se urmareste rezultatul testului iar daca se observa ca unele subiecte nu au fost atinse atunci se rediscuta notiunile respective dar nu inainte de a se incerca o reformulare a lor. Se reactualizeaza si fixeaza cunostintele dobandite la ora corespunzatoare de teorie. ANUNTAREA SUBIECTULUI |

activitate individuala studentii rezolva testul studentii discuta unele dificultati legate de test raspund la intrebari |

|

12 min |

PREZENTAREA CONTINUTULUI NOII LECTII Se asigura ca toata clasa este atenta si pregatita sa intervina. Modelul algoritmului pentru determinarea celui mai mare divizor comun, corpul procesului de calcul. Prezentarea modelului: Process Begin A := A_in; B := B_in; If ( A/= 0 and B /= 0) then While ( B /= 0) loop While (A >= B) loop A := A-B; End loop; Swap := A; A := B; B := Swap; End loop; Else A := 0; End if; Y := A; End process ; Se pun intrebari verificindu-se intelegerea modelului in asamblul lui de catre toti studentii. INTENSIFICAREA ATENTIEI 2. Intrebari: De ce se descrie algoritmul prin constructia concurentǎ process? Ce face instructiunea if? Ce face prima instructiune while-loop? Care sunt conditiile pentru intrarea in a doua buclǎ loop? In ce stare este procesul dupǎ terminarea executiei ultimei instructiuni din corpul sǎu? De ce sa ales utilizarea tipului de datǎ variable si nu tipul signal? Ce se intampla la revenirea in arhitectura programului ? Cum se face testul algoritmului in arhitectura programului? 3. Aplicatie exemplu -Produsul a douǎ numere binare conform algoritmului de multiplicare BOOTH. In rezolvarea problemei de programare se va tine seama de urmatoarele etape: - Analiza initiala a problemei prin care se stabileste modul (intrare, iesire) si tipul datelor de intrare (bit, std_logic, unsigned), intervalele de variatie a datelor de intrare, a variabilelor de lucru (date intermediare) precum si formatul si intervalele de variatie a datelor de iesire. Tot in aceasta etapa se va stabili un algoritm (plan) de rezolvare, exprimat in limbajul de descriere a circuitelor numerice VHDL, pe baza caruia se va permite fiecarui student sa lucreze independent. - Rezolvarea propriu-zisa a problemei este etapa in care se realizeaza transpunerea intr-un limbaj hardware a algoritmului stabilit in prima etapa. In prealabil, algoritmul este reprezentat in una dintre formele cunoscute, se stabilesc variabilele de lucru, forma lor de alocare, prelucrarile ce vor avea loc, apoi se trece la implementarea in limbajul VHDL. Daca rezolvarea se poate face pe mai multe cai, trebuie sa se sublinieze, daca este posibil, calea optima. - Verificarea solutiei sau solutiilor obtinute va permite studentului sa-si dea seama daca solutia obtinuta este cea corecta. In aceasta etapa intervine profesorul cu seturi de date de test care sa cuprinda daca este posibil, majoritatea (daca nu toate) cazurilor existente ridicate de problema si in special cazurile critice, la limita, ale datelor de intrare. |

se noteaza in caiete se raspunde la intrebari studentii participa cu raspunsuri dind dovada insusirii si asimilarii cunostintelor predate in lectiile anterioare se rezolva la tabla si se noteaza in caiete caietul de aplicatii practice de laborator trebuie sa contina in mod obligatoriu: un rezumat al cunostintelor teoretice necesare realizarii aplicatiilor practice; enuntul problemei a carei rezolvare constituie obiectul activitatii; algoritmul de rezolvare rezolvarea, sau acea parte din solutie care constituie esenta rezolvarii (programul sau secventele cele mai importante, cu precizarea in clar a ceea ce s-a realizat in acea etapa); un rezumat al cunostintelor noi dobandite in urma rezolvarii problemelor. |

|

18 min |

ASIGURAREA TRANSFERULUI DE INFORMATII SI OBTINEREA PERFORMANTEISe propune spre rezolvare urmatoarea problema ( in timpul lucrului la calculator studentii vor fi indrumati individual de catre profesor ) Sa se genereze functia VHDL care efectueazǎ raportul a douǎ numere binare. Ex: Se introduc: A=00001001 C=01011001 Se va afisa : Cit=1001, Rest=1000 Se pun intrebari suplimentare si ajutatoare studentilor. Se incurajeaza munca individuala si independenta. |

se lucreaza individual la calculator se va da solutia pe tabla si se va nota in caiete se urmareste cit de activi, cit de atenti sunt studentii |

|

5 min |

INCHEIEREA LECTIEISe mai explica o data cum functioneaza algoritmul de gǎsire a celui mai mare divizor comun a douǎ numere dar de aceasta data discutia se va purta cu ajutorul studentilor Se anunta tema pentru acasa: problemele 1, 2, 3, 4 / manual pagina 120 |

se noteaza tema in caiete |

Concluzii:

Repetarea materiei parcurse serveste la improspatarea cunostintelor dobandite, ajuta la formarea de noi corelatii, reluarea materiei predate intr-un cadru mai general, uneori cu completarea unor cunostinte. Repetarea (lectiei anterioare) s-a facut inainte de predarea unei lectii noi print-un test la inceputul orei.

Este necesara formarea la studenti a capacitatii de autoevaluare, prezentandu-le criteriile de apreciere, ceea ce va mari increderea studentului in propriile sale forte si va inlatura orice urma de suspiciune.

Predarea s-a facut prin intermediul tehnicii modelarii. Lectia cuprinde un model de rezolvare ce este valabil pentru majoritatea problemelor de acest gen. S-a urmarit modul in care studentii au receptionat noua lectie avindu-se in vedere atitudinile, manifestarile pe parcursul lectiei, cit de activi au fost si interesati de a participa la ora.

Din discutiile de final a reiesit faptul ca studentii si-au insusit aceasta noua tehnica de rezolvare a problemelor participarea lor fiind activa si plina de interes.

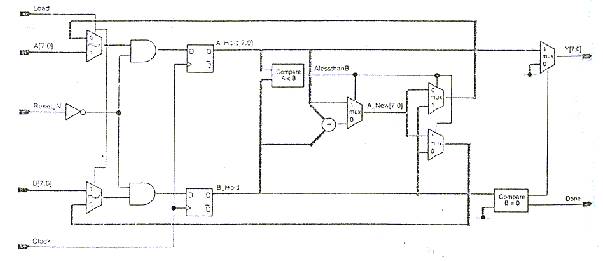

Figura 1.

Schema bloc a circuitului pentru determinarea celui mai mare divizor comun a

douǎ numere

Explicarea schemei bloc a circuitului pentru determinarea celui mai mare divizor comun a douǎ numere:

Porturile de intrare ale circuitului declarate in entitatea gcd sint: clk -semnalul periodic de ceas, reset - semnal de stergere, load - semnal de incǎrcare al registrilor, A,B - intrǎrile de date de tip intreg fǎrǎ semn de lungime DIM.

DIM este o constantǎ de tip generic care permite modificarea printr-un singur parametru a numǎrului de biti pe care lucreazǎ circuitul.

Porturile de iesire sint Done - indicǎ sfirsitul operatiei de determinare a celui mai mare divizor comun pentru 2 biti de intrare si Y care contine rezultatele aplicǎri algoritmului fiecǎrei perechi de biti de intrare.

Codul scris in limbaj VHDL pentru determinarea celui mai mare divizor comun a douǎ numere este prezentat in continuare.

library IEEE;

use IEEE.STD_LOGIC_1164.all;

use Ieee.numeric_std.all ;

entity gcd is

generic ( dim : natural := 8);

port(

clk : in STD_LOGIC;

reset : in STD_LOGIC;

load : in STD_LOGIC;

A, B : in unsigned (dim-1 downto 0);

Done : out std_logic;

Y : out unsigned (dim-1 downto 0)

);

end gcd;

architecture rtl of gcd is

signal A_nou, A_hold, B_hold : unsigned (dim-1 downto 0);

signal A_maimicdecitB : std_logic;

begin

--incarca cei 2 registri pentru case B_hold < A_hold

incarc: process(Clk)

begin

if rising_edge(Clk) then

if (Reset = '0') then

A_Hold <= (others => '0');

B_Hold <= (others => '0');

elsif (Load = '1') then

A_Hold <= A ;

B_Hold <= B;

elsif (A_maimicdecitB = '1') then

A_Hold <= B_hold ;

B_Hold <= A_nou;

else

A_hold <= A_nou;

end if;

end if;

end process;

scad : process (A_Hold, B_Hold)

begin

if (A_Hold >= B_Hold) then

A_maimicdecitB <= '0' ;

A_nou <= A_Hold - B_Hold;

else

A_maimicdecitB <= '1';

A_nou <= A_Hold ;

end if;

if (B_Hold = '00000000' ) then

Done <= '1' ;

Y <= A_Hold ;

else

Done <= '0' ;

Y <= (others => '0' );

end if;

end process ;

end architecture ;

Explicarea programului VHDL pentru determinarea celui mai mare divizor comun a douǎ numere :

Arhitectura entitǎtii gcd se numeste rtl si contine semnalele A_nou, A_hold, B_hold de tip intreg fǎrǎ semn, A_maimicdecitB de tip std_logic si douǎ constructii proces. Primul proces implementeazǎ doi registri si functionezǎ astfel: cind semnalul reset are valoarea zero semnalele A_hold si B_hold sint setate la zero.

Cind semnalul reset nu este zero si semnalul de incǎrcare load este activ ('1' logic) bitii de intrare de pe proturile A si B sint memorate in registrii A_hold si B_hold . Cind semnalele reset si load sint inactive si semnalul A_maimicdecitB este mai mic decit B_hold, valorile registrilor A_hold si B_hold sint interschimbate.

Cind semnalele reset si load sint inactive si semnalul A_maimicdecitB este mai mare decit B_hold, semnalul A_hold isi mentine valoarea. In corpul celui de al doilea proces se testeazǎ mai intii dacǎ A_hold este mai mare sau egal cu B_hold.

Dacǎ da, rezultatul scǎderii A_hold-B_hold este atribuit semnalului A_nou si la urmǎtorul front crescǎtor al semnalului de ceas, semnalului B_hold. Daca A_hold este mai mic decit B_hold atunci scǎderea (A_hold-B_hold) nu mai poate avea loc iar A_nou este atribuit semnalului B_hold.

Interschimbarea A_hold si B_hold sint interschimbate pe urmǎtorul front al semnalului de ceas. A doua instructiune if testeazǎ dacǎ B_hold este zero, in cazul adevǎrat semnalul DONE ia valoarea '1' iar valoarea semnalului A_hold este transmisǎ portului de iesire Y.

Fisierul care contine vectorii de intrare este:

49 7

30 5

27 1

40 40

250 5

Programul VHDL de test pentru circuitul care calculeazǎ cel mai mare divizor comun este:

library ieee;

use ieee.numeric_std.all;

use ieee.std_logic_1164.all;

--use ieee.std_logic_unsigned.all;

use std.textio.all;

-- Add your library and packages declaration here

entity gcd_tb is

-- Generic declarations of the tested unit

generic(

dim : NATURAL := 8 );

end gcd_tb;

architecture TB_ARCHITECTURE of gcd_tb is

-- Component declaration of the tested unit

file TESTDATAFile: text open read_mode is 'gcd_test.vhs';

file ResultsFile : text open write_mode is 'gcd_test_results.vhs';

component gcd

generic(

dim : NATURAL := 8 );

port(

clk : in std_logic;

reset : in std_logic;

load : in std_logic;

A : in UNSIGNED((dim-1) downto 0);

B : in UNSIGNED((dim-1) downto 0);

Done : out std_logic;

Y : out UNSIGNED((dim-1) downto 0) );

end component;

component gcd_test

port (

clk : IN std_logic ;

reset : IN std_logic ;

load : IN std_logic ;

A : IN std_logic_vector (7 DOWNTO 0) ;

B : IN std_logic_vector (7 DOWNTO 0) ;

Done : OUT std_logic ;

Y : OUT std_logic_vector (7 DOWNTO 0)

);

end component ;

-- Stimulus signals - signals mapped to the input and inout ports of tested entity

signal clk : std_logic := '0';

signal reset : std_logic;

signal load : std_logic;

signal A : UNSIGNED((dim-1) downto 0);

signal B : UNSIGNED((dim-1) downto 0);

-- Observed signals - signals mapped to the output ports of tested entity

signal Done,done_test : std_logic;

signal Y,Y_test,Y_1 : UNSIGNED((dim-1) downto 0);

-- Add your code here

constant TCLK : time := 20 ns;

constant GCD_temp: integer := 100 ;

begin

-- Unit Under Test port map

UUT : gcd

generic map (

dim => dim

)

port map (

clk => clk,

reset => reset,

load => load,

A => A,

B => B,

Done => Done,

Y => Y

);

UUT1: gcd_test port map

(

clk => Clk,

reset => reset,

load => load,

A(7) => A(7),

A(6) => A(6),

A(5) => A(5),

A(4) => A(4),

A(3) => A(3),

A(2) => A(2),

A(1) => A(1),

A(0) => A(0),

B(7) => B(7),

B(6) => B(6),

B(5) => B(5),

B(4) => B(4),

B(3) => B(3),

B(2) => B(2),

B(1) => B(1),

B(0) => B(0),

Done => done_test,

Y(7) => Y_test(7),

Y(6) => Y_test(6),

Y(5) => Y_test(5),

Y(4) => Y_test(4),

Y(3) => Y_test(3),

Y(2) => Y_test(2),

Y(1) => Y_test(1),

Y(0) => Y_test(0)

);

--Below VHDL code is an inserted .srcgcd_test.vhs

--User can modify it .

-- Add your stimulus here

clk <= not clk after TCLK/2;

process

variable A_var, B_var, Y_Ref_var : integer range 0 to 255;

variable TestData: line;

variable Bufline: line;

variable Passed: bit := '1';

begin

Reset <= '0';

Load <= '0' ;

wait for Tclk; Reset <= '1';

wait for TCLK ; Reset <= '1';

while not endfile(TestDataFile) loop

readline(TestDataFile,TestData);

read(TestData, A_var);

read(TestData, B_var);

read(TestData, Y_ref_Var);

A <= to_unsigned(A_var,8);

B <= to_unsigned(B_var,8);

Y_1 <= to_unsigned(Y_Ref_var, 8);

wait for TClk ; Load <= '1';

wait for Tclk ; Load <= '0';

for m in 0 to (GCD_temp -1 ) loop

wait for TClk;

if (Done = '1') then

if (Y /= Y_1 or Y_test /= Y_1 or Done_test /= '1' ) then

Passed := '0' ;

write (Bufline, string'('Eroare: A='));

write (Bufline, to_integer(A));

write (Bufline, string'('B='));

write (Bufline, to_integer(B));

write (Bufline, string'('Y='));

write (Bufline, to_integer(Y));

write (Bufline, string'('Y_1='));

write (Bufline, to_integer(Y_1));

writeline (Resultsfile, Bufline);

end if ;

end if;

end loop;

end loop;

if (Passed = '1') then

write(Bufline,string'('algoritmul GCD e corect'));

writeline(Resultsfile,Bufline);

end if;

end process;

end TB_ARCHITECTURE;

configuration TESTBENCH_FOR_gcd of gcd_tb is

for TB_ARCHITECTURE

for UUT : gcd

use entity work.gcd(rtl);

end for;

end for;

end TESTBENCH_FOR_gcd;

Explicarea programului VHDL de test:

Programul instantiazǎ douǎ circuite: circuitul proiectat (initial) cu eticheta UUT si circuitul care rezultǎ in urma sintezei logice (UUT1). Perioada semnalului de ceas a fost stabilitǎ la 20 ns. In corpul procesului sint aplicati stimulii din fisierul de test gcd_test.vhs, porturilor de intrare a celor douǎ circuite.

Dupǎ un timp predefinit de 100 perioade de ceas sint comparate iesirile circuitelor. Rezultatele comparatiei sint scrise in fisierul gcd_test_results.vhs. Variabila Passed are rolul de a semnaliza aparitia de neconcordante (erori) intre iesirile omoloage ale celor douǎ circuite.

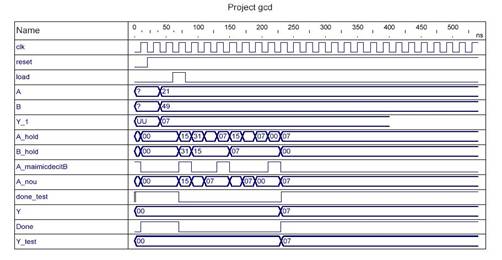

Figura

2.Formele de undǎ obtinute in urma rulǎrii circuitului de test.

In figurǎ se pot observa porturile de intrare (clk, reset, load, A, B) semnalele interne (A_hold, B_hold, A_maimicdecitB, done_test, Y_test) si porturile de iesire (Y, Done).

Functionarea corectǎ a solutiei de circuit aleasǎ se poate observa calculind c.m.m.d.c pentru porturile de intrare A (valoare 21) si B (valoare 49). Valoarea corectǎ a c.m.m.d.c a celor douǎ numere este prezentǎ la portul de iesire Y (valoare 7).

Figura 3.

Schema bloc a plǎcii de dezvoltare care contine circuitul FPGA in

care se implementeazǎ circuitul pentru determinarea celui mai mare divizor

comun a douǎ numere

Placa de dezvoltare XESS contine urmǎtoarele circuite: circuite de interfatare serialǎ (Serial Port), circuite de interfatare paralelǎ (Parallel port), RAMDAC pe 24 bit (VGA Output), codec audio stereo (Stereo Input, Stereo Output), conectori de expansiune, circuit numeric reprogramabil din familia Virtex FPGA (XCV-300) cu o arie de 300000 porti logice sintetizabile, 4 bancuri de memorie SRAM cu capacitatea de512kx8 biti, port de alimentare. Circuitul sintetizat este implementat in circuitul reprogramabil cu ajutorul programului Xilinx ISE 4.1i prin circuitul de interfatare paralela a placii de dezvoltare.

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |