Universitatea "Dunarea

de Jos",

Universitatea "Dunarea

de Jos",

Facultatea de inginerie electrica si electronica

Descriere a functionarii proiectului

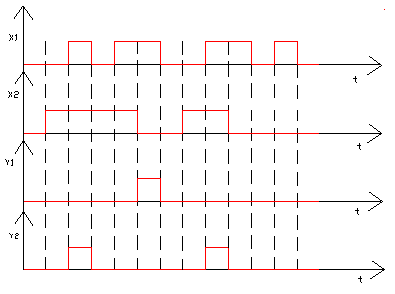

Proiectul consta in obtinerea unor forme de unda in functie de semnalele aplicate la intrare.

Semnalul de clock al bistabilelor este generat de un oscilator realizat cu o porta de tip Trigger Schmith. Rezistenta aferenta oscilatorului este de 180k iar capacitatea condensatorului este de 47pF. Aceastea au fost calculate pentru o perioada de aproximativ 10us. Poarta Trigger Schmith folosita se afla in integratul CD140106, acesta continand 6 astfel de porti.

Semnalul de la sursa de curent de 5V este prelucrat de oscilator si transformat in semnal dreptunghiular. Cand circuitul este alimentat, la intrarea inversorului avem nivelul 0, deci la iesire va fi 1. Prin rezistenta se incarca condensatorul pana cand tensiunea la intrarea inversorului ajunge la pragul pozitiv al portii Trigger Schmith. Odata atinsa aceasta valoare, la intrare vom avea nivel 1 logic, iar la iesire 0 logic, iar condensatorul incepe sa se descarce pana cand valoarea tensiunii atinge valoarea aferenta pragului negativ al portii Trigger Schmith.

Tema: Sa se proiecteze, cu circuite logice CMOS, un automat finit pornind de la formele de unda date.

Tabelul cu starile echivalente:

|

x1x2 Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Reducerea numarului de stari:

0,1,2,11->0 3,4,5->1 6,7,8->2 9,10->3

|

x1x2 Q |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Codificarea starilor

Regula 1: Starile prezente care au aceeasi stare urmatoare,pentru aceleasi intrari, primesc coduri adiacente.

Regula 2: Starile urmatoare unei stari prezente, care se afla pecoloane cu intrari diacente, primesc coduri adiacente.

Regula 3: Starile prezente, care au in corespondenta iesirii dentice pentru aceleasi intrari, primesc coduri adiacente.

Regula 4: Codurile cu mai multe zerouri se atribuie starilor careapar o singura data pe mai multe coloane.

Regula 5: Starile circuitului intre care exista tranzitii primesc coduri adiacente.

Rezultatul codarii:

1-01 2-10 3-11

|

x1x2 q1q2 |

||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

K |

J |

Q+ |

Q |

|

X |

|

|

|

|

X |

|

|

|

|

X |

|

|

|

|

|

X |

|

|

|

J |

K |

Q+ |

|

Q |

||

|

|

Tabel de adevar Tabelul de tranzitie

Tabele de tranzitie si adevar pentru bistabile de tip JK.

Prelucrarea semnalului cu bistabile de tip JK.

|

Y2 |

Y1 |

K1 |

J1 |

K0 |

J0 |

q0+ |

q1+ |

q0 |

q1 |

x2 |

x1 |

|

|

|

X |

X |

|

|

|

|

|

|||

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

|

X |

X |

|

|

|

|

|

||

|

|

|

X |

X |

|

|

|

|

|

|||

|

|

|

X |

X |

|

|

|

|

|

|||

|

|

|

|

X |

X |

|

|

|

|

|

||

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

X |

X |

|

|

|

|

|

|||

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

|

|

|

|

X |

X |

|

|

|

|

|

||

|

|

|

|

X |

X |

|

|

|

|

|

||

|

|

|

X |

X |

|

|

|

|

|

|||

|

|

|

X |

X |

|

|

|

|

|

|||

|

|

|

|

X |

X |

|

|

|

|

|

||

|

X |

X |

X |

X |

X |

X |

X |

X |

|

|

|

|

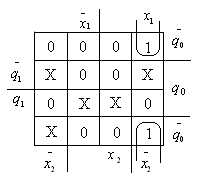

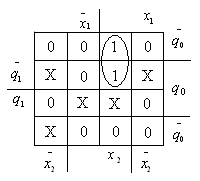

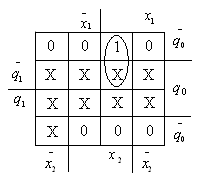

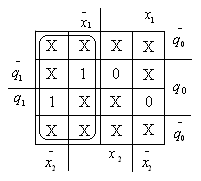

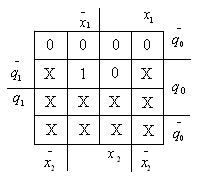

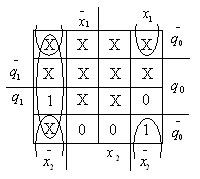

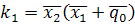

Cu ajutorul diagramelor Veitch-Karnaugh se minimizeaza functiile:

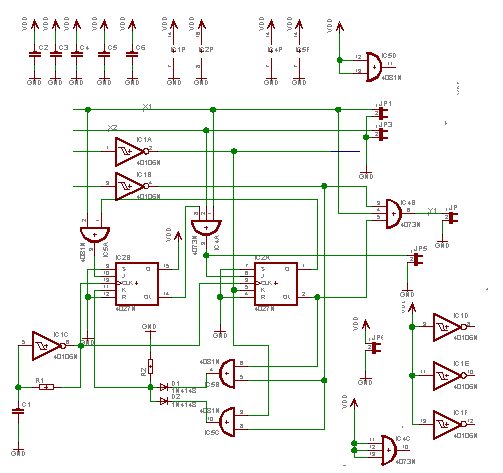

Schema circuitului cu bistabil de tip JK realizata cu porti logice

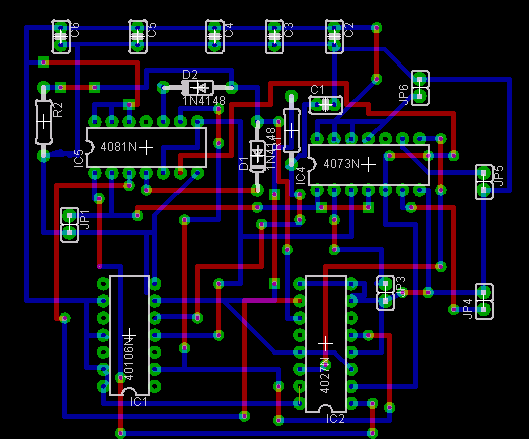

Cablajul circuitului realizat cu bistabil de tip JK

Calculul constantei de timp (oscilatorul RC):

unde

= perioada clock-ului,

,

si

date de catalogul

inversorului cu histerezis MC14106B. Se cere ca frecventa clock-ului sa fie

de 500 kHz. Rezulta T=2μs.

alegem R=180K si calculam C=47pF

Lista de componente

|

Nume componenta |

Tipul |

Cod |

Valoare |

Numar bucati |

|

Bistabil JK |

integrat |

CD4027N | ||

|

Porti logice |

integrat |

CD4073N | ||

|

Porti logice |

integrat |

CD4081N | ||

|

Porti logice |

integrat |

CD4071N | ||

|

Inversoare |

integrat |

CD40106N | ||

|

Condensator |

analogic |

C | ||

|

Jumper | ||||

|

Rezistenta |

analogic |

R |

10k |

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |