Sumatoarele paralele pe principiul selectarii prin transport a sumei

Urmarind aceeasi tinta de imbunatatire a performantelor tinzand spre o latenta logaritmica caracteristica principiului CLA, sumatoarele CSkA apeleaza la calcule efectuate in paralel, aceeasi idee fundamentala, dar aplicata intr-un mod diferit sta la baza configurarii unor sumatoare la care adunarea efectueaza prin asa numitul algoritm al sumei conditionata de valoarea lui carry (conditional-sum addition algorithm [ParL00]). In esenta, algoritmul prevede ca blocuri de ranguri sa calculeze suma simultan, in paralel, in doua variante acceptand apriori valorile 0, respectiv 1, pentru carry-in in respectivele blocuri si selectand valorile corecte la iesirile blocurilor, ulterior, cand valoarea reala, adevarata a lui carry devine cunoscuta. In acest mod, valoarea lui carry conditioneaza alegerea valorii sumei dintre cele doua antecalculate.

Exista doua categorii de sumatoare functionand pe baza acestui algoritm, si anume cele avand suma selectata prin valoarea transportului, asa numite carry-select adders (a caror prescurtare a fost aleasa CSeA), din aceeasi motive explicate in paragraful anterior la CSkA) si cele avand suma conditionata de valoarea transportului, asa numite conditional-sum adders (CSuA), care vor fi analizate in paragraful urmator. Asemanatoare ca principiu, cele 2 tipuri de sumatoare se deosebesc prin implementarea acestora.

Supunand analizei sumatoarele CSeA, consideram, intr-o prima instanta, un sumator RCA pe n biti pe care il impartim in doua, iar partea corespunzatoare celor n/2 ranguri mai putin semnificative calculeaza, in mod direct, cei n/2 biti corespunzatori ai sumei. Partea corespunzatoare celor n/2 ranguri mai semnificative este substituita prin 2 sumatoare RCA de n/2 ranguri, fiecare calculand, concomitent cu RCA-ul pentru partea mai putin semnificativa, suma si carry-out-ul in doua ipostaze diferite, si anume aplicand valoarea 0 pentru carry-in la unul dintre cele 2 RCA-uri pentru bitii mai semnificativi ai sumei, respectiv valoarea 1 pentru carry-in la celalalt RCA. Cele trei sumatoare , functionand in paralel, termina calculele aproximativ in acelasi timp, cand devine cunoscut carry-out-ul real, generat de RCA-ul corespunzator bitilor mai putin semnificativi ai sumei (si carry-out-ului) doar pe cea care corespunde.

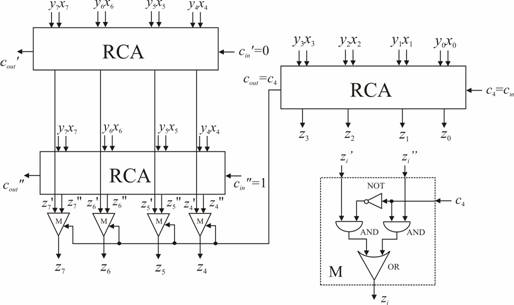

Fig. 2.28

Astfel,

in calitate de exemplu, in figura 2.28 se prezinta un CSeA pe n = 8

ranguri alcatuit din trei sumatoare pe 4 ranguri, admise, fara a

pierde din generalitate, de tip RCA. Se observa ca bitii mai

semnificativi ai sumei sunt calculati, in paralel, pentru doua

scenarii, anume pentru situatia cand cin = 0, fiind

obtinuti bitii de la z4 la z7, respectiv

pentru situatia cand cin = 1, fiind obtinuti

bitii de la z4 la z7. Selectia dintre cei doi

subvectori binari suma se efectueaza sub controlul carry-out-ului

generat de sumatorul RCA corespunzator partii mai putin

semnificative a sumei, prin intermediul unui strat de multiplexoare M, dintre

care unul este detaliat la nivel de poarta in figura 2.28. Apreciind

aceasta noua configuratie .sumator in raport cu reperul RCA,

constatam ca la intarzierea corespunzatoare propagarii

seriale defavorabile pe RCA-ul mai putin semnificativ (in general, ![]() niveluri logice) se

adauga intarzierea pe multiplexorul M (pe care o admitem de doua

niveluri logice), cu alte cuvinte latenta, exprimata in niveluri

logice, este egala cu (n+2) fata de cele 2n corespunzatoare

RCA-ului de aceleasi dimensiuni. Diferenta de performanta

intre cele doua solutii este cu atat mai pregnanta, cu cat n ia

valori mai mari, tinzand spre injumatatirea latentei

(desigur, aceata apreciere este prea optimista atunci cand cele trei

segmente de sumator nu mai sunt de tipul RCA). Trebuie insa metionat

ca aceasta estimare trebuie amendata intrucat semnalul carry-out

generat de sumatorul RCA mai putin semnificativ (in cazul nostru, c4)

comanda, in general, un numar mare de multiplexoare, ceea ce, in

anumite tehnologii, poate degrada performanta destul de mult. Pe de

alta parte, apreciind costul in termeni de numar de porti,

dublarea sumatorului RCA pentru bitii suma mai semnificativi si

stratul de multiplexoare tinde, grosier, spre o dublare a costului pentru CSeA

fata de RCA. Remarcam insa, din nou, ca aceste

evaluari de performanta si cost sunt influentate, in

mod decisiv, de factorul tehnologic.

niveluri logice) se

adauga intarzierea pe multiplexorul M (pe care o admitem de doua

niveluri logice), cu alte cuvinte latenta, exprimata in niveluri

logice, este egala cu (n+2) fata de cele 2n corespunzatoare

RCA-ului de aceleasi dimensiuni. Diferenta de performanta

intre cele doua solutii este cu atat mai pregnanta, cu cat n ia

valori mai mari, tinzand spre injumatatirea latentei

(desigur, aceata apreciere este prea optimista atunci cand cele trei

segmente de sumator nu mai sunt de tipul RCA). Trebuie insa metionat

ca aceasta estimare trebuie amendata intrucat semnalul carry-out

generat de sumatorul RCA mai putin semnificativ (in cazul nostru, c4)

comanda, in general, un numar mare de multiplexoare, ceea ce, in

anumite tehnologii, poate degrada performanta destul de mult. Pe de

alta parte, apreciind costul in termeni de numar de porti,

dublarea sumatorului RCA pentru bitii suma mai semnificativi si

stratul de multiplexoare tinde, grosier, spre o dublare a costului pentru CSeA

fata de RCA. Remarcam insa, din nou, ca aceste

evaluari de performanta si cost sunt influentate, in

mod decisiv, de factorul tehnologic.

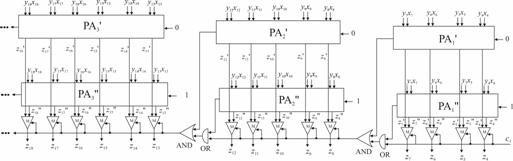

Principiul carry-select, aplicat mai sus la patitionarea sumatorului in jumatati, poate fi extins impartind sumatorul in sferturi, sau continuand divizarea, obtinand corespunzatoare accelerari la calculul sumei. In plus, segmentele in care se divide sumatorul nu trebuie sa contina acelasi numar de ranguri, ele putand fi de dimensiune variabila. O astfel de solutie tehnica pleaca de la observatia conform careia daca pentru un bloc de b ranguri, care este dublat avem o intarziere data de 2b niveluri logice si adaugand la aceasta pe cea data de doua niveluri logice prin intermediul carora se admite ca este obtinut carrz-out-ul celor doua blocuri (din cont' si cont'', vezi si fig. 2.28), atunci, intrucat (2b + 2 = 2(b+1)), rezulta ca urmatorul bloc, succesiv inspre partea mai semnificativa, este indicat sa aiba cu un rang mai mult, adica (b+1) ranguri. Astfel, sa extindem sumatorul de n = 8 ranguri din fig. 2.28, obtinand configuratia din fig. 2.29.

In figura se prezinta schematic, pentru rangurile de la 4 la 18, partea de schema care este dublata constand din 3 blocuri de sumatoare paralele (parallel adders, PA) care au, parcurgandu-le inspre bitii mai semnificativi, cite un rang in plus. Fiecare bloc este dublat avand un etaj superior la care carry-in este 0 si unul inferior (la aceasta, pentru claritatea figurii, au fost omise intrarile, care sunt aceleasi de la etajul superior) la care carry-in este 1. Alegerea subvectorilor suma se realizeaza cu multilpezoarele M care selecteaza valori zi', respectiv zi'' dependent de valoarea carry-out-ului care soseste de la blocul anterior. Primul bloc, cel corespunzator bitilor suma cei mai putin semnificativi z0 si z3, care nu este dublat, nu a mai fost figurat, pentru claritate, fiind identic cu cel din fig.2.28, cu metiunea ca, de aceasta data, nu am mai restrictionat principiul constructiv la RCA, considerandu-l un PA general, indiferent metoda care a stat la baza sintezei acestuia. Imediat ce este cunoscut carry-out-ul (c4) a acestui prim bloc pot fi selectati noi subvectori binari suma in dependenta de activarea carr-out-urilor de bloc. Se remarca generarea acestora prin cele doua porti, AND si OR, constituind un etaj de multiplexare simplificat datorita excluderii din consideratii, la fiecare bloc, a perechii imposibile de valori (cout' cout'' = 10).

Fig. 2.29

Asemanator cu sumatoarele carry-skip, si cele carry-select, am vazut, pot fi configurate din blocuri de dimensiune variabila. Tot asa, ambele pot fi structurate pe mai multe niveluri (multilevel). In cazul in sumatoarelor carry-select, o posibila astfel de constructie imparte cele n ranguri in blocuri de dimensiune n/4, dintre care blocul corespunzator rangurilor mai putin semnificative nu este dublat, iar celelalte trei sunt dublate functionand dupa scenariile cunoscute, cu intrarile de carry-in conectate la 0, respectiv 1 logic [ParL00]. Realizarea pe doua niveluri se refera la partea de multiplexare, mai exact, la selectia jumatatii mai semnificative a bitilor suma. O astfel de structura este posibil sa conduca la implementarea favorabila a conceptului de pipeline aritmetic (asupra caruia se va revni), dar, si in acest caz, optiunea pentru apelarea la principiul constructiv multilevel este decisiv influentata de tehnologia de fabricatie.

|

Politica de confidentialitate |

| Copyright ©

2026 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |