Dupa cum s-a prezentat anterior familia TTL standard este caracterizata de un timp de propagare de tp=10 ns la o putere consumata de Pc=10 mW. In aplicatiile in care tp nu are o importanta atat de mare, dar se urmareste o putere consumata pe poarta cat mai mica se utilizeaza familia TTL de mica putere (LP-TTL) caracterizata de putere consumata pe poarta Pc=1 mW si un timp de propagare este practic identic cu cea a portii TTL- standard, dar valoarea rezistentelor din circuit sunt marite pentru a obtine un consum mai redus.

Micsorand valorile rezistentelor din circuitul portii TTL standard scad timpii de propagare, marindu-se in schimb puterea disipata pe poarta. Cand frecventa de lucru este elementul important, in afara micsorarii valorii rezistentelor si a utilizarii diodelor de limitare de la intrarea circuitului standard i se mai aduc doua imbunatatiri:

- inlocuirea tranzistorului T4 cu un repetor pe emitor in montaj de amplificator Darlington.

- inlocuirea rezistentei R3 din emitorul lui T2 cu o rezistenta neliniara.

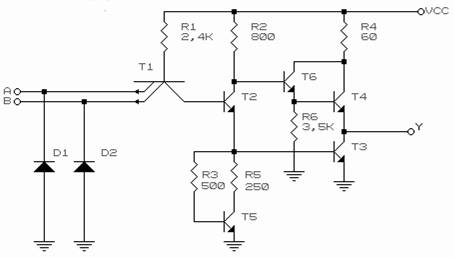

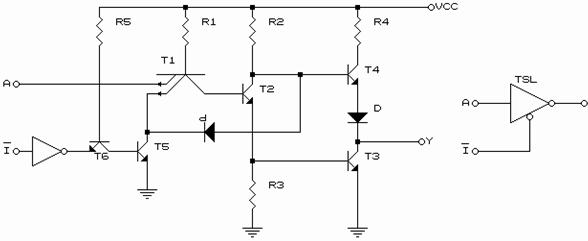

In figura 4.16 se prezinta schema unei porti TTL rapide.

Rolul elementelor introduse este urmatorul:

1.a. Rezistenta echivalenta a dipolului constituit de T5 si R3 si R5 este mare la tensiuni VBE3 mici, ceea ce duce la o intrare mai rapida in conductie a lui T3 (deci un timp de comutatie directa mai mic).

1.b. Pentru tensiuni VBE3 mai mari corespunzatoare intrarii in saturatie a lui T3 (VBE3>0,8 V) rezistenta echivalenta este mica (mai mica ca R3 din schema portii TTL standard) suntand jonctiunea BE3 si micsorand astfel curentul de baza a lui T3 cea ce are ca efect micsorarea sarcinii stocate in baza si respectiv accelerarea comutatiei inverse (evacuarea sarcinilor stocate in baza) deci tpHL devine mai mic.

2. Inlocuirea tranzistorului T4 cu un repetor pe emitor in montaj de amplificator Darlington. Jonctiunea EB a tranzistorului T6 indeplineste acelasi rol cu dioda D si anume de a bloca tranzistorul T4 cand T3 conduce. Grupul format din tranzistoarele T4 si T6 si rezistenta R6 constituie o structura Darlington care are o rezistenta de intrare (vazuta in baza lui T6) de valoare mare, sarcina capacitiva a lui T2 micsorandu-se, ceea ce mareste viteza de tranzitie a tensiunii in colectorul lui T2; de asemenea are o rezistenta de iesire mai mica decat rezistenta de iesire a circuitului standard si, prin urmare, creste viteza de raspuns a portii deoarece in cazul rezistentei de iesire mai mici orice capacitate care sunteaza iesirea poate fi incarcata mai rapid. Se poate observa de asemenea ca tranzistorul T4 nu se satureaza niciodata deoarece jonctiunea s-a C-B nu poate fi polarizata direct intrucat VCE a tranzistorului T6 care conduce (eventual la saturatie) este totdeauna pozitiva.

Figura 4.16. Poarta SI-NU HTTL.

O scadere mai mare a timpilor de propagare printr-o poarta logica se poate realiza prin doua solutii:

1. Reducerea duratei de viata a purtatorilor minoritari. Se obtine in general prin doparea siliciului cu aur.

Evitarea saturarii tranzistoarelor

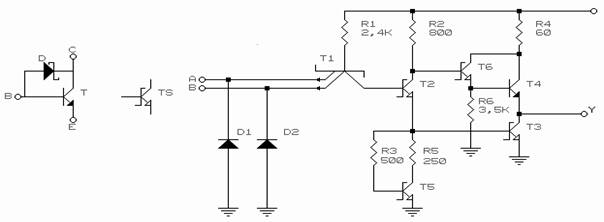

Aceste circuite au aceeasi schema ca si circuitele TTL rapide, dar folosesc tranzistoare nesaturate (figura 4.17.b). Evitarea intrarii in saturatie se face folosind o dioda Schottky conectata in paralel pe jonctiunea baza-colector a tranzistorului. (figura 4.17.a) Dioda Schottky se obtine prin realizarea unui contact metal - semiconductor (Al si Si de tip n). Avantajul diodei Schottky consta in aceea ca nu stocheaza sarcini in jonctiune (timpul de stocare are valoare redusa ts<1 ns) si are o tensiune de deschidere de 0,3-0,4 V mai mica decat jonctiunea tranzistorului care este 0,6 V, impiedicand saturarea acestuia.

s

Figura 4.17. a) Tranzistorul Schottky. b) Poarta SI-NU TTL Schottky.

Prin intrare in conductie a diodei colectorul tranzistorului nu va avea niciodata un potential suficient pentru polarizarea directa a jonctiunii colector-baza. Se obtine astfel o micsorare a timpului de propagare (tpd=3 ns) prin micsorarea timpului de stocare la o putere disipata medie de 20 mW pe poarta.

Varianta de porti TTL Schottky de mica putere (LPSTTL) are aceeasi structura, dar curentii prin tranzistoare sunt mai mici, efect care se obtine prin marirea valorilor rezistentelor. Timpii de comutatie cresc insa fata de valoarea normala. Se foloseste in special in montaje mixte care cuprind atat circuite logice TTL cat si circuite din familia MOS sau CMOS.

Majoritatea portilor TTL folosite astazi sunt din familia Schottky sau una din subfamiliile acesteia. Circuitele din familia Schottky contin litera S in indicativ ca de exemplu 74Sxx, iar cele de mica putere literele LS, 74LSxx. Alte tipuri de circuite TTL Schottky sunt cele din seria AS (advanced Schottky), ALS (advanced low - power Schottky), si F (fast Schottky). Parametrii circuitelor Scottky sunt prezentati in tabelul urmator, alaturi de parametrii seriei TTL standard inclusa pentru comparatie.

|

Parametrii |

Seria |

|||||

|

74S |

74LS |

74AS |

74ALS |

74F |

||

|

VOHmin |

2,4 V |

2,7 V |

2,7 V |

2,7 V |

2,7 V |

2,7 V |

|

VOLmax |

0,4 V |

0,5 V |

0,5 V |

0,5 V |

0,5 V |

0,5 V |

|

VIHmin |

2,0 V |

2,0 V |

2,0 V |

2,0 V |

2,0 V |

2,0 V |

|

VILmax |

0,8 V |

0,8 V |

0,8 V |

0,8 V |

0,8 V |

0,8 V |

|

IOHmin |

- 0,4 mA |

- 1,0 mA |

- 0,4 mA |

-2,0 mA |

- 0,4 mA |

- 1,0 mA |

|

IOLmin |

16 mA |

20 mA |

8 mA |

20 mA |

4 mA |

20 mA |

|

IIHmax |

40 µA |

50 µA |

20 µA |

20 µA |

20 µA |

20 µA |

|

IILmax |

- 1,6 mA |

-2,0 mA |

- 0,4 mA |

- 0,6 mA |

- 0,2 mA |

- 0,6 mA |

|

tp |

10 ns |

3 ns |

10 ns |

1,5 ns |

4 ns |

2,5 ns |

|

Pd |

10 mW |

20 mW |

2 mW |

20 mW |

1 mW |

4 mW |

Doua sau mai multe porti SI-NU in structura obisnuita nu pot avea iesirile cuplate in paralel. Presupunem doua asemenea porti a caror iesiri sunt cuplate in paralel (figura 4.18).

Figura 4.18. Studiul a doua iesiri TTL cuplate in paralel

Daca ambele iesiri sunt simultan la '0' sau simultan la '1', circuitul functioneaza corect. In cazul in care o iesire se afla la '0' si alta la '1' tranzistorul T4' al circuitului cu iesire in '1' logic este legat la masa prin tranzistorul T3 al circuitului cu iesirea in '0' logic fiind parcurs astfel de un curent mare (cca. 40 mA) limitat numai de dioda si rezistenta mica de 130 W, un asemenea regim se mentine pana cand nivelele logice se schimba. Aceasta atrage dupa sine cresterea puterii absorbite de la sursa de alimentare si, ceea ce e mai important, disiparea unei puteri excesiv de mari in tranzistoarele T3 si T4' si in rezistenta de 130 W. Drept consecinta, parametrii portii se modifica (daca tranzistoarele nu se distrug prin ambalare termica) pierzandu-se imunitatea la zgomot, deoarece, pentru un asemenea curent (40 mA), potentialul colectorului lui T3 din stanga e mai mare de 0,4, iar al celui din dreapta e mai mic decat 2,4 V garantati alterandu-se astfel, nivelele logice '0' si '1'.

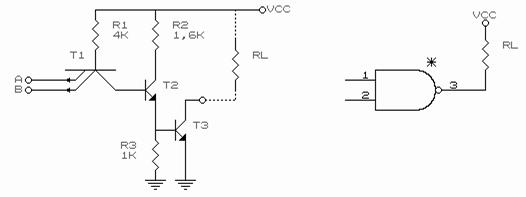

Pentru a cupla totusi in paralel mai multe porti se utilizeaza circuite cu colectorul in gol (figura 4.19).

a) Schema circuitului b) Simbolul circuitului

Figura 4.19. Circuitul TTL cu colectorul in gol.

O asemenea poarta este identica cu poarta TTL standard din care lipseste insa repetorul pe emitor din etajul in contratimp (T4 si D) care este inlocuit de o rezistenta de sarcina RL a carei valoare se calculeaza din urmatoarele considerente:

-RLmax se determina din conditia ca V0H 2,4 V;

-RLmin se determina din conditia ca V0L 0,4 V.

Aceste valori se obtin tinand cont de curentii debitati, de portile conectate in paralel si de curentii absorbiti de portile comandate si sunt:

unde m reprezinta numarul de porti ale caror iesiri sunt cuplate in paralel, iar N numarul intrarilor comandate. Se au in vedere urmatoarele valori: VCC=5 V, IOHmax=800 mA, IOLmax=16 mA, IILmax=1,6 mA, IIHmax=40 mA, VOLmax=0,4 V, VOHmin=2,4 V. Se constata ca valoarea minima a rezistentei RL nu depinde de numarul portilor cuplate in paralel.

In practica se alege o valoare pentru RL cuprinsa intre cele doua valori calculate. In cataloage se dau tabele de dimensionare functie de numarul m al iesirilor cuplate in paralel si numarul N de porti comandate.

a) b)

Figura 4.20 Implementarea functiei logice SI cu: operatori SI-NU (a), SI - cablat (b).

Operatia de interconectare a iesirilor mai multor circuite cu colectorul in gol este denumita in literatura de specialitate sub numele de cablare, iar functia logica realizata SI-cablat. Cablarea iesirilor portilor cu colectorul in gol, in vederea obtinerii functiei SI, (figura 4.20) este mai avantajoasa decat realizarea aceleiasi operatii cu operatori SI-NU obisnuiti, deoarece se economisesc doua nivele de logica si in consecinta se reduce timpul de propagare.

Pentru sistemele actuale de calcul digital ce utilizeaza magistrale comune de date, la care sunt cuplate atat receptoare cat si mai multe surse de semnal numeric, au fost concepute in cadrul familiei de circuite logice TTL circuite specializate denumite porti cu trei stari sau TSL (Tri-State-Logic).

Acestea

au avantajul fata de portile cu colectorul in gol ca

pastreaza toate performantele circuitelor TTL obisnuite

avand etaj de iesire in contratimp. Schema circuitului TSL este data

in figura 4.21. Circuitul este prevazut cu o borna suplimentara

de comanda INHIBITIE (I). Daca intrarea ![]() este pe '1'

logic tranzistorul T5 si dioda d sunt blocate. Circuitul

functioneaza ca un inversor obisnuit fata de intrarea

A. Daca nivelul semnalului pe

este pe '1'

logic tranzistorul T5 si dioda d sunt blocate. Circuitul

functioneaza ca un inversor obisnuit fata de intrarea

A. Daca nivelul semnalului pe ![]() devine '0'

logic T5 conduce la saturatie, se deschide jonctiunea

baza-emitor a lui T1, iar T2 si T3

sunt blocati. Curentul ce trece in aceasta situatie prin R2

spre baza lui T4 este deviat prin dioda d deschisa. Tensiunea

din anodul diodei d aproximativ 0,9 V este insuficienta pentru deschiderea

tranzistorului T4 care prin urmare este blocat. Cum si

tranzistorul T3 este blocat, indiferent de valoarea variabilei

logice de la intrarea A circuitul se comporta la iesire ca o

impedanta mare. Aceasta stare se numeste stare de

impedanta mare, HiZ (High Z) sau stare izolata.

devine '0'

logic T5 conduce la saturatie, se deschide jonctiunea

baza-emitor a lui T1, iar T2 si T3

sunt blocati. Curentul ce trece in aceasta situatie prin R2

spre baza lui T4 este deviat prin dioda d deschisa. Tensiunea

din anodul diodei d aproximativ 0,9 V este insuficienta pentru deschiderea

tranzistorului T4 care prin urmare este blocat. Cum si

tranzistorul T3 este blocat, indiferent de valoarea variabilei

logice de la intrarea A circuitul se comporta la iesire ca o

impedanta mare. Aceasta stare se numeste stare de

impedanta mare, HiZ (High Z) sau stare izolata.

a) b)

Figura 4.21. Circuite logice cu trei stari (TSL) : schema interna (a); simbolul (b)

Tabelul de adevar al inversorului TSL este prezentat in continuare:

|

|

I |

Y |

|

0 |

1 |

1 |

|

1 |

1 |

0 |

|

X |

0 |

HiZ |

|

Politica de confidentialitate |

| Copyright ©

2026 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |