Tehnologia de realizare a circuitelor integrate cu tranzistoare MOS ofera o serie de avantaje:

un numar mai redus de operatii tehnologice;

densitate de integrare mai mare (de pana la 15 ori mai mare) decat circuitele logice cu tranzistoare bipolare;

consum redus de putere;

pragul de zgomot mai ridicat datorita tensiunilor mari de alimentare

Datorita utilizarii exclusive a tranzistoarelor (nu si a rezistentelor) procesul tehnologic de realizare a acestor circuite are de trei ori mai putine operatii principale deci si un pret de cost mai redus.

In trecut, circuitele din aceste familii prezentau dezavantajul unui timp de propagare mai mare ca si circuitele TTL (aproximativ de 10 ori mai mare), si un curent de iesire mai mic. Astazi aceste dezavantaje au disparut astfel incat anumite subfamilii sunt egale sau chiar superioare cu familia TTL si la acesti parametrii.

Familiile de circuite logice cu TEC-MOS se realizeaza exclusiv cu tranzistoare cu canal p sau canal n (familiile PMOS si NMOS), fie cu tranzistoare de ambele tipuri (familia CMOS). Aceste familii se deosebesc atat din punct de vedere al parametrilor cat si al tehnologiei de fabricatie, deci implicit al costului acestora. Circuitele de tip PMOS au procesul de fabricatie cel mai simplu, dar viteza de comutatie cea mai scazuta, datorita mobilitatii mai mici a purtatorilor mobili (golurile). Circuitele de tip NMOS au un proces de fabricatie mai complicat, dar mobilitatea marita a purtatorilor mobili (electronii) le asigura o viteza de comutatie mai ridicata. Circuitele CMOS au viteza de comutatie medie, dar permit realizarea unei structuri de circuit care nu consuma energie de la sursele de alimentare in nici una dintre starile stabile, consumul de curent aparand numai in timpul tranzitiei dintr-o stare in alta. Tranzistoarele TEC-MOS au simbolul si caracteristica din figura 4.22.

|

|

|

|

|

|

Simbol |

Caracteristica |

Comutator inchis |

Comutator deschis |

|

a) cu canal n indus |

|||

|

|

|

|

|

|

Simbol |

Caracteristica |

Comutator inchis |

Comutator deschis |

|

b) cu canal p indus |

|||

Figura 4.22. Simbolul si caracteristicile tranzistoarelor TEC-MOS

Un tranzistor MOS poate fi echivalat cu un comutator comandat in tensiune. Daca tensiunea VGS este mai mica in valoare absoluta decat tensiunea de prag a tranzistorului VT rezistenta drena-sursa rds este practic infinita, comutatorul MOS fiind deschis. Atunci cand ˝VGS˝>VT se formeaza un canal conductor intre drena si sursa tranzistorului, rds este foarte mica, iar comutatorul MOS inchis. Polaritatea tensiunii de prag este pozitiva pentru tranzistoarele cu canal n si negativa pentru tranzistoarele cu canal p si are valori tipice cuprinse intre 1 si 4 volti. In aceasta familie logica se foloseste ca rezistenta de sarcina (de cateva zeci de kW) tot un tranzistor MOS.

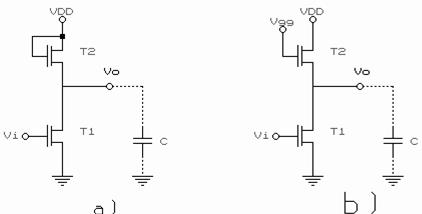

Schema de principiu a inversorului MOS static este prezentata in figura 4.23 a) cu tranzistor de sarcina saturat; b) cu tranzistor de sarcina nesaturat.

b) a)

Figura 4.23. Poarta logica NMOS statica

Aceste circuite constau exclusiv din tranzistoare TEC-MOS cu canal n folosindu-se ambele tipuri, cu canal initial si cu imbogatire. Ele functioneaza alimentate la o singura sursa de tensiune pozitiva care poate lua valori cuprinse intre 5 si 15 V. Nivelele logice depind de tensiunea de alimentare folosita; pentru alimentare la +5 V sunt compatibile cu nivelele logice TTL. Tranzistorul T1 este un TEC-MOS cu canal n cu imbogatire deoarece este comod ca el sa fie blocat cand tensiunea pe poarta sa este zero. El conduce in regim static in regiunea de trioda (unde rezistenta dispozitivului este functie de tensiune). Circuitul reprezinta un etaj de amplificare cu T1 in care T2 functioneaza ca o sarcina activa inlocuind o rezistenta fixa. Sarcina externa a acestui inversor este in general constituita tot din intrari in NMOS deci are un caracter capacitiv si a fost reprezentata prin C. Folosirea lui T2 ca rezistenta de sarcina este o solutie avantajoasa intrucat permite realizarea unei rezistente de valoare mare pe o suprafata relativ mica.

Diferenta intre solutiile a) sau b) din figura 4.23 este data de regimul de functionare al tranzistorului T2. In cazul solutiei a), T2 functioneaza in regim de saturatie a caracteristicilor, in solutia b) punctul de functionare a tranzistorului este plasat in regiunea nesaturata. Avantajul solutiei a) este utilizarea unei singure surse de alimentare in schimb caracteristica de transfer este mai putin abrupta ca la solutia b) (figura 4.24), iar tensiunea de iesire este VOH=VDD-VT fata de VOH=VDD la solutia b).

|

|

|

|

Figura 4.24. Caracteristica de transfer |

Figura 4.25. Raspunsul inversorului la un semnal impuls |

Pentru explicarea functionarii se considera ca inversorul este comandat de un circuit identic cu el insusi. Cand tensiunea de intrare VI=VDD-VT2 (unde VT2 este tensiunea de prag la care se deschide tranzistorul T2) tranzistorul T1 intra in conductie si se obtine la iesire VO=VOL='0'. Daca la intrarea inversorului se aplica VIL='0', T1 este blocat si se obtine la iesire VOH=VDD-VT='1' S-a demonstrat ca circuitul realizeaza functia de negare. Daca consumul de putere a inversorului este practic nul, in cazul in care VO=VOH, el poate atinge valori importante atunci cand tranzistorul T1 este deschis: VO=VOL=0 V. Pentru a limita puterea consumata, se stabilesc prin proiectare valori mari pentru rezistentele in conductie a tranzistoarelor, rds. Nivelul tensiunii VOL este fixat de raportul rezistentelor in conductie ale lui T1 si T2.

![]()

Deoarece se urmareste ca VOL 0 V, este necesar ca rds1<<rds2. De aici rezulta o diferenta importanta intre cei doi timpi de propagare a inversorului, tpHL si tpLH, constantele de timp ale iesirii fiind proportionale cu valorile celor doua rezistente. Desi tranzistorul MOS intrinsec comuta rapid ( 1 ns) viteza de comutare se reduce cu cca. 3 ordine de marime din cauza capacitatii C ( 5 pF). Frontul pozitiv este mai mare deoarece rezistenta oferita de T2 pentru incarcarea condensatorului este mai mare decat cea oferita de T1 pentru descarcarea lui C (figura 4.25).

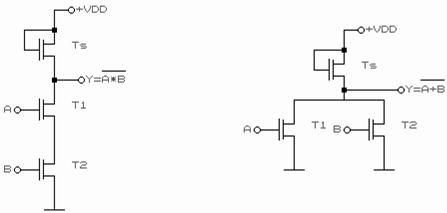

Poarte SI-NU NMOS are configuratia din figura 4.26. Cand VIA sau/si VIB = '0' rezulta ca tranzistorul T1 si/sau T2 sunt blocate astfel ca tensiunea de iesire este VO=VDD='1'. Daca VIA=VIB='1' atunci ambele tranzistoare conduc si iesirea este in '0'. Tensiunea de iesire este suma tensiunilor de-a lungul tranzistoarelor T1 si T2 si trebuie sa fie sub tensiunea de prag pentru un tranzistor in conductie. Pentru a micsora caderea de tensiune pe cele doua tranzistoare se creste (dubleaza) latimea canalului.

|

Figura 4.26. Poarta SI-NU NMOS |

Figura 4.27. Poarta SAU-NU NMOS |

Pentru VIA sau VIB ='1' tranzistorul corespunzator este deschis si la iesire se obtine '0'. Daca VIA=VIB='0' ambele tranzistoare sunt blocate si iesirea este in '1'. Se poate observa ca valoarea tensiunii de iesire corespunzatoare lui '0' este mai mica decat la poarta SI-NU fiind egala doar cu tensiunea de iesire a unui tranzistor saturat. De aceea poarta fundamentala a familiei MOS este poarta SAU-NU. Prin interconectarea lor cu circuite inversoare se pot realiza si functii mai complexe.

Circuitele MOS statice (studiate pana in prezent) sunt circuitele prin care informatia logica se propaga neconditionat de un semnal extern. In circuitele MOS dinamice un semnal de ceas conditioneaza propagarea informatiei logice prin ele.

|

|

|

|

|

a) Schema inversorului |

b) Forme de unda |

|

|

Figura 4.28. Inversorul MOS dinamic cu doua impulsuri de tact. |

||

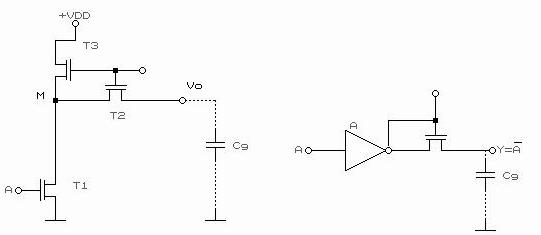

Inversorul MOS dinamic prezentat in figura 4.28 are un consum considerabil redus fata de inversorul MOS static. Circuitul este actionat prin intermediul a doua semnale de tact F si F principiul de functionare fiind bazat pe incarcarea si descarcarea capacitatii de grila CG a intrarii urmatorului operator logic. In momentul in care actioneaza tactul F , se produce incarcarea capacitatii CG prin Ts deschis la valoarea VDD, T2 fiind blocat nu apare curgere de curent spre masa. Cand F revine la masa semnalul F pune in conductie tranzistorul T2. Astfel in functie de nivelul tensiunii de intrare se stabileste regimul de functionare al lui T1, deci CG ramane incarcat la VDD daca T1 este blocat sau se descarca rapid daca T1 este deschis. Deci semnalul de iesire a inversorului se obtine numai dupa aplicarea tactului F . Frecventa impulsurilor F si F nu poate fi mai mica decat o valoare minima impusa de curentii reziduali din circuit ce determina descarcarea capacitatii CG si pierderea informatiei utile.

De asemenea pentru formarea secventei corecte a semnalelor F si F circuitul necesita montaje de comanda auxiliare. Cu toate aceste dezavantaje multe circuite LSI-MOS sunt dinamice: microprocesoare, memorii RAM, registre de deplasare.

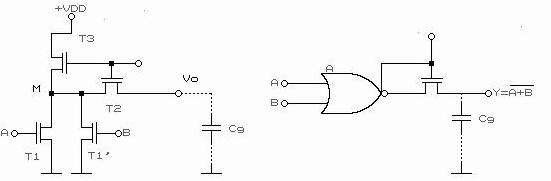

Inversorul, portile SI-NU si SAU-NU dinamice cu un singur impuls de control sunt prezentate in figura 4.29.

Pentru aceste circuite tranzistoarele de sarcina sunt alimentate numai la aplicarea impulsului de tact. In acest fel ele consuma mai putina energie decat circuitele statice. Daca F='0' (figura 4.29.a) T2 si T3 sunt blocate si VM=0. Cand F='1', T2 si T3 conduc si V0=VM, astfel ca daca VA = 0 T1 este blocat si VM='1', iar daca VA='1', T1 conduce si VM=0.

F F

a) Inversorul NMOS dinamic

F F

b) Poarta SI-NU NMOS dinamica

F F

c) Poarta SAU-NU NMOS dinamica

Figura 4.29. Porti NMOS dinamice

Este familia cu parametrii cei mai apropiati de aceea ai unei familii ideale care ar trebui sa aiba: consum zero in regim static, timp de propagare egal cu zero, fronturi controlabile, imunitate la zgomot egala cu 50% din diferenta dintre tensiunile corespunzatoare nivelelor logice.

Circuitele CMOS incorporeaza pe un sigur substrat semiconductor atat tranzistoare MOS cu canal n cat si tranzistoare MOS cu canal p. Familia CMOS a atins o diversitate comparabila cu cea a circuitelor TTL si datorita performantelor superioare le-a inlocuit in multe aplicatii.

Avantajele circuitelor MOS sunt:

- consum static de putere de valoare extrem de scazuta, de 10 nW pe poarta (datorita curentilor reziduali);

- tensiunea de alimentare poate varia intr-un domeniu larg: + (3-15) V;

- procesul tehnologic desi mai complex decat la circuitele MOS (n sau p) este mult mai simplu decat cel de la fabricarea circuitelor cu tranzistoare bipolare. In consecinta circuitele CMOS sunt mai ieftine decat circuitele TTL.

Dezavantajele circuitelor CMOS sunt :

- consumul de putere in regim dinamic creste rapid cu marirea frecventei, fiind intre 1 si 10 mW la frecventa de 1 MHz, ea depinde de tensiunea de alimentare si de sarcina;

- timpii de propagare desi la familiile mai vechi erau mai mari ca la circuitele TTL (intre 20 si 50 ns) la ora actuala exista familii care egaleaza sau chiar intrec si la acest parametru performantele familiei TTL.

Daca evaluam performantele familiilor logice prin produsul putere disipata-timp de propagare (factor de calitate) se constata ca factorul de calitate al circuitelor CMOS este cu aproape doua ordine de marime mai mic decat cel al circuitelor TTL.

Familia de circuite CMOS cuprinde mai multe serii logice distincte. Seriile CD40XX si 54/74CXX sunt perfect compatibile intre ele. Circuitele din seria 54/74CXX sunt compatibile cu circuitele din familia TTL fiind echivalente functional si ca dispunere a terminalelor cu circuitele TTL din seria 74XX. In cazul in care sunt alimentate la +5 V circuitele din seria 54/74CXX pot comanda direct doua unitati de sarcina TTL din seria de putere redusa 54/74LXX. Cresterea tensiunii de alimentare duce la cresterea vitezei de lucru dar si la cresterea puterii disipate in regim dinamic. Seria de circuite CMOS rapide are indicativul HC iar seria de consum redus indicativul AC.

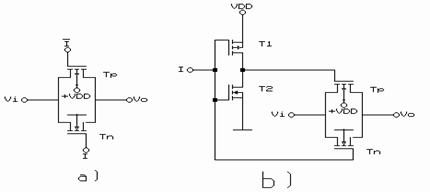

Operatorul fundamental CMOS este circuitul inversor cu schema din figura 4.30:

V0 VI![]()

![]()

![]()

![]()

Figura 4.30. Inversorul CMOS.

Daca la intrare se aplica nivelul de tensiune VI = VDD, T1 va intra in conductie fixand V0 0 V. Daca intrarea se pune la masa, VI =0 V rezulta ca pe grila tranzistorului T2 se afla o tensiune egala cu -VDD fata de sursa lui, ce duce la deschiderea lui, nivelul tensiunii de iesire devenind V0 VDD. Se observa ca in permanenta un tranzistor este blocat si unul conduce ceea ce duce la un consum mic de putere. Circuitul consuma putere in cursul comutarii cand exista un anumit interval de timp in care ambele tranzistoare conduc si curentul se inchide prin ele intre plusul sursei de alimentare si masa. Puterea consumata este direct proportionala cu frecventa semnalului. Un avantaj important al circuitelor CMOS este acela ca indiferent de nivelul tensiunii de iesire exista o cale de rezistenta scazuta, determinata de tranzistorul care se afla in conductie, pentru incarcarea si descarcarea sarcinilor capacitive.

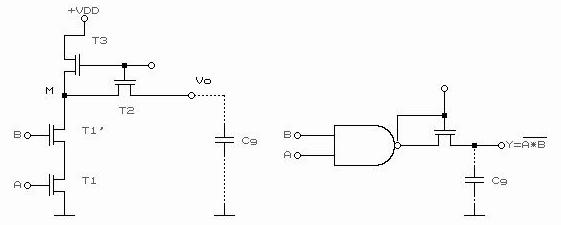

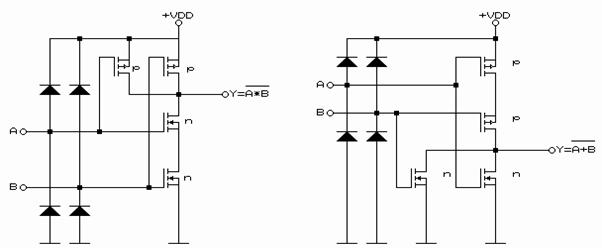

Poarta SI-NU din familia CMOS (figura 4.31.a) se formeaza dintr-o combinatie serie-paralel de tranzistoare MOS-p si MOS-n. Tensiunea de iesire are valoarea VH pentru toate combinatiile de intrare care determina conductia cel putin a unui tranzistor MOS-p. Se obtine un nivel coborat de tensiune cand prin aplicarea la toate intrarile a tensiunii VH tranzistoarele MOS-p sunt blocate si cele MOS-n in conductie. Poarta logica SAU-NU (figura4.31.b) difera de poarta SI-NU prin schimbarea configuratiei etajului, adica prin inversarea rolurilor intre tranzistoarele MOS-p si MOS-n. Tensiunea de iesire are valoarea VH VDD numai daca toate intrarile sunt la nivel logic scazut, determinand blocarea tranzistoarelor MOS-n si intrarea in conductie a tranzistoarelor MOS-p.

Figura 4.31. a) Poarta SI-NU CMOS; b) Poarta SAU-NU CMOS.

Portile SAU-NU respectiv SI-NU din familia logica MOS (MOS-n sau MOS-p) contin n+1 tranzistoare pentru n intrari, in timp ce operatorul echivalent CMOS contine un numar de 2n tranzistoare pentru n intrari. Diodele au rol de protectie a tranzistoarelor, impiedicand aplicarea pe intrari a unor tensiuni negative si a unor tensiuni pozitive mai mari ca tensiunea de alimentare. Portile MOS prezinta impedante medii la iesire (1 kW), de aceea la cuplarea in paralel a mai multor iesiri pot aparea curenti mari. Un circuit care realizeaza impedanta mare de iesire este poarta de transmisie CMOS (figura 4.32.a).

|

I |

V0 |

|

HiZ |

|

|

VI |

b) a)

Figura 4.32. Poarta de transmisie CMOS.

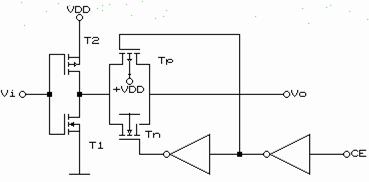

Aceste circuite sunt special concepute pentru a fi utilizate drept comutatoare comandate in tensiune. Valoarea rezistentei drena-sursa a unui tranzistor MOS variaza cu mai mult de sase ordine de marime la trecerea din starea blocata in starea de conductie (rDS(on)=0,2kW ). Este format in esenta din doua tranzistoare MOS unul cu canal p si unul cu canal n puse in paralel si comandate cu impulsuri in antifaza, obtinute cu un inversor (figura 4.32.b). Acest circuit este foarte util atat pentru prelucrarea semnalelor analogice, fiind folosit drept comutator analogic, cat si ca element component la realizarea circuitelor logice, de exemplu pentru obtinerea iesirilor cu trei stari, ca in figura 4.33, pentru un inversor. Daca CE=1 poarta este deschisa si iesirea V0 reproduce semnalul de la iesirea inversorului V0'. Daca CE=0 poarta de transmisie este blocata si circuitul prezinta impedanta mare de iesire (HiZ).

Figura 4.33. Iesire cu trei stari realizata cu poarta de transmisie CMOS.

Tensiunea de alimentare pentru circuitele CMOS este cuprinsa intre + 3 si +15 V dar cele mai folosite sunt valori sunt + 5V si + 3,3 V.

Nivelele logice Valorile nivelelor logice pentru tensiunea de alimentare de + 5V pentru un circuit CMOS sunt:

|

+ 5 V CMOS |

+ 3,3 V CMOS (LV-CMOS) |

|

|

VIL max |

1,5 V |

0,8 V |

|

VIH min |

3,5 V |

2 V |

|

V0L max |

0,33 V |

0,4 V |

|

V0H min |

4,4 V |

2,4 V |

Marginea de zgomot pentru circuitele CMOS alimentate cu + 5V este:

ML VIL max - V0L max 1,17 V

MH V0H min - VIH min 0,9 V

In acest fel pentru portile CMOS standard marginea de zgomot de c.c. este mai mare ca la circuitele TTL care are valoarea de 0,4 V pentru ambele nivele logice. Zona cuprinsa intre tensiunea de intrare in starea low maxima si tensiunea de intrare in starea high minima adica pentru circuitele alimentate la + 5 V intre VIH min = 3,5 V si VIL max 1,5 V, respectiv pentru circuitele alimentate la + 3,3 V intre VIH min = 2 V si VIL max 0,8 V, este o interzisa deoarece un semnal de intrare cu valoarea cuprinsa intre aceste limite genereaza un raspuns nepredictibil.

Puterea disipata. In timp ce la circuitele TTL puterea disipata este aproximativ constanta in domeniul frecventelor de lucru, in cazul circuitelor CMOS este dependenta de frecventa. In regim static puterea disipata este extrem de scazuta si de exemplu pentru un circuit HCMOS este 2,75 µW dar creste puternic cu frecventa astfel incat la 100 Hz este de 170 µW pentru acelasi tip de circuit.

Circuitele CMOS se pot distruge in timpul manipularii datorita descarcarilor electrostatice. De aceea ele trebuiesc manipulate cu grija tinand cont de cateva recomandari:

Toate circuitele CMOS se transporta in invelisuri conductoare pentru a prevenii incarcarea electrostatica. Cand se scot din ambalaj, pinii nu trebuie atinsi.

Dispozitivul trebuie plasat cu pinii pe o suprafata metalica. Este interzisa plasarea pe o suprafata de polistiren sau pungi de plastic.

Toate sculele, echipamentele de testare si masa de lucru trebuiesc sa fie legate la priza de masa. Persoana care lucreaza cu dispozitivul CMOS trebuie sa aiba o bratara metalica legata la masa prin intermediul unei rezistente de valoare mare (care previne socurile care pot aparea la contactul cu o sursa de tensiune).

Dispozitivele CMOS se introduc in socluri numai cu alimentarea oprita.

Toate intrarile nefolosite trebuiesc conectate la plusul sursei de alimentare in cazul portilor SI (SI-NU) sau la masa in cazul portilor SAU (SAU-NU).

Dupa montarea pe un cablaj pentru pastrare sau transport acesta trebuie protejat prin acoperirea conectorilor cu un invelis conductor.

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |