Microcontrolerul AT89C52

1. Caracteristici

Compatibilitate cu produse de tip MCS-51

8k biti ai sistemului reprogramabil a memoriei FLASH

Durata de viata: 1.000 scriere / cicluri de stergere

Intreaga operatie statica: de la 0 Hz la 24 MHz

3 nivele de inchidere a programului de memorie

256 x 8 biti RAM intern

32 linii I/O programabile

3 temporizatoare / numaratoare pe 16 biti

8 surse de intrerupere

canal serial programabil

modul de lucru de joasa putere si modul IDLE

2. Descriere

AT89C52 este un microcontroler de inalta performanta in tehnologie CMOS, pe 8 biti, de putere joasa cu 8k octeti de memorie FLASH. Memorie FLASH este o memorie de tip EEPROM cu timp de scriere foarte scurt, tensiune de stergere de valoare redusa, capacitate mare si cost rezonabil, putand fi folosita in locul unei dischete.

Dispozitivul este fabricat folosind tehnologia ATMEL de inalta densitate a memoriei nevolatile si este compatibil cu standardul 80C51 si 80C52 in ceea ce priveste instructiunile si configurarea pinilor. Memoria de tip FLASH permite memoriei de program sa fie reprogramata in sistem sau printr-o programare a memoriei nevolatile conventionale. Combinand un dispozitiv CPU pe 8 biti care are calitatea de a indeplini mai multe functii, cu o memorie de tip FLASH intr-un cip monolitic, ATMEL AT89C52 este un microcontroler puternic care ofera solutii de mare flexibilitate multor aplicatii de control traditionale.

3. Configuratia Pinilor

Fig.2.1 Configurarea pinilor.

4. Schema bloc a microcontrolerului

Fig.2.2. Schema bloc a microcontrolerului.

AT89C52 prevede urmatoarele caracteristici: 8 ko de memorie FLASH, 256 octeti de memorie RAM, 32 linii I/O, trei temporizatoare/ numaratoare de 16 biti, o arhitectura cu 6 vectori pe doua nivele de intrerupere, un port serial full-duplex, un oscilator si un ceas intern. In plus microcontrolerul AT89C52 este proiectat cu o logica statica pentru operare cu o frecventa redusa pana la 0Hz si ofera doua software-uri selectabile pentru economisirea puterii. Modul IDLE opreste CPU-ul permitand RAM-ului, temporizatoarelor/numaratoarelor, portului serial si sistemului de intrerupere sa-si continue functionarea. Modul de scoatere de sub tensiune opreste oscilatorul, facand imposibila utilizarea celorlalte functii ale cip-ului pana cand apare o noua reinitializare (reset) a hardware-ului.

5. Descrierea pinilor

VCC-tensiune de alimentare

GND-masa

Portul 0 este un port pe 8 biti de intrare/iesire bidirectional. Functionand ca si port de iesire, fiecare pin poate absorbi curent de la opt intrari TTL. Cand 1 logic este inscris la portul 0 pinii pot fi folositi ca si intrari de inalta impedanta. Portul 0 poate de asemenea fi configurat sa fuctioneze ca un multiplexor intre octetul inferior de adrese si un octet de date in timpul accesului la programul exterior si la memoria de date externa. In acest scop, portul 0 este prevazut cu rezistente de pull-up. De asemenea primeste octetul de cod in timpul programarii FLASH si elibereaza octetul de cod in timpul verificarii programului. Sunt necesare rezistente externe de pull-up in timpul verificarii programului.

Portul 1 este un port de intrare/iesire bidirectional, pe 8 biti cu rezistente interne de pull-up. Buffer-ele de iesire ale portului 1 pot alimenta patru intrari TTL. Cand se inscrie 1 logic la pinii portului 1, ei sunt pusi in starea high (1 logic) datorita rezistentelor interne si pot fi utilizati ca si intrari. Ca intrari, pinii portului 1 care au fost pusi pe low din exterior vor produce un curent datorita rezistentelor interne. In plus, P1.0 si P1.1 pot fi configurate sa fie a doua componenta de intrare externa temporizator/numarator (P1.0/T2) si respectiv a doua intrare declansatoare temporizator/numarator (P1.1/T2EX), dupa cum se observa din urmatorul tabel. De asemenea portul 1 primeste octetul cel mai putin semnificativ de adresa in timpul programarii FLASH si a verificarii.

|

Portul pin |

Functionari alternative |

|

P1.0 |

T2(intrare externa a temporizatorului/ numaratorului |

|

P1.1 |

T2EX (temporitator/numarator 2 - declansator de captare/transmitere si control a directiei |

Portul 2 - este un port bidirectional intrare/iesire de 8 biti cu rezistente interne de pull-up. Buffer-ele de iesire ale portului 2 pot receptiona/furniza curent pentru patru intrari TTL. Cand primul este scris de pinii portului 2, ei sunt pusi in starea high de dispozitivele de tranzitie ascendenta interne si pot fi utilizate ca si intrari. Ca intrari, pinii portului 2 care din exterior au fost pusi in starea low, vor furniza curentul (Iil) datorita dispozitivelor de tranzitie ascendenta interne. Portului 2 emite adresele bitilor high in timpul citirii din memoria externa de program si in timpul accesului la datele din memoria externa care utilizeaza 16 biti de adrese (MOVX @DPTR). In timpul accesului la memoria externa de date care utilizeaza 8 biti de adrese (MOVX @RI), portul 2 emite continutul registrului special de functionare al pinului P2. Portul 2 de asemenea primeste adrese ale bitilor high si anumite semnale de verificare in timpul programarii si verificarii memoriei de tip FLASH.

Portul 3 este un port bidirectional de intrare/iesire cu rezistente de pull-up interne. Buffer-ele de iesire ale portului 3 pot receptiona/furniza patru intrari TTL. Cand 1 logic este inscris la pinii portului 3, ei sunt pusi in starea high de catre rezistentele interne de pull-up si pot fi utilizati ca intrari. Ca intrari, pinii portului 3 care au fost pusi din exterior in starea low, vor furniza un curentul (IIL) datorita rezistentelor de pull-up interne. De asemenea, portul 3 serveste la functii speciale ale microcontrolerului AT89C51, dupa cum se poate observa in urmatorul tabel.

De asemenea, portul 3 primeste anumite semnale de control pentru programarea FLASH si pentru verificare.

Tabel 2.2

|

Pinul potului |

Functia alternativa |

|

P3.0 |

RXD - intrare seriala a portului pentru receptie |

|

P3.1 |

TXD - iesire seriala a portului pentru transmisie |

|

P3.2 |

INT0 - intrerupere externa pentru Timer 0 |

|

P3.3 |

INT1 - intrerupere externa pentru Timer 1 |

|

P3.4 |

T0 - intrare externa in Timer 0 |

|

P3.5 |

T1 - intrare externa in Timer 1 |

|

P3.6 |

|

|

P3.7 |

|

6. RESET

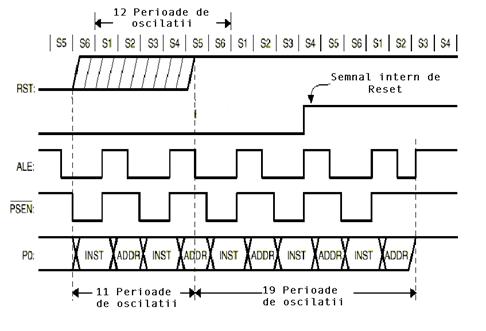

Intrarea de reset a microcontrolerului AT89C52 este pinul RST, care este intrarea intr-un Trigger Schmitt.

Reset-ul se realizeaza tinand pinul RST pe "1" logic pe perioada a cel putin doi ciclii-masina (24 de perioade de oscilator), in timp ce oscilatorul functioneaza. CPU va raspunde printr-un reset intern. De asemenea, CPU va configura pinii cvasi-bidirectionali ALE si PSEN ca pini de intrare.

Reset-ul intern este executat in timpul celui de-al doilea ciclu masina, cand RESET este in "1" logic si va fi repetat la fiecare ciclu masina pana cand RST trece in "0" logic.

RAM-ul intern nu este afectat de reset. Cand apare tensiune pe +Vcc continutul RAM-ului este nedeterminat, cu exceptia cazului in care se foloseste modul de operare cu putere redusa.

7. Timpul de Reset

Fig.2.3.Timp de Reset

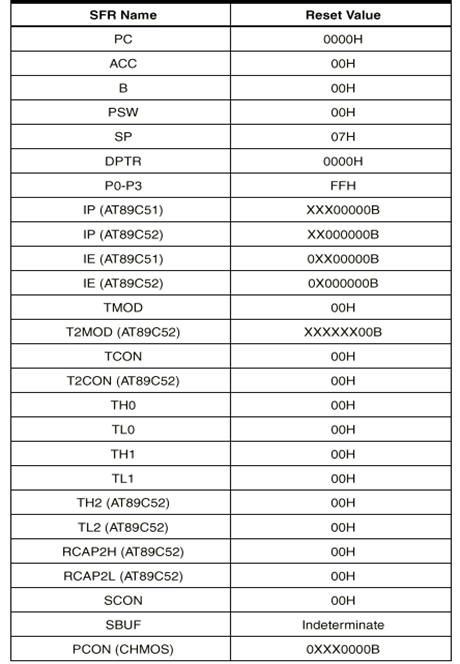

8. Reset la pornire (POWER-ON RESET)

Un reset automat se poate obtine atunci cand microcontrolerul este alimentat conectand pinul RST la +Vcc prin intermediul unui condensator de 10 uF si pinul Vss la pinul RST prin intermediul unui rezistor. Astfel, timpul de crestere pentru +Vcc pe pinul RST nu depaseste o milisecunda si timpul de pornire a oscilatorului nu depaseste 10 microsecunde (vezi figura 2.4).

Continutul registrilor cu functii speciale in urma reset-ului:

Fig. 2.4.Reset.

ALE/PROG (Address Latch Enable) furnizeaza impulsul de iesire pentru memorarea octetului celor mai putin semnificativi biti de adresa in accesului la memoria externa. ALE poate conduce pana la 8 intrari LS TTL. In operatii normale, ALE este generat la o rata constanta egala cu 1/6 din frecventa oscilatorului si poate fi folosit pentru temporizare sau ceas extern. De retinut insa ca un impuls ALE este omis in timpul fiecarui acces la memoria de date externa. Acest pin este de asemenea pin de intrare pentru impulsul de programare in timpul programarii EPROM-ului. Singura data cand un impuls ALE nu apare, este in timpul accesului la memoria de date externa: primul ALE din cel de-al doilea ciclu masina al unei instructiuni MOVX lipseste.

PSEN (Program Store Enable) este semnalul folosit pentru a valida citirea datelor din memoria program externa. Daca microcontrolerul acceseaza memoria program externa, PSEN este activat de doua ori in timpul unui ciclu masina, cu o exceptie: in timpul activarii de date externe.

EA/VPP (External Access Enable). Daca EA este in stare high, CPU ar trebui sa foloseasca memoria de program interna, dar avand in vedere ca microcontrolerul AT89C52 nu are memorie de program interna, pinul respectiv se leaga la masa. Astfel, EA tinut pe low forteaza unitatea centrala de prelucrare (CPU) sa foloseasca memoria program externa.

De asemenea acest pin permite utilizarea unei alimentari Vpp de 12V in timpul programarii FLASH, atunci cand este selectata programarea de 12V.

XTAL1 - Intrarea la inversorul oscilatorului si intrarea pentru ceasul intern de operare a circuitului.

XTAL2 - Iesirea de la inversorul oscilatorului.

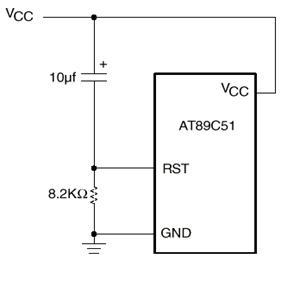

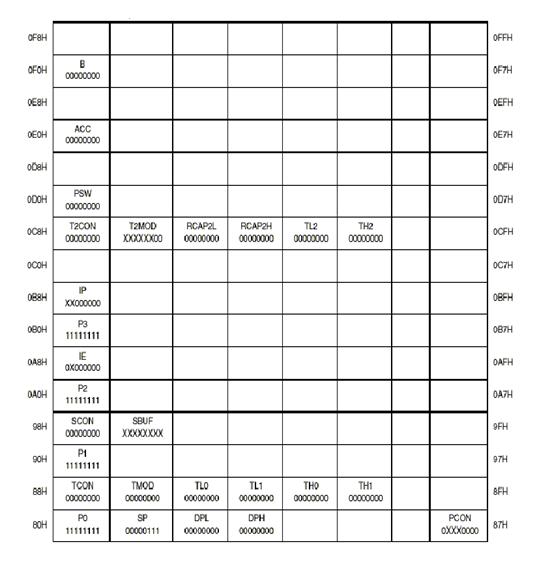

9. Registre cu functii speciale

O harta a zonei de memorie on-chip numita spatiu SFR (Special Function Register) este prezentata in figura de mai jos. SFR-urile marcate prin paranteze se regasesc in AT89C52 dar nu in AT89C51.

Tabel 4.2 Valorile la Reset

Nu toate adresele sunt ocupate. Adresele neocupate nu sunt implementate in cip. Accesul de citire pentru aceste adrese in general da date aleatore, iar accesul de scriere nu are efect.

Softul de utilizare nu trebuie sa scrie 1 logic in aceste locatii neimplementate deoarece ele pot fi folosite in microcontrolerele viitoare pentru facilitati noi. In acest caz, valorile inactive sau de reset ale noilor biti vor fi intotdeauna "0", iar valorile active vor fi "1".

Functiile SFR-urilor sunt prezentate in sectiunile urmatoare.

9.1. Acumulator

ACC este registrul Acumulator. Mnemonicile pentru instructiunile specifice Acumulator-ului, oricum, se refera la Acumulator printr-un simplu A.

9.2. Registrul B

Registrul B este folosit pe durata operatiilor de inmultire si impartire. Pentru altele el poate fi tratat cu un alt registru scratch pad.

9.3. PSW

Cuvant de stare al programului (Program Status Word) - registru ce contine informatii despre starea programului. Configuratia acestui registru este prezentata in tabelul de mai jos:

Cel mai semnificativ bit Cel mai putin semnificativ

MSB(Most significant bit) LSB(Less significant bit)

|

CY |

AC |

F0 |

RS1 |

RS0 |

0V |

-- |

P |

9.4. Registrul indicator de stiva SP(Stack pointer)

Registrul Stack Pointer are o marime de 8 biti. El este incrementat inainte ca datele sa fie salvate pe durata executiei instructiunilor PUSH si CALL. In timp ce stiva se poate regasi oriunde intr-un cip RAM indicatorul de stiva este initializat la 07H dupa reset. Aceasta determina stiva sa inceapa de la 08H.

9.5. Data Pointer (DPTR)

Data Pointer este format din octetul high (DPH) si octetul low (DPL). Functia sa este de a retine o adresa de 16 biti. El poate fi folosit ca un registru de 16 biti sau ca doi registrii de 8 biti.

9.6. Porturi

P0, P1, P2 si P3 sunt latch-urile pentru porturile 0, 1, 2 respectiv 3.

9.7. Buffer-ul de date serial

Buffer-ul de date serial este de fapt format din doua registre separate, un registru buffer de transmisie si un registru buffer de receptie. Atunci cand datele sunt mutate in SBUF (Serial Data Buffer), ele merg in buffer-ul de transmisie, unde sunt retinute pentru transmisia seriala. Mutarea unui octet in SBUF initiaza transmisia. Atunci cand datele sunt mutate din SBUF, ele vin din buffer-ul de receptie.

9.8. Registre temporizator/numaratoare (Timer/Counter registers)

Registrele pereche (TH0, TL0), (TH1, TL1) si (TH2, TL2) sunt numaratoare pe 16 biti pentru temporitator/numarator (Timer/Counter) 0, 1 si 2 .

9.9. Registre de captura

Perechea de registre (RCAP2H, RCAP2L) sunt registre de captura pentru modul captura 2 al circuitului de temporizare. In acest mod, ca raspuns la o tranzitie la pinul T2EX al AT89C52, TH2 si TL2 sunt copiati in RCAP2H si RCAP2L. Circuitul de temporizare 2 are de asemenea un mod de autoincarcare de 16 biti, iar RCAP2H si RCAP2L retin valoarea de autoincarcare pentru acest mod.

9.10. Registre de control

Registrele cu functii speciale IP, IE, TMOD, TCON, T2CON, T2MOD, SCON si PCON contin biti de control si de stare pentru sistemul de intreruperi, circuitele de temporizare/numaratoare si portul serial. Acestea sunt descrise in sectiunea urmatoare a acestui capitol.

Operarea si structura porturilor

Toate patru porturile din AT89C52 sunt bidirectionale. Fiecare este format dintr-un latch (registrele cu functii speciale de la P1 pana la P3), driver de iesire si un buffer.

Driverele de iesire ale porturilor 0 si 2 si buffer-ele de intrare ale portului 0 sunt folosite pentru accesarea memoriei externe. Portul 0 asigura iesirea octetului celui mai putin semnificativ al adresei de memorie externe. Portul 2 asigura iesirea octetului cel mai semnificativ al adresei de memorie externe atunci cand adresa are o lungime de 16 biti. Altfel, pinii portului 2 vor emite in continuare continutul lui P2 SFR.

Toti pinii portului 3 si 2 dintre pinii portului 1 (la AT89C52 ) sunt multifunctionali. Ei nu sunt doar pini de port, furnizand de asemenea servicii speciale prezentate in tabelul urmator:

|

Pin port |

Functii alternative |

|

P1.0 |

T2 intrare externa pentru circuitul de numarare/temporizare2 ) |

|

P1.1 |

T2EX |

|

P3.0 |

RXD ( port de intrare serial ) |

|

P3.1 |

TXD ( port de iesire serial ) |

|

P3.2 |

/INTO ( intreruperi externe ) |

|

P3.3 |

/INT1 ( intrare externe ) |

|

P3.4 |

T0 (intrare externa pentru circuitul de temporizare/numarare 0) |

|

P3.5 |

T1 (intrare externa pentru circuitul de temporizare/numarare 1) |

|

P3.6 |

/WR (scriere memorie de date externa) |

|

P3.7 |

/RD (citire memorie de date externa) |

Functiile alternative pot fi activate daca secventa de biti corespunzatoare din portul SFR contine un "1". Altfel pinul portului este blocat pe "0".

11. Scrierea intr-un port

Cand o instructiune schimba valoarea latch-ului unui port noua valoare soseste la latch pe durata S6P2 al ciclului final al instructiunii. Oricum latch-urile portului sunt esantionate cu ajutorul buffere-lor de iesire doar pe durata fazei 1 a oricarei perioade de tact. (Pe durata fazei 2 buffer-ul de iesire retin valorile esantionate pe durata fazei 1 anterioare). In mod consecvent, noua valoare din latch-ul portului nu apare la pinul de iesire inainte de urmatoarea faza 1, care este la S1P1 din urmatorul ciclu masina.

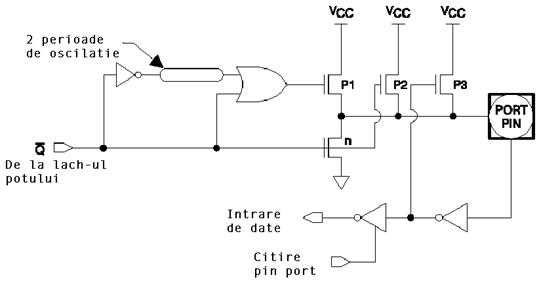

Daca schimbarea necesita o tranzitie de la 0 la 1 in porturile 1, 2 sau 3, o rezistenta de pull-up aditionala este activata pe durata S1P1 si S1P2 a ciclului in care se produce tranzitia pentru a mari viteza, rezistentele interne de pull-up sunt tranzistori cu efect de camp, nu rezistoare liniare. Aranjarea acestora este aratata in figura 2.5.

Fig. 2.5. Configurarea rezistentei de pullup interna pentru porturile 1 si 3

Rezistenta de pull-up este formata din trei pFET-uri. Un FET cu canal n (nFET) se activeaza cand un "1" logic se aplica la grila sa si este dezactivat cand un "0" logic se aplica la grila sa. Un FET cu canal p (pFET) este opusul lui nFET: se activeaza cand un "0" logic se aplica la grila sa si este dezactivat cand un "1" logic se aplica la grila sa.

Tranzistorul pFET1 din fig.2.4 este pornit pentru doua perioade ale oscilatorului dupa tranzitia de la "0" la "1" din latch-ul portului. In timp ce pFET1 este pornit el activeaza pFET3 prin inversor. Acest inversor impreuna cu pFET3 formeaza un latch care retine "1" logic.

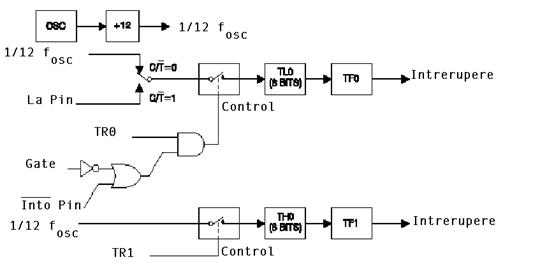

12. Circuite de numarare/temporizare

AT89C51 are doua registre de 16 biti de numarare/temporizare: Timer0 si Timer1. AT89C52 are aceste doua circuite de numarare/temporizare si in plus mai are Timer2. Toate trei pot fi configurate pentru a functiona direct ca circuite de temporizare sau eventual ca circuite de numarare.

Ca circuit de temporizare registrul este incrementat la fiecare ciclu masina. Astfel, registrul contorizeaza ciclurile masina. In timp ce un ciclu masina este format din 12 perioade de oscilatie, rata de numarare este de 1/12 din frecventa oscilatorului.

Ca numarator, registrul este incrementat la fiecare tranzitie de la "1" la "0" la pinul de intrare extern corespunzator: T0, T1 sau T2. Intrarea externa este esantionata pe durata S5P2 a fiecarui ciclu masina. Atunci cand esantioanele arata high intr-un ciclu si low in ciclul urmator numaratorul este incrementat. Noua valoare de numarare apare in registru pe durata S3P1 a ciclului urmator celui in care a fost detectata tranzitia. Deoarece sunt necesare doua cicluri masina (24 perioade de oscilatie) pentru a recunoaste o tranzitie de "l" la "0", rata de numarare este 1/24 din frecventa oscilatorului. In plus fata de functiile de numarare sau temporizare Timer0 si Timer1 au patru moduri de operare: temporizare pe 13 biti, temporizare pe 16 biti, autoincarcare pe 8 biti si temporizare distribuita.

13.Timer 0 si Timer 1

Circuitele de numarare/temporizare Timer0 si Timer1 sunt prezente si la AT89C51 si la AT89C52. Functia de numarare sau temporizare este selectata cu ajutorul bitilor de control C/-T din registrul cu functii speciale TMOD.

![]() TIMER1 TIMER0

TIMER1 TIMER0

|

GATE |

C/-T |

M1 |

M0 |

GATE |

C/-T |

M1 |

M0 |

TMOD |

Aceste doua circuite de numarare/temporizare au patru moduri de operare care pot fi selectate cu ajutorul perechilor de biti (M0, M1) din TMOD. Modurile 0, 1 si 2 sunt la fel pentru ambele circuite de numarare/temporizare, dar modul 3 este diferit. Cele patru moduri sunt descrise in continuare.

|

M1 |

M0 |

Nr. |

Modul de operare |

|

TIMER pe 13 biti |

|||

|

TIMER/COUNTER pe 16 biti |

|||

|

TIMER/COUNTER pe 8 biti in mod auto-reload |

|||

|

(TIMER1) TIMER /COUNTER1 oprit |

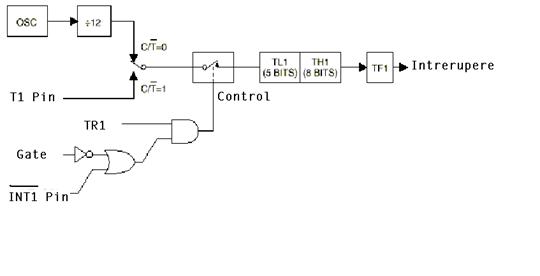

Modul 0 - Ambele circuite de temporizare in modul 0 au circuite de numarare pe 8 biti cu divizare cu 32. Figura 3 prezinta modul de operare 0 aplicat la circuitul Timer1. In acest mod registrul de temporizare este configurat ca un registru de 13 biti. Ca numararea sa se produca de la toti bitii 1 la toti bitii 0 se seteaza TF1, intrarea de numarare este validata de catre Timer atunci cand TR1=1 si GATE=0 sau /INT1=1. Setand GATE=1 permitem ca timer-ul sa fie controlat de catre intrare externa /INT1. TR1 este un bit de control in registrul cu functii speciale TCON (fig.2. ). GATE este in TMOD.

Registrii de 13 biti sunt formati din toti cei 8 biti ai lui TH1 si 5 cei mai putin semnificativi ai lui TL1. Primii 3 biti din TL1 sunt nedeterminati si pot fi ignorati. Setand TR1 nu se vor sterge registrii.

Modul 0 de operare este la fel pentru Timer1 si Timer0. Cu exceptia TL0, TF0 si /INT0 care inlocuiesc semnalele corespunzatoare Timer1 in figura 2. exista doi biti diferiti pentru GATE, punand unul pentru Timer1 (TMOD.7) si unul pentru Timer0 (TMOD.3).

Fig.2.6. Modul 0 al circuitului de numarare/temporizare

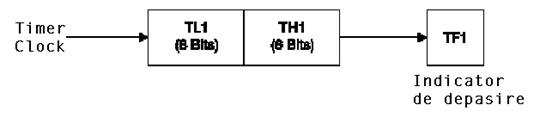

Modul 1 - este la fel ca si modul 0 exceptand faptul ca registrii circuitelor de temporizare ruleaza cu toti cei 16 biti. Semnalul de tact este aplicat registrilor de temporizare in combinati high si low (TL1/TH1). In timp ce impulsurile de tact sunt receptionate, timer-ul numara crescator: de la 0000H, 0001H, 0002H, etc. Se va inregistra o depasire de la FFFFH la 0000H in bitul indicator de depasire. Timer-ul va continua sa numere. Indicatorul de depasire este bitul TF1 din TCON care este citit sau scris prin soft.

Fig.2.7. Modul 1 al circuitului de numarare/temporizare

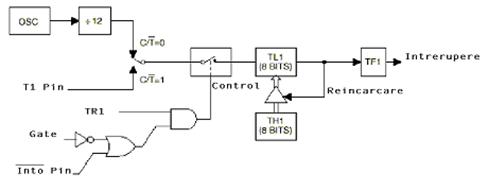

Modul 2 - configureaza registrul de temporizare ca un numarator pe 8 biti (TL1) cu reincarcare automata, dupa cum este prezentat in figura 2.8. Depasirea de la TL1 nu seteaza doar TF1, ci de asemenea reincarca TL1 cu continutul lui TH1, care este prezentat prin soft. Reincarcarea lasa TF1 neschimbat.

Fig.2.8. Modul 2 al circuitului de numarare/temporizare

Modul 3 - In modul 3, Timer1 doar retine rezultatul numararii. Efectul este la fel ca la setarea lui TR1=0.

In modul 3, Timer 0 stabileste TL0 si TH0 ca doua numaratoare separate. Logica pentru Timer0 functionand in modul 3 este prezentata in figura 2.10. TL0 foloseste bitii de control ai Timer0: , GATE, TR0, /INT0 si TF0. TH0 este blocat pentru o functie a circuitului de temporizare (numararea ciclurilor masina) si pentru folosirea lui TR1 si TF1 pentru Timer1. Astfel TH0 controleaza intreruperile Timer1.

Modul 3 este folosit pentru aplicatiile care necesita circuite de numarare sau temporizare mai mari de 8 biti. Cu Timer 0 in modul 3, AT89C51 poate aparea ca avand trei circuite de numarare/temporizare, iar AT89C52 poate aparea ca avand patru. Cand Timer 0 este in modul 3, Timer 1 poate fi oprit sau pornit prin comutarea in afara sau in interiorul propriului sau mod 3. In acest caz Timer1 poate fi in continuare folosit prin portul serial ca generator sau in orice aplicatie ce nu necesita intreruperi.

Fig.2.9. Modul 3 al circuitului de numarare/temporizare.

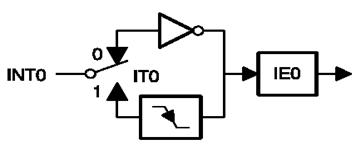

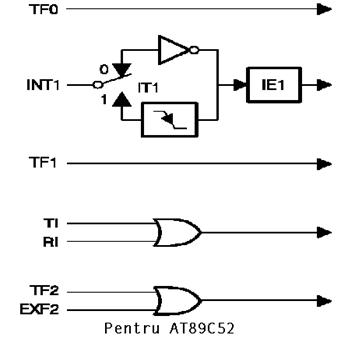

14. Intreruperile

Microcontrolerul AT89C52 are 6 surse de intreruperi prezentate in figura 2.11.

Fig.2.10. Intrerupere Interna 0

Fig.2.11. Sursele de intreruperi.

Intreruperile externe INT0 si INT1 pot fi activate prin nivel sau prin tranzitie depinzand de bitii IT0, IT1 din registrul TCON. Flag-urile care activizeaza aceste intreruperi sunt bitii IE0 si IE1 din TCON. Cand serviciul de rutina este activat, hard-ul sterge flag-ul care a generat o intrerupere externa numai daca intreruperea a fost activata prin tranzitie. Daca intreruperea a fost activata prin nivel atunci sursa externa ceruta controleaza flag-ul cerut. Intreruperile Timer 0 si Timer 1 sunt generate de TF0 si TF1, fiind produse de o depasire in respectivele registre de numarare/temporizare (cu exceptia lui T0 in mod 3). Cand o intrerupere de Timer este generata CIP-ul hard sterge flag-ul care a generat-o cand serviciul de rutina este activat.

15. Structura nivelelor de prioritate

Fiecare sursa de intrerupere poate fi programata si individual la unul din cele doua nivele de prioritate din setarea sau stergerea unui bit din registrul cu functii speciale IP (intrerupere prioritara) la adresa 0B8H. IP este initializat dupa o resetare a sistemului care plaseaza toate intreruperile la un nivel de prioritate mai scazut prin lipsa. O intrerupere cu nivel de prioritate scazut poate fi intrerupta printr-o intrerupere cu nivel de prioritate ridicat si nu printr-o alta intrerupere cu nivel de prioritate scazut. O intrerupere cu nivel de prioritate ridicat nu poate fi intrerupta prin nici o alta sursa de intrerupere [ 5 ]. Daca doua cereri de nivele de prioritate diferite sunt primite simultan este servita cererea nivelului mai ridicat de prioritate. Daca sunt primite cereri ale aceluiasi nivel de prioritate in mod simultan o secventa interna de polling arata care dintre cereri este indeplinita. Astfel in cadrul fiecarui nivel de prioritate exista o structura prioritara secundara determinata de secventa polling dupa cum urmeaza: Se observa ca structura "prioritatile din cadrul nivelului" este folosita numai pentru a rezolva cereri simultane ale aceluiasi nivel de prioritate.

Registrul IP contine un numar de biti neimplementati.

IP7 si IP6 sunt liberi la microcontrolerul AT89C52.

Tabel 9.2 Registrul pentru prioritatea intreruperilor

|

X |

X |

PT2 |

PS |

PT1 |

PX1 |

PT0 |

PX0 |

IP |

16. Intreruperi externe

Sursele externe pot fi programate sa fie activate prin nivel sau prin tranzitie prin setarea sau stergerea bitului IT0 sau IT1 din registrul TCON. Daca ITx=0 intreruperea externa X este declansata printr-o scadere detectata la pinul ITx. Daca ITx=1 intreruperea externa X este declansata. In acest fel daca esantioane succesive ale pinului /INTx arata o crestere intru-un ciclu si o scadere in urmatorul ciclu, intreruperea flag-ului cerut IEx din TCON este setata. Bitul flag-ului IEx cere in acest caz intreruperea.

Din moment ce pinii de intrerupere externa sunt prezenti odata pentru fiecare ciclu masina o intrare high sau low ar trebui sa tina cel putin 12 perioade oscilatoare pentru a asigura esantionarea. Daca intreruperea externa este activata prin tranzitie, sursa externa este activata prin tranzitie, sursa externa trebuie sa tina cresterea ceruta a pinului pentru cel putin un ciclu masina si apoi sa-i mentina scaderea pentru cel putin un ciclu masina pentru a ne asigura ca tranzitia este facuta incat flag-ul de intrerupere cerut IEx sa fie setat. IEx va fi in mod automat sters de catre CPU cand serviciul de rutina este chemat.

Daca intrerupere externa este activata prin nivel, sursa externa trebuie sa tina cererea activata pana cand intreruperea ceruta este generata. Atunci sursa externa trebuie sa dezactiveze cererea inainte ca intreruperea serviciului de rutina sa fie completa, astfel va fi generata o alta intrerupere.

17. Interfata seriala

Portul serial este de tip full-duplex, adica poate sa transmita si sa receptioneze. De asemenea, portul serial are partea de receptie cu registrul tampon (buffer), adica poate sa inceapa receptia celui de-al doilea octet inainte ca primul octet receptionat sa fie citit din registrul de receptie. Oricum, daca primul octet nu a fost citit pe durata receptiei celui de-al doilea octet, unul dintre octeti se va pierde.

Registrele de transmisie si de receptie ale portului serial sunt ambele accesate de catre registrul cu functii speciale SBUF (Serial Data Buffer). Scrierea in SBUF incarca registrul de transmisie, iar citirea lui SBUF acceseaza un registru de receptie separat fizic.

Portul serial poate opera in patru moduri:

Modul 0 : Datele transmise serial intra si ies prin RXD. TXD furnizeaza semnalul de ceas decalat (shift clock). Se transmit/receptioneaza 8 biti de date, incepand cu bitul cel mai putin semnificativ (LSB). Rata transferului de date (baud rate) este fixata la 1/12 din valoarea frecventei de oscilatie.

Modul 1 : Se transmit (prin TXD) sau se receptioneaza (prin RXD) 10 biti: un bit de start (0), 8 biti de date (incepand cu bitul cel mai putin semnificativ-LSB) si in final un bit de stop (1). La receptie bitul de stop se va duce in RB8, bit din registrul cu functie speciala SCON (Serial Port Control Register). Acest registru este in figura 2.11. Rata transferului de date este variabila.

Modul 2 : Se transmit (prin TXD) sau se receptioneaza (prin RXD), 11 biti: un bit de start (0), 8 biti de date (primul bit care intra este cel mai putin semnificativ-LSB), un al 9-lea bit de date care este programabil si un bit de stop (1). La transmisie, cel de-al 9-lea bit de date (TB8 din registrul SCON) poate fi incarcat la valoarea "0" logic, sau la valoarea "1" logic, sau se poate incarca in TB8 bitul de paritate P din registrul cu functie speciala PSW (Program Status Word). La receptie, cel de-al 9-lea bit de date este plasat in RB din registrul cu functie speciala SCON, iar bitul de stop este ignorat. Rata transferului de date este programabila, ea putand fi 1/32 sau 1/64 din frecventa oscilatorului.

Modul 3 : Se transmit (prin TXD) sau se receptioneaza (prin RXD) 11 biti: un bit de start (0), 8 biti de date, un al 9-lea bit de date programabil si un bit de stop (1). De fapt, modul 3 este similar modului 2, singura exceptie fiind ca rata transferului de date este valida in modul 2.

In toate cele patru moduri de operare, transmisia este initiata de orice instructiune care foloseste registrul SBUF ca registru de destinatie. Receptia este initiata diferit pentru modul 0 si pentru celelalte trei moduri de operare.

In modul 0, receptia este initiata de conditiile RI=0 si REN=1 (REN este bitul care activeaza, atunci cand este setat receptia seriala, iar RI este bitul de receptie intrerupere).

17.1. Registrul de control al portului serial

Registrul de control si stare al portului serial (Serial Port Control Register) este registrul cu functie speciala SCON prezentat in tabelul 11.2.

Acest registru contine bitii pentru selectia modului de operare, cel de-al 9-lea bit de date transmis sau receptionat (TB8 si RB8) si bitii de intrerupere ai portului serial (TI si RI), a caror descriere se face in continuare.

Tabel 10.2. Registrul de control al portului serial SCON

|

SM0 |

SM1 |

SM2 |

REN |

TB8 |

RB8 |

TI |

RI |

Semnificatia bitilor registrului SCON este urmatoarea:

|

Simbol |

Pozitie |

Functie |

|

|

SM0 |

SCON.7 |

Specificator al modului de operare al portului serial |

|

|

SM0 |

SCON.6 |

Specificator al modului de operare al portului serial |

|

|

SM2 |

SCON.5 |

Activeaza posibilitatea de comunicare multiprocesor in modurile 2 si 3 .In modul 2 sau in modul 3, daca SM2 este setat, atunci RI nu va fi activat, daca al 9-lea bit de date receptionat RB8, este 0. In modul 1, daca SM2=1 atunci RI nu va fi activat daca nu a fost receptionat un bit valid de stop. In modul 0, SM2 trebuie sa fie 0. |

|

|

REN |

SCON.4 |

Setare/Stergere (SET/Cleared) prin software pentru a activa/dezactiva receptia. |

|

|

TB8 |

SCON.3 |

Al 9-lea bit de date ce va fi transmis in modurile de operare 2 si 3 ale portului serial |

|

|

RB8 |

SCON.2 |

Al 9-lea bit de date ce va fi receptionat in modurile de operare 2 si 3 ale portului serial. In modul 1, daca SM2=0, RB8 este bitul de stop care a fost receptionat. In modul 0, RB8 nu este folosit. |

|

|

TI |

SCON.1 |

Indicatorul (Flag) de intrerupere a transmisiei. Este setat prin hardware: in modul 0 la sfarsitul timpului de transmisie a celor 8 biti de date, in celelalte moduri de operare la inceputul bitului de stop. Acest bit trebuie resetat prin software. |

|

|

RI |

SCON.0 |

Indicatorul (Flag) de intrerupere receptiei. Setat prin hardware: in modul 0, la sfarsitul timpului de transmisie a celor 8 biti de date, in celelalte moduri la jumatatea timpului de transmisie a bitului de stop. Acest bit trebuie resetat prin software. |

|

|

SM0 |

SM1 |

Modul |

Descriere |

Rata transferului de date (Baud Rate) |

|

Registru de deplasare (shift register) |

Fosc/12 |

|||

|

8-bit URT |

Variabila |

|||

|

9-bit URT |

Fosc./64 sau Fosc./32 |

|||

|

9-bit URT |

Variabila |

17.2. Registrul de Control al Timer/Counter-elor 0 si 1

|

TF1 |

TR1 |

TF0 |

TR0 |

IE1 |

IT1 |

IE0 |

IT0 |

TCON |

Tabel 14.2

|

Simbol |

Pozitie |

Functie |

|

TF1 |

TCON.7 |

Indicator depasire al Timer-ului 1. Este setat prin hardware la depasire pe temporizator/numarator. Este resetat prin hardware cand procesorul apeleaza rutina de intrerupere |

|

TR1 |

TCON.6 |

Bitul de control al functionarii Timer-ului 1. Este setat/resetat prin software pentru a porni/opri temporizatorul/numaratorul. |

|

TF0 |

TCON.5 |

Indicator depasire Timer 0. Este setat prin hardware la depasire pe temporizator/numarator. Este resetat prin hardware cand procesorul apeleaza rutina de intrerupere. |

|

TR0 |

TCON.4 |

Bit de control al functionarii Timer 0. Este setat/resetat prin software pentru a porni/opri temporizatorul/numaratorul |

|

IE1 |

TCON.3 |

Indicator de activare a intreruperii 1 pe front. Setat prin hardware cand se detecteaza un front negativ. |

|

IT1 |

TCON.2 |

Bit de control al modului de activare a intreruperii 1. |

|

IE0 |

TCON.1 |

Indicator de activare a intreruperii 0 pe front. Setat prin hardware cand se detecteaza un front negativ. |

|

IT0 |

TCON.0 |

Bit de control al modului de activare a intreruperii 0 |

17.3. TIMER 2

Registrul Timer 2 este Timer/Counter pe 16 biti si poate fi configurat sa lucreze ca Timer sau Counter cu ajutorul bitului C/-T2 din registrul cu functii speciale T2CON (Timer/Counter 2 Control Register) prezentat in figura urmatoare. Pentru C/-T2=0 Timer 2 este in functionare Timer, iar pentru C/-T2=0 este in functionare Counter.

17.4 Registrul de control al Timer/Counter-ului 2 (T2CON)

Tabel 15.2

|

Simbol |

Pozitie |

Functie |

|

TF2 |

T2CON.7 |

Indicator depasire Timer 2. Este setat cand apare o depasire in Timer 2si trebuie sters prin software. TF2 nu va fi setat cand cel putin unul dintre bitii RCLK sau TCLK este 1. |

|

EXF2 |

T2CON.6 |

Bit indicator al aparitiei unui eveniment la pinii de control al Timer 2. |

|

RCLK |

T2CON.5 |

Bit indicator al ceasului de receptie pentru portul serial. |

|

TCLK |

T2CON.4 |

Bit indicator al ceasului de transmisie pentru portul serial. |

|

EXEN2 |

T2CON.3 |

Indicator de activare externa al Timer 2 |

|

TR2 |

T2CON.2 |

Porneste/Opreste Timer 2. Un "1" logic porneste timer-ul. |

|

C/-T2 |

T2CON.1 |

Selecteaza functionarea Timer 2 ca Timer sau Counter. C/-T2=0 Timer intern cu frecventa egala cu 1/12 din frecventa oscilatorului. C/-T2=1 numarator al evenimentelor externe pe front negativ. |

|

CP/RL2 |

T2CON.0 |

Indicator pentru memorare/incarcare. Cand este setat, memorarea va avea loc la o tranzitie negativa pe pinul T2X daca EXEN2=1. |

Semnificatia bitilor registrului cu functii speciale T2CON este urmatoarea:

|

Simbol |

Pozitie |

Functie |

|

TF2 |

T2CON.7 |

Indicator depasire Timer 2. Este setat cand apare o depasire in Timer 2si trebuie sters prin software. TF2 nu va fi setat cand cel putin unul dintre bitii RCLK sau TCLK este 1. |

|

EXF2 |

T2CON.6 |

Bit indicator al aparitiei unui eveniment la pinii de control al Timer 2. |

|

RCLK |

T2CON.5 |

Bit indicator al ceasului de receptie pentru portul serial. |

|

TCLK |

T2CON.4 |

Bit indicator al ceasului de transmisie pentru portul serial. |

|

EXEN2 |

T2CON.3 |

Indicator de activare externa al Timer 2 |

|

TR2 |

T2CON.2 |

Porneste/Opreste Timer 2. Un "1" logic porneste timer-ul. |

|

C/-T2 |

T2CON.1 |

Selecteaza functionarea Timer 2 ca Timer sau Counter. C/-T2=0 Timer intern cu frecventa egala cu 1/12 din frecventa oscilatorului. C/-T2=1 numarator al evenimentelor externe pe front negativ. |

|

CP/RL2 |

T2CON.0 |

Indicator pentru memorare/incarcare. Cand este setat, memorarea va avea loc la o tranzitie negativa pe pinul T2X daca EXEN2=1. |

In plus Timer 2 are trei moduri de operare care sunt prezentate in tabelul de mai jos:

|

RCLK+TCLK |

CP/-RL2 |

TR2 |

Modul de operare |

|

Auto-reincarcare pe 16 biti. |

|||

|

Memorare pe 16 biti. |

|||

|

X |

Generator de rata a transferului de date. |

||

|

X |

X |

Off. |

18. Rata transferului de date ( BAUD RATE )

Rata transferului de date reprezinta numarul de biti transmisi pe secunda si uneori ea coincide cu rata de transmisie. Pentru fiecare din cele 4 moduri de operare ale portului serial, baud rate se calculeaza separat, astfel:

Timer-ul poate fi configurat sa lucreze ca Timer sau Counter. In majoritatea aplicatiilor este configurat pentru operare Timer (prin punerea C/-T2=0). Operarea ca Timer este diferita pentru Timer 2 cand este folosit ca generator de rata a transferului de date si anume: normal, ca Timer el va incrementa la fiecare ciclu masina (aceasta se face la 1/12 din frecventa oscilatorului de ceas), in timp ce ca generator de rata a transferului de date, va incrementa la fiecare stare (aceasta se face la 1/2 din frecventa oscilatorului). In acest caz rata transferului de date se va calcula cu formula:

Rata transferului de date in Mod1 si Mod3 = Frecventa oscilatorului/32x [65536-(RCAP2H, RCAP2L)];

-unde (RCAP2H, RCAP2L) reprezinta continutul lui RCAP2H si RCP2L luate ca un intreg fara semn, de 16 biti.

In modul 2 de lucru rata de transfer depinde de valoarea depinde de valoarea bitului SMOD din registrul de control al alimentarii PCON.

Formula pentru calculul ratei transferului de date in acest mod este: Rata transferului de date Mod x Frecventa oscilatorului.

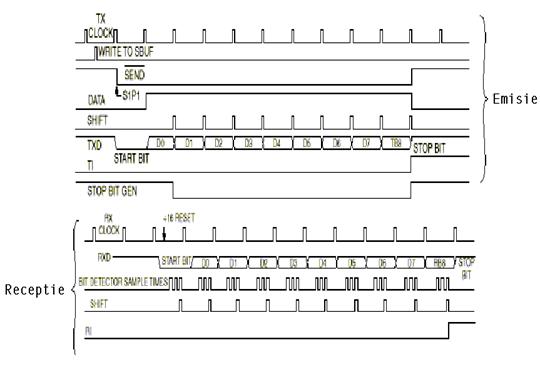

19. Modul 1 de operare al portului serial

In acest mod de operare se transmit (prin pinul TXD) si se receptioneaza (prin pinul RXD) un cadru alcatuit din 10 biti: 1 bit de start (0) (in repaus linia sta in "1" logic, deci frontul negativ va indica inceputul), 8 biti de date (se transmite / receptioneaza mai intai cel mai putin semnificativ bit LSB) si 1 bit de stop (1). La receptie bitul de stop merge in RB8 din registrul cu functie speciala SCON.

Fig.2.12. Diagramele de timp ale functionarii portului serial in modul 1.

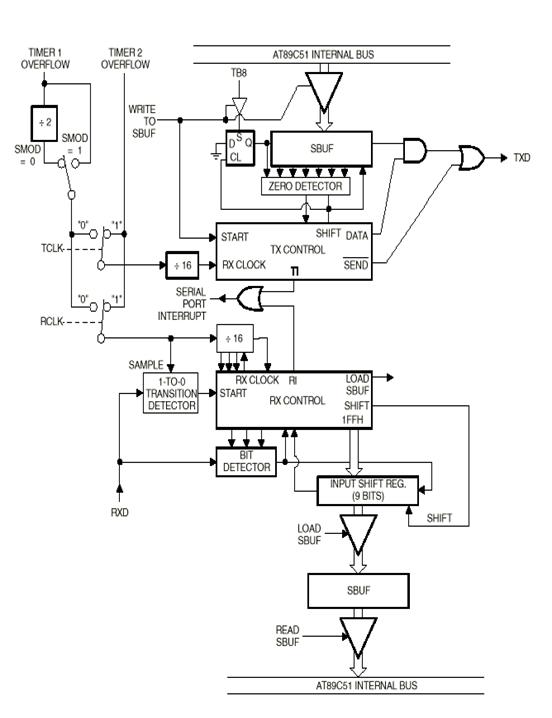

Fig.2.13. Schema bloc a portului serial (modul 1).

In figura 2.13 este prezentata o diagrama functionala simplificata a portului serial in modul 1 de operare, iar figura 2.12 prezinta diagramele de timp pentru timpii asociati transmisiei si receptiei.

Transmisia este initiata de orice instructiune care foloseste registrul cu functie speciala ca registru destinatie. Semnalul scrie in SBUF (write to SBUF) va incarca un "1" in pozitia a 9-a din registrul de deplasare de transmisie si anunta unitatea de control a transmisiei, TX Control, ca este ceruta o transmisie. Transmisia incepe in S1P1 al ciclului masina care urmeaza dupa ce a aparut o depasire in numaratorul "divide-cu-16". Astfel timpii pentru bit sunt sincronizati cu numaratorul "divide-cu-16", care stabileste rata transferului de date si nu cu semnalul write to SBUF

Transmisia va incepe cu activarea lui SEND, care pune bitul de start pe TXD. Dupa o perioada egala cu durata deplasarii unui bit prin registru, este activat registrul Data care permite iesirea bitului din registrul de deplasare pentru transmisie, spre TXD. Primul impuls de deplasare apare dupa o perioada egala cu durata deplasarii unui bit. Pe masura ce bitii de date ies spre dreapta din registrul de deplasare, in stanga se introduc zero-uri. Aceasta conditie anunta unitatea TX Control ca trebuie sa faca o ultima deplasare si dupa aceea sa dezactiveze SEND sa seteze TI (sa lanseze o intrerupere). Aceasta se intampla dupa al 10-lea tact de transmisie dat de numaratorul divizor cu 16 dupa semnalul write to SBUF.

Receptia este initiata de detectarea unei tranzitii din 1 in 0, pe pinul RXD. In acest scop RXD este esantionat la perioade egale cu timpul de tranzitie al unui bit, indiferent de valoarea la care este fixata rata transferului de date. Cand se detecteaza o tranzitie, numaratorul divide-cu-16 este imediat resetat si se scrie 1FFH in registrul de deplasare de intrare.

Resetarea numaratorului se face pentru sincronizarea ceasului propriu al procesorului si a semnalului receptionat.

Cele 16 stari ale numaratorului impart timpul de tranzitie al unui bit la 13. Pentru fiecare bit in parte, la starile 7, 8 si 9 ale numaratorului, detectorul de bit va face esantionarea valorii de la RXD. Valoarea este acceptata doar daca ea a fost vazuta cel putin in doua din cele trei esantionari. Acest lucru se face pentru rejectarea zgomotului.

Daca valoarea acceptata pentru primul bit nu este 0, circuitele de receptie sunt resetat si unitatea incepe din nou sa caute o tranzitie din 1 in 0. Acest lucru se face pentru a elimina bitii de start falsi. Daca bitul de start se dovedeste a fi valid, el este deplasat in registrul de deplasare de intrare si urmeaza apoi receptia in continuare a cadrului (10 biti: 1 bit de start, 8 biti de date si 1 bit de stop).

Bitii de date vin din dreapta si sunt deplasati spre stanga. Cand bitul de start ajunge la ultima pozitie din stanga in registrul de deplasare, anunta blocul de control RX Control, si seteaza RI(lanseaza o intrerupere). Semnalul pentru incarcarea lui SBUF si RB8 si setarea lui RI va fi generat, daca si numai daca, urmatoarele doua conditii sunt indeplinite simultan in momentul generarii ultimului impuls de deplasare:

RI = 0 si SM2 = 0 sau bitul de stop receptionat =1. Daca oricare din aceste doua conditii sunt este indeplinita, cadrul receptionat este iremediabil pierdut. Daca ambele conditii sunt indeplinite, bitul de stop se duce in RB8, cei 8 biti de date se duc in SBUF si RI este activat. In acest moment, indiferent daca cele doua conditii sunt indeplinite sau nu, unitatea incepe din nou sa astepte o tranzitie din 1 in 0.

|

Politica de confidentialitate |

| Copyright ©

2026 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |