Scazatoare paralele pe principiul propagarii seriale a transportului

Dominant, operatia de scadere binara se efectueaza utilizand un sumator care permite adunarea la descazut (minued) a scazatorului (subtrahend) negat in mod corespunzator. Astfel, in reprezentare semn-marime (sign-magnitudine), scaderea implica inversarea bitului de semn al scazatorului succedata de adunarea acestuia. In complement de unu (one's complement), se realizeaza inversarea fiecarei bit al scazatorului si apoi adunarea acestui vector binar la descazut. Cea mai raspandita implementare a scaderii corespunde hend-ul este complementat de unu si apoi adunat la minuend impreuna cu o unitate binara care trebuie si ea adunata la rangul cu mai putin semnificativ. In vederea implementarii se apeleaza la un sumator binar paralel, indiferent de tipul acestuia, la par se aplica minuend-ul Y precum si subtrahend-ul X in urma trecerii acestuia printr-un strat de porti EXCLUSIVE-OR, pe toata lungimea cuvantului (EX-OR wordgate), asa cum se arata in fig.2.17. Pentru adunarea unitatii binare la rangul cel mai putin semnificativ se profita de intrarea de carry-in (cin), ramasa disponibila, la care se aplica variabila s (de la 'subtract', care comanda, de asemenea, o intrare a tuturor portilor EXCLUSIVE-OR wordgate-ului. Variabila s comandata de cond configureaza sumatorul paralel ca scazator (X-Y), atunci cand s=1; lasand nemodificata functia sa (X+Y) atunci cand s = 1, lasand nemodificata functia sa (Y + X) atunci cand s = 0.

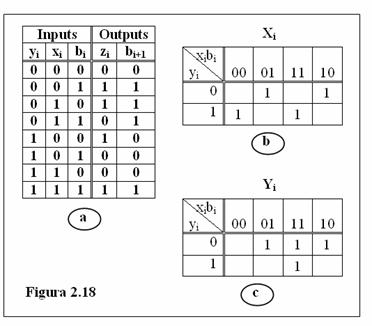

Exista insa cazuri, si structura matriciala combinationala de inmultire bazata pe recodificari Booth din paragraful 3.9 (vezi fig.3) reprezinta un astfel de exemplu, la care mai pot fi adaugate si structuri matriciale combinationale dedicate operatiei de impartire binara [Omon 94], cand este util a asigura o scadere verita ca o operatie separata, executata de catre un dispozitiv de sine statator denumit scazator binar (binary subtractor). Elementul de structura fundamental al unui astfel de dispozitiv este prin analogie cu celula sumator complet (full adder cell, FAC) a unui sumator binar RCA, o celula scazator complet (full subtractor cell, FSC). Proiectarea logica a unei FSS are la baza descrierea comportamentala prin tabelul de adevar din fig.2.18a, elaborat pentru un rang oarecare, al unui dispozitiv care realizeaza scaderea, fara semn a subtrahend-ului X din minuend-ul Y. In calitate de intrari avem variabile yi si xi, precum si imprumutul intrare (borrow-in), bi, cerut de rangul anterior (i-1), iar iesirile le reprezinta variabila diferentiala, zi, precum si imprumutl iesire (borrow-out), bi+1, revendicat de la rangul urmator (i+1). La completarea valorilor logice pentru iesirile zi si bi+1, din tabelul de adevar (fig.2.18a), s-a procedat la adunarea valorilor corespunzatoare variabilelor zi si bi, iar suma rezultata este scazuta din valoarea lui yi . Astfel spre exemplu, corespunzator tripletei (xi, yi, zi) = 010, avem xi+bi = 1+0 =1, care scazut din yi = 0 conduce la bitul diferenta zi = 1. Pentru elaborarea ecuatiilor booleene corespunzatoare functiilor booleene de iesire ale FSS, s-a apelat la diagrame Karnaugh reprezentata in fig.2.18b pentru zi, respectiv in fig.2.18c pentru bi+1.

Este de remarcat faptul ca expresia

booleana pentru iesirea diferenta zi

rezulta a fi data de

aceeasi functie de paritate impara zi = xi

+ yi +bi corespunzatoare iesirii suma zi

a unui FAC, cu mentiunea substituirii variabilei transport ci

cu variabila imprumut bi. De acest aspect se profita atunci

cand apare necesitatea (vezi schema matriciala combinationala

din fig.3.47) de a reconfigura un FAC intr-un FSC. Pe de alta parte, acoperirea unitatilor binare din

fig.2.18c conduce pentru bi+1, la o expresie asemanatoare

cu cea pentru transportul inspre rangul urmator, ci+1, anume ![]() .

.

De asemenea, pentru sinteza functiei imprumut bi+1 mai poate fi folosita si expresia :

![]()

In baza ecuatiei booleene pentru zi si bi+1 rezulta sinteza FSC care poate fi utilizata la configurarea, de scazatoare binara, una dintre solutii fiind, spre exemplu, inlantuirea in cascada a FSC-urilor in maniera RCA. Mai remarcam ca rezultatul unei scaderi poate fi negativ chiar si cand minuend-ul este pozitiv, situatie in care va fi imprumut pentru rangul cel mai semnificativ dintr-un ipotetic al 2-lea rang.

In final, sa ne

referim la scaderea operanzilor reprezentati in cod BCD8421. Prin

analogie cu operatia efectuata cu numere binare prin adunarea la

minuend a complementului de doi corespunzator subtrahend-ului, in acest

caz se va apela tot la o adunare, dar complementul de unu este substituit prin

mai costisitorul, in ceea ce priveste generarea, complement de noua

la care se adauga o unitate binara (ca si in cazul

complementului de doi). Astfel, in fig 2.19 se prezinta scaderea numerelor

adunate in fig 2.13 si fig 2.16. scaderea din minuend-a Y=473510 a subtrahend-ului X=291810 se efectueaza adunand la Y

complementul de noua al lui X, anume ![]() =708110 ,

si inca o unitate.

=708110 ,

si inca o unitate.

Operatia de adunare

se realizeaza in maniera

descrisa la exemplul din fig. 2.13, cu aplicarea selectiva a

corectiei de 0110. Implementarea adunarii poate fi realizata prin sumatorul din

fig. 2.14, detaliat in fig. 2.15. Cifra zecimala transport c*out,

in cazul nostru c*out = 1, se impune ignorata

dupa modelul operarii in binar. Ar mai ramane in discutie

implementarea complementarii de noua, care trebuie realizata

pentru fiecare cifra zecimala in parte. Se poate folosi in acest sens

cate un adder/subtracter pe 4 biti sau un translator de cod sintetizat pe

baza tabelului de adevar din fig. 2.2 prezentat pentru o cifra

zecimala Xi a subtrahend-ului. Sinteza translatorului se

efectueaza fara dificultate, rezultand ecuatiile booleene

pentru cifrele binare corespunzatoare complementului de noua ale

cifrei zecimale, spre exemplu ![]() Implementarea

unui astfel de translator se realizeaza simplu, necesitand trei porti

logice, cate una de tipul NOR, EXCLUSIVE OR si NOT.

Implementarea

unui astfel de translator se realizeaza simplu, necesitand trei porti

logice, cate una de tipul NOR, EXCLUSIVE OR si NOT.

|

Politica de confidentialitate |

| Copyright ©

2025 - Toate drepturile rezervate. Toate documentele au caracter informativ cu scop educational. |

Personaje din literatura |

| Baltagul caracterizarea personajelor |

| Caracterizare Alexandru Lapusneanul |

| Caracterizarea lui Gavilescu |

| Caracterizarea personajelor negative din basmul |

Tehnica si mecanica |

| Cuplaje - definitii. notatii. exemple. repere istorice. |

| Actionare macara |

| Reprezentarea si cotarea filetelor |

Geografie |

| Turismul pe terra |

| Vulcanii Și mediul |

| Padurile pe terra si industrializarea lemnului |

| Termeni si conditii |

| Contact |

| Creeaza si tu |